# Comprehensive Evaluation of Bias Temperature Instabilities on 4H-SiC MOSFETs Using Device Preconditioning

Submitted: 2017-09-08

Revised: 2018-01-25

Accepted: 2018-02-05 Online: 2018-06-05

Gerald Rescher<sup>1,a\*</sup>, Gregor Pobegen<sup>1,b</sup>, Thomas Aichinger<sup>2,c</sup> and Tibor Grasser<sup>3,d</sup>

<sup>1</sup>KAI GmbH, Europastraße 8, 9524 Villach, Austria

<sup>2</sup>Infineon Austria AG, Siemensstraße 2, 9500 Villach

<sup>3</sup>Vienna University of Technology, Gußhausstraße 27-29 / E360, 1040 Wien, Austria

<sup>a</sup>gerald.rescher@k-ai.at, <sup>b</sup>gregor.pobegen@k-ai.at, <sup>c</sup>thomas.aichinger@infineon.com,

<sup>d</sup>grasser@iue.tuwien.ac.at

**Keywords:** 4H-SiC, MOSFET, bias temperature instability, threshold voltage shift, preconditioning, delay time.

**Abstract.** In comparison to silicon based devices, MOSFETs based on silicon carbide show more complex threshold voltage variations due to positive and negative gate bias stress. We show that the majority of the voltage shift in standard JEDEC-like bias temperature instability measurements originates from stress independent measurement parameters like timing and switching conditions. A more sophisticated bias temperature instability measurement technique using device preconditioning is presented allowing for more accurate and nearly delay time independent extraction of the permanent voltage shift component within typical industrial timescales.

#### Introduction

In SiC devices, bias temperature instability (BTI) is caused by charge capture/emission at or near the SiC/SiO<sub>2</sub> interface during (high temperature) gate stress  $V_G^{\rm str}$ . Depending on the polarity of  $V_G^{\rm str}$ , BTI results in a positive (electron capture) or negative (hole capture) shift of the threshold voltage  $V_{\rm th}$ . A large positive  $V_G^{\rm str}$  causes a positive threshold voltage shift  $\Delta V$  and therefore reduces the overdrive in the on-state leading to increased on-resistance  $R_{\rm on}$  and static losses [1,2].

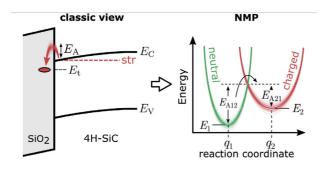

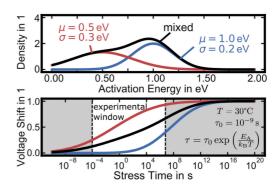

A simplified classic model of the charge trapping mechanism during BTI is shown in Fig. 1 (left) assuming a single trap state near the SiC/SiO<sub>2</sub> interface at the energetic position  $E_{\rm t}$ . At a fixed Fermi-level position  $E_{\rm F}$  (e.g. during bias stress), the activation energy  $E_{\rm A}$  of the trap state to change its occupancy is assumed to be normally distributed. Previous work on Si/SiO2 interfaces has shown that it is mandatory to consider the correct picture is given by the non-radiative multi-phonon (NMP) model (Fig. 1, right), which also accounts for atomic deformation of the defect subsequent to charge capture and the electric field dependence for both, capture and emission times [3, 4]. The activation energy for the reverse transition from the charged to the neutral state is therefore given by  $E_{\rm A21}$ . Assuming a distributed  $E_{\rm A}$ , the capture/emission process is also distributed in time according to the characteristic capture/emission time constant  $\tau = \tau_0 \exp(E_{\rm A}/k_{\rm B}T)$  with the Boltzmann constant  $k_{\rm B}$ , the temperature T and the pre-exponential factor  $\tau_0$ . An example of the impact of distributed  $E_{\rm A}$  on  $\Delta V$  is given in Fig. 2. In real devices, a large variation of defects with characteristic energy barriers will contribute to the overall voltage shift leading to a mix-up of the individual  $\Delta V$  over time behavior (Fig. 2, dashed line) [5]. For broadly distributed  $E_{\rm A}$ ,  $\Delta V$  approaches the often used, but unphysical power-law approximation

$$\Delta V = A \cdot t^k \tag{1}$$

with the pre-factor A and the power-law factor k. Instead of using Eq. 1, a more physical way to describe  $\Delta V$  during bias stress (assuming normally distributed  $E_A$ ) is given by [5]

$$\Delta V(t_{\rm str}) = \frac{\Delta V^{\rm max}}{2} \cdot \operatorname{erfc}\left(-\frac{k_{\rm B}T \ln(\frac{t_{\rm str}}{\tau_0}) - \mu}{\sqrt{2}\sigma}\right) \tag{2}$$

Fig. 1. Left: classic view of trapping mechanism with trap level  $E_{\rm t}$  and distributed  $E_{\rm A}$ . Right: Non-radiative multi-phonon (NMP) interpretation with distributed activation energies for capture  $E_{\rm A12}$  and emission  $E_{\rm A21}$ .

Fig. 2. Simulated impact of distributed activation energies (top) on the observed voltage shift during bias stress (bottom) according to Eq. 1. The dashed line represents a mix of the distributions  $\mu = 0.5$  eV and  $\mu = 1.0$  eV leading to a broadly distributed stress behavior.

with the complimentary error function erfc, the stress time  $t_{\rm str}$ , the maximum voltage shift  $\Delta V^{\rm max}$  and the parameters of the normal distribution  $\mu$  and  $\sigma$ .  $\Delta V$  recovery also scales with  $\log(t)$  resulting in a crucial dependence on timing parameters. Due to these facts, we present a preconditioned measurement method which minimizes the impact of delay and recovery times on the extracted  $\Delta V$ .

# **Experimental Setup**

All devices were fabricated on 4H-SiC n-doped substrates using an industrial process. The n-channel MOSFETs received a SiO<sub>2</sub> dielectric on the (11 $\overline{2}$ 0)-plane deposited via chemical vapor deposition. Post oxidation anneal was done in a nitric oxide containing atmosphere for all samples. Measurements are performed on wafer level using an Agilent B1500A parameter analyzer and Agilent E5250A switching matrix at room temperature unless otherwise stated.

# **Results and Discussion**

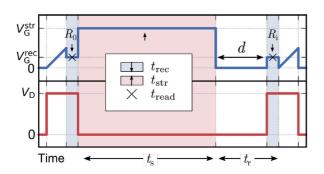

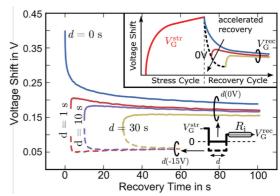

The consequences of measurement delay times. Fig. 3 shows a typical delayed JEDEC-like measurement pattern (JEDd) used in industrial BTI measurements. The pattern consists of a gate voltage  $V_G$  sweep for the subsequent calculation of  $\Delta V$ , a reference readout  $R_0$  at the readout voltage  $V_{\rm G}^{\rm rec}$ , a stress cycle at the stress voltage  $V_{\rm G}^{\rm str}$  for the stress time  $t_{\rm str}$ , a delay cycle at  $V_{\rm G}=0$  V for the delay time d and a readout  $R_i$  at the readout voltage  $V_{\rm G}^{\rm rec}$  for the recovery time  $t_{\rm rec}$ . Especially in industrial BTI measurements, delay times of 1 to 10 h between the end of the stress and  $R_i$  are always present since the stress cycle is usually done in high-temperature furnaces to accelerate degradation, whereas the readouts are done at room temperature outside the furnace in series for multiple devices. The impact of d on  $\Delta V$  is shown in Fig. 4 for multiple devices subjected to identical positive stress according to JEDd. Delay time varies from 0 s to 30 s. We observe decreasing  $\Delta V$  for increasing delay times. The explanation for the increased recovery is shown in the inset of Fig. 4. During the stress cycle,  $\Delta V$  increases with  $t_{\rm str}$  according to Eq. 2 (inset, red). By directly switching to  $V_G^{\text{rec}}$  without any delay (d = 0 s),  $\Delta V$  follows the blue recovery curve. Introducing a delay at  $V_{\rm G} = 0$  V results in increased recovery (inset, dashed black) because recovery depends on the Fermi level position. A subsequent bias change back to  $V_{\rm G}^{\rm rec}$  leads to a superposition of charge capture at  $V_{\rm G}^{\rm rec}$  (rising edge) and ongoing recovery. As can be seen, the delayed recovery curve ends up at less  $\Delta V$  than the non-delayed trace. This increased recovery effect scales with delay time showing that the delay phase at 0 V clears a fraction of the recoverable  $\Delta V$  component. The clearing characteristic of the delay pulse increases by using an accumulation pulse instead of just 0 V (dashed lines). In

Fig. 3. JEDEC-like bias temperature instability measurement with delay d between stress cycle and  $\Delta V_{\text{th}}$  readout  $R_{\text{i}}$ .

Fig. 4. Impact of the delay on  $\Delta V_{\rm th}$  recovery behavior for varying d at  $V_{\rm G}=0$  V (solid lines) and  $V_{\rm G}=-15$  V (dashed lines).

Fig. 4 an accumulation clearing pulse of -15 V was used for the same range of delay times resulting in a decrease of  $\Delta V$  from 175 mV to 60 mV after 60 s.

**Preconditioned BTI.** As shown in Fig. 4, JEDEC-like BTI measurements show varying recovery curves depending on the exact bias and timing conditions of each  $\Delta V$  readout for identical bias stress. This is due to two essential facts: First, extracted  $\Delta V$  depends on the reference readout  $R_0$  timing and preceding gate voltage since thermal equilibrium is not reached within the measurement time. Second, the way the readouts  $R_i$  are performed usually differs from the initial readout  $R_0$ . For example, in the JESD 241 standard [6],  $R_0$  is monitored after the end-of-sweep voltage whereas each subsequent readout is done after applying the stress voltage. This difference alone already results in a different interface charging state and therefore leads to an offset in  $\Delta V$  which is independent of the stress pulse itself.

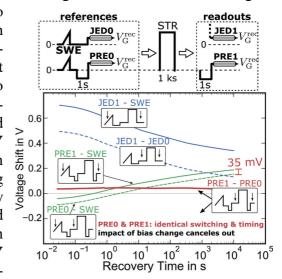

To overcome bias and timing dependent variations of  $\Delta V$ , we propose an optimized measurement pattern using preconditioning. Fig. 5 shows the impact of various readout patterns on  $\Delta V$  after a 1 ks positive bias stress (STR). As reference for the calculation of  $\Delta V$  we either use the sweep (SWE) itself, a bias switch from 0 V to  $V_G^{\rm rec}$  (JED0) or preconditioned readout (PRE0) with a -15 V accumulation pulse for 1 s. After STR, readout is preformed according to JESD 241 via switching di-

rectly to  $V_G^{\text{rec}}$  (JED1) or via preconditioning similar to PRE0 (PRE1). Each  $\Delta V$  recovery trace in Fig. 5 is given in relation to one of the reference readouts which is indicated by the minus sign. For the JEDEC-like readout JED1-JED0 (dashed blue),  $\Delta V$  recovers from ~500 mV to  $\sim$ 100 mV within 10 ks recovery time after STR.  $\Delta V$  recovery changes drastically by using preconditioned readout. The solid and dashed green curves represent  $\Delta V$ before (PRE0) and after (PRE1) STR. Since both readouts are performed under strictly identical switching conditions and show the same recovery trend, recovery behavior mainly depends on the switching conditions and is nearly independent of STR. The difference between both curves (PRE1-PRE0) gives the offset-free  $\Delta V$ caused by STR and is indicated in red and almost constant at 35 mV. This value gives a good estimation of the permanent component of  $\Delta V$  and can be reliably measured no matter if the delay is as short as 20ms or as long as 3 hours.

Fig 5. Top: switching variations for  $\Delta V$  calculation. Bottom:  $\Delta V$  resulting from chosen readout-reference combination.

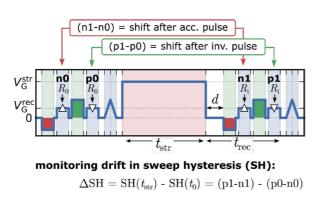

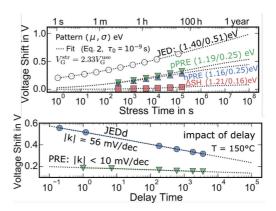

**Hysteresis Monitoring.** To enable monitoring of hysteresis (SH) effects [7] during high temperature gate stress, the accumulation pulse readout is extended via a second inversion preconditioning pulse at use-voltage (see Fig. 6). SH before the stress is given by p0-n0, whereas SH after the stress is given by p1-n1. The change in SH due to BTI is therefore given by  $\Delta$ SH = (p1-n1) – (p0-n0). Fig. 7 (top) shows a comparison of JESD 241 (JED, circles) and preconditioned BTI after a 1 s acc. pulse (nPRE) and after a succeeding 1 s inversion pulse (pPRE) for a 40 h,  $V_G^{\text{str}} = 2.3 V_G^{\text{use}}$  positive bias stress at 150°C. For JED,  $\Delta V$  is overestimated due to the offset induced by the different switching conditions. PRE measurements result in ~2 times lower and more accurate  $\Delta V$ . The difference between nPRE and pPRE results from the hysteresis (red squares) which slightly increases during high-T positive bias stress. In addition to the offset-free extraction of  $\Delta V$ , PRE allows for nearly delay time independent measurements. Fig. 7 (bottom) shows the impact of the delay time at  $V_G = 0$  V. Between d = 1 s and d = 10 ks,  $\Delta V$  decays from 520 mV to 290 mV for JEDd, and from 190 mV to 160 mV for PRE allowing for nearly delay time independent extraction of  $\Delta V$ .

Fig. 6. Preconditioned BTI measurement PRE with accumulation and inversion pulse preconditioning allowing for additional hysteresis monitoring.

Fig. 7. Top:  $\Delta V$  for  $t_{\rm str}$  up to 40h for JESD 241 and PRE under identical stress. Fit is done according to Eq. 2. Bottom: impact of d on  $\Delta V$  for JESD241 and preconditioned BTI.

## **Summary**

We investigated the impact of various BTI measurement parameters on the extracted voltage shift of 4H-SiC power MOSFETs. Using JEDEC-like measurements, the majority of  $\Delta V$  originates from recoverable and stress independent shift components solely defined by varying timing and switching parameters of each  $\Delta V$  extraction point. To overcome this issue and provide identical switching conditions, we demonstrate a sophisticated BTI measurement pattern using well defined preconditioning pulses prior to each  $\Delta V$  extraction point. Using this technique, shift components originating solely from the bias change cancel out allowing for accurate extraction of the permanent  $\Delta V$  component induced by the stress pulse. Voltage shifts extracted via preconditioned BTI are less dependent on measurement delay times within industrial timescales and do not include the impact of fully-recoverable hysteresis effects. Therefore, only this approach enables an accurate lifetime prediction of 4H-SiC MOSFETs.

#### Acknowledgement

This work was funded by the Austrian Research Promotion Agency (FFG, Project No. 860424).

## References

- [1] E. Zhang et al., IEEE Transactions on Device and Materials Reliability 12, 391-398, (2012).

- [2] A. J. Lelis, et al, IEEE Transactions on Electron Devices, vol. 55, no. 8, pp. 1835–1840, (2008).

- [3] A. Stoneham, Reports on Progress in Physics, vol. 44, no. 12, p. 1251, (1981).

- [4] C. Kittel, Introduction to solid state physics. Wiley, (2005).

- [5] T. Grasser, Bias Temperature Instability for Devices and Circuits, 447-481, Springer (2014).

- [6] Procedure for Wafer-Level DC Characterization of BTI, JEDEC Standard (2015).

- [7] G. Rescher, International Electron Devices Meeting, IEEE (2016).