# Stochastic Modeling of Hot-Carrier Degradation in nFinFETs Considering the Impact of Random Traps and Random Dopants

Alexander Makarov, Ben Kaczer, Philippe Roussel, Adrian Chasin, Michiel Vandemaele, Geert Hellings, Al-Moatasem El-Sayed, Markus Jech, Tibor Grasser, *Fellow, IEEE*, Dimitri Linten, Stanislav Tyaginov

Abstract—We present a stochastic description of hot-carrier degradation (HCD) which captures the impact of random traps (RTs) and random dopants (RDs) using our deterministic physical model for HCD. For each combination of stress voltages and stress time we generate 10,000 different samples with each of them having a unique configuration of RTs and RDs. Our analysis shows that both RTs and RDs broaden the set of degradation traces and device lifetimes, herewith resulting in average (over the sample ensemble) changes in the linear drain current lower than the nominal values from the deterministic model. Although at higher stress voltages device lifetimes follow bimodal normal distributions, at stress biases close to the operating regime the distributions are substantially different. Therefore, a proper modeling of HCD should be based on a full statistical description.

*Index Terms*—hot-carrier degradation, random dopants, random traps, physics-based modeling, FinFETs, carrier transport, interface traps

## I. INTRODUCTION

Hot-carrier degradation (HCD) becomes the dominant reliability concern as transistor dimensions shrink and shrink faster than the operating (and consequently stress) voltage scales. In this spirit, Intel reported that in their most advanced nodes (fin field-effect transistors, FinFETs) HCD is the most severe degradation mode [1]. Although HCD has been a subject of extensive research over several decades, most published HCD models are phenomenological/empirical and do not capture variability of HCD, which is another crucial reliability concern [2]. Indeed, sub-decananometer FETs contain a few dopants which are randomly distributed over the device, thereby resulting in sample-to-sample scattering of device characteristics typical even for pristine FETs. Although there are different sources responsible for transistor characteristic variability [3, 4], random dopant (RD) induced fluctuations have recently been reported to impact reliability of modern FETs fabricated by such leading semiconductor companies as IBM and TSMC

This work was supported in part by the European Union's Horizon 2020 research and innovation programme under the Marie Sklodowska-Curie grant agreement No 794950 and by the Austrian Science Fund (FWF), grant P31204-N30.

- A. Makarov, A.-M. El-Sayed, M. Jech and T. Grasser are with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria.

- B. Kaczer, Ph. Roussel, A. Chasin, M. Vandemaele, G. Hellings and D. Linten are with imec, Leuven 3001, Belgium.

- S. Tyaginov is with imec, Leuven 3001, Belgium and also with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria, and with the Ioffe Physical-Technical Institute, Russian Academy of Sciences, St. Petersburg 194021, Russia

[5,6]. In addition to RDs, interface traps generated by hotcarrier stress are also randomly placed. As a consequence, while the impact of RDs manifests itself in variability of unstressed device parameters, the random traps (RTs) lead to time dependent variability [7,8].

Although experimental studies of HCD variability were carried out by several groups [8–12] only a few stochastic modeling attempts exist which focus on HCD variability [13]. One of this approaches developed by Lie and co-authors [14] considers only the impact of RTs on HCD and all simulations were performed for devices with non-fluctuating doping concentrations. Another model published by Bottini *et al.* [13] presents a statistical analysis of both the impacts given by RDs and RTs in devices stressed under high voltages ( $V_{\rm ds} \geq 3.4\,\rm V$ ). At this bias HCD is driven by the single-carrier mechanism of Si-H bond dissociation and another mechanism, the multiple-carrier process, is not considered. However, in miniaturized transistors subjected to HC stress at low voltages the multiple-carrier mechanism governs HCD and determines device lifetime [15–18].

To bridge this gap, we present a comprehensive stochastic description of HCD in n-channel FinFETs which covers contributions of both RDs and RTs. For this, we use the deterministic physics-based model of hot-carrier degradation [19, 20] which was validated against HCD data acquired in devices with different geometries and over a wide range of stress conditions [21–23]. Note that the impact of RDs on HCD in n-channel FinFETs has already been addressed in our recent publications [24, 25] and in this work we consider the cumulative impact of RDs and RTs.

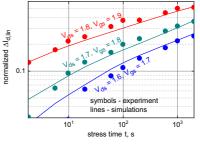

Fig. 1: Experimental and simulated (with the deterministic version of our HCD model) normalized changes of the linear drain current with time  $\Delta I_{\rm d.lin}(t)$ .

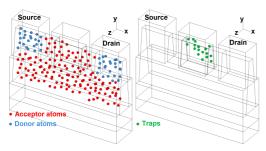

Fig. 2: Sketches of the FinFETs with RD (left panel) and RT (right panel).

### II. THE MODELING FRAMEWORK

The modeling framework is based on our physics-based model for HCD [19, 20, 26, 27] which considers Si-H bond rupture as a superposition of single- and multiple-carrier processes. For computing the rates of these mechanisms we employ the carrier energy distribution functions (DFs) which are obtained from the solution of the Boltzmann transport equation obtained from the deterministic solver ViennaSHE [21,28]. The model was calibrated to capture relative changes in the linear drain current  $\Delta I_{

m d,lin}$  vs. stress time t (Fig. 1) in nFinFETs (with a channel length of 28 nm and a gate stack containing SiO2 and HfO2 layers with the resulting EOT of 1.2 nm; the operating voltage is  $V_{\rm dd} = 0.9 \,\rm V$ ) stressed under three combinations of biases:  $V_{\rm ds} = 1.6\,{\rm V},\ V_{\rm gs} = 1.7\,{\rm V};$  $V_{\rm ds} = 1.7 \, \text{V}, \ V_{\rm gs} = 1.8 \, \text{V}; \ \text{and} \ V_{\rm ds} = 1.8 \, \text{V}, \ \tilde{V}_{\rm gs} = 1.9 \, \text{V}.$ Note that the model thus captures average experimental traces  $\Delta I_{\rm d.lin}(t)$  and parameterizes interface traps using the continuous concentration  $N_{\rm it}$ . This model version is called "deterministic" and its results "nominal".

Using the geometry of the initial device with the continuous doping concentration as a template we generated a set of 100 samples with individual RD configurations (Fig. 2). To achieve this goal, for each mesh cell we calculated the average number of dopants contained in this cell by multiplying the local value of the doping concentration and the cell volume; next the number of discrete impurity atoms was randomized using a Poisson random generator.

For each particular RD configuration we solved the Boltzmann transport equation to obtain carrier DFs and continuous  $N_{\rm it}$  concentrations. Then, we generated different configurations of RTs based on a certain continuous  $N_{\rm it}$  profile, see Fig. 2 in a manner analogous to the RD generation routine. In this case, we used the product of the density  $N_{\rm it}$  and the 2D cell area to calculate the mean number of traps in each cell which was then used for Poisson randomization, considering that the concentration  $N_{\rm it}$  and hence the number of traps in each cell is a non-decreasing function of time. Thus, a set of 100 samples with different RD configurations was created and then we generated 100 different RT configurations for each sample, each tuple of  $V_{\rm ds}, V_{\rm gs}$ , and each t step. Overall, for a fixed combination of  $V_{\rm ds}, V_{\rm gs}$  and t 10,000 samples were generated.

# III. RESULTS AND DISCUSSION

All calculations were performed for  $V_{\rm ds}=1.7$  V,  $V_{\rm gs}=1.8$  V;  $V_{\rm ds}=1.8$  V,  $V_{\rm gs}=1.9$  V; and  $V_{\rm ds}=1.0$  V,  $V_{\rm gs}=1.0$  V

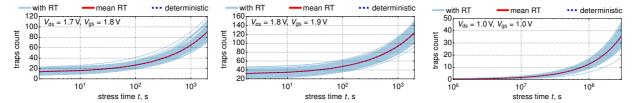

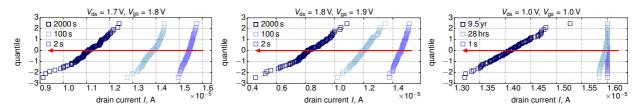

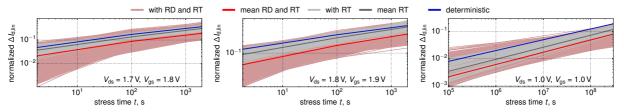

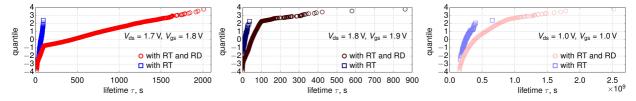

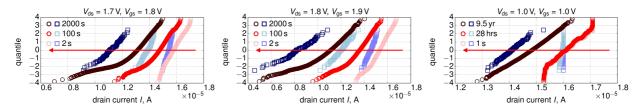

(close to  $V_{\rm dd}$ ). Fig. 3 summarizes the total number of traps contained in the entire device vs. t, their mean value, and the number of traps extracted for the nominal device (with no RT and RD variations). One can see that the mean and nominal numbers are equal. To check the impact of RTs on the device characteristics, we calculated probit plots (see Fig. 4) for the linear drain current  $I_{\rm d,lin}$  (stress times are 2 s, 100 s, and 2 ks) and sets of  $\Delta I_{\rm d.lin}(t)$  traces which are summarized in Fig. 5. From Fig. 4 one can see that the currents in degraded devices are normally distributed and the distributions become broader with stress times. Fig. 5 shows that  $\Delta I_{

m d,lin}$  in devices with varied RTs also have broad distributions with the corresponding mean values lower than those typical for the nominal  $I_{d,lin}(t)$  traces. Note that this trend is discussed in sufficient detail in our recent publication [24]. As for device lifetimes (which correspond to  $\Delta I_{\rm d,lin}$  = 0.1), from Fig. 6 we can conclude that they are approximately normally distributed (with some deviations visible at  $V_{\rm ds} = 1.0 \, \rm V$ ,  $V_{\rm gs} = 1.0 \, \rm V$ ).

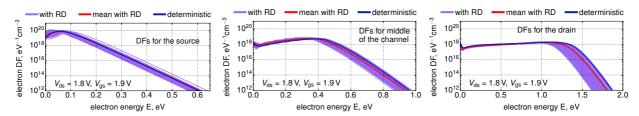

Electron DFs calculated for different RD configurations are plotted in Fig. 7 for the source, channel, and drain. The average DFs have lower values than the nominal DFs and this trend is especially pronounced near the drain, i.e. in the most degraded device spot. This suggests that the impact of RDs weakens HCD and shifts the  $\Delta I_{\rm d,lin}$  traces towards lower values. Fig. 8 presents a summary of quantile plots for  $I_{\rm d,lin}$  distributions calculated with the impacts of RTs and RDs (for comparison distributions from Fig. 4 are also shown) and confirms this trend: probit plots obtained with the impact of RDs spread over wider ranges, i.e. have longer tails at higher  $I_{\rm d,lin}$  values.

As for the  $\Delta I_{\rm d.lin}$  changes calculated with the impacts of both RDs and RTs (see Fig. 5), their distribution is much broader than that evaluated with the RTs impact only and the mean  $\Delta I_{\rm d,lin}(t)$  function  $(\langle \Delta I_{\rm d,lin} \rangle(t))$  has lower values than that extracted from the set with varied RTs. As a consequence of the interplay between RT and RD impacts, the  $\langle \Delta I_{\rm d,lin} \rangle(t)$  trace has lower values than that predicted by the deterministic model (see Fig. 5) [24]. From the probit plots for device lifetimes (Fig. 6) we can see that RTs and RDs results in two different slopes of the bimodal normal distribution extracted for higher stress voltages. The steeper fragment visible at shorter lifetimes stems from the impact of RTs and qualitatively corresponds to the probit plot calculated with the RT contribution only, while at longer stress times the distribution is determined by the RD impact. Qualitatively, this behavior is consistent with experimental lifetime distributions obtained for planar devices with a channel length of 28 nm and presented in a recent publication by imec [29]. It is important to emphasize that at  $V_{\rm ds}$  =  $V_{\rm gs}$  = 1.0 V the probability density has a significantly different shape. Note that our simulations performed by considering HCD variability induced exclusively by RDs also resulted in different slopes of lifetime distributions evaluated for accelerated stress regimes and milder operating conditions [24].

The reported tendency that the impact of RDs slows down HCD is consistent with the results of the Asenov group [30, 31] where the authors showed that the threshold voltage, mobility and the drain current extracted for devices with various RD configurations can be substantially different from

Fig. 3: Number of all interface traps generated during HC stress as a function of stress time. The mean number of traps is in good agreement with that calculated for the nominal devices with the continuous doping concentration.

Fig. 4: Evolution of probit plots of  $I_{\rm d,lin}$  current distributions with stress time calculated considering the impact of RTs. Distributions for stress time steps of 2 s, 100 s, and 2 ks are shown. Arrows show the increasing stress time.

Fig. 5: Sets of  $\Delta I_{\rm d,lin}(t)$  traces obtained with the impacts of both RTs and RDs. For comparison, the set of  $\Delta I_{\rm d,lin}(t)$  dependences computed with the impact of RTs only is also plotted.

Fig. 6: Probit plots for device lifetimes extracted from  $\Delta I_{\rm d,lin}(t)$  traces (plotted in Fig. 5) obtained considering the RT impact only (square symbols) and the mixture of RT and RD contributions (circles).

Fig. 7: Sets of electron energy distribution functions computed with the impact of RD for the source, channel, and drain. For comparison, the average DF as well as the DF for the nominal device with the continuous doping concentration are depicted.

Fig. 8: Probit plots for  $I_{d,lin}$  distributions calculated with the impacts of RDs and RTs (circles) as well as only with the impact of RTs (square symbols) for stress times of 2 s,  $100 \, \text{s}$ , and  $2 \, \text{ks}$ .

the continuous doping case. In both cases, the microscopic reason for that is a strong perturbation of the channel electrostatics by individual doping atoms which can result in a substantial suppression of the high energetical fraction of the carrier ensemble visible in Fig. 7. Another important conclusion which can be drawn from our statistical analysis is that both RT and RD contributions broaden the  $\Delta I_{\rm d,lin}(t)$  sets and lifetime distributions and lead to  $\langle \Delta I_{\rm d,lin} \rangle$  values smaller than the nominal  $\Delta I_{\rm d,lin}$  values obtained by the deterministic model. Finally, the fact that the lifetime probability density for the lowest voltages ( $V_{\rm ds} = V_{\rm gs} = 1.0\,\rm V$ ) is different than those obtained for higher voltages makes backward lifetime extrapolation problematic. All these considerations suggest that for a comprehensive description of HCD a stochastic analysis which covers both RT and RD contributions is needed.

# IV. CONCLUSIONS

The impacts of RTs and RDs on HCD were modeled and statistically analyzed using 10,000 device realizations with different configurations of RTs and RDs for each combination of stress voltages and for each stress time step. First, we generated 100 samples with different distributions of RDs, calculated carrier DFs, and then evaluated continuous  $N_{\rm it}$ profiles. Furthermore, for each of these  $N_{\rm it}$  concentrations we generated devices with different placements of discrete traps, evaluated  $\Delta I_{

m d,lin}$  changes and binned them in sets of  $\Delta I_{

m d,lin}(t)$  traces. A statistical analysis of these traces showed that both RTs and RDs broaden the sets of  $\Delta I_{\rm d,lin}$  traces and lifetime distributions and result in average  $\Delta I_{\rm d,lin}$  values smaller than those obtained from the deterministic model neglecting RTs and RDs. Finally, we showed that RTs and RDs lead to bimodal normal lifetime distributions, while at biases close to  $V_{\rm dd}$  these distributions are significantly different. This behavior substantially complicates backward extrapolation of device lifetimes and suggests that a full stochastic analysis of HCD is required.

### REFERENCES

- [1] A. Rahman, J. Dacuna, P. Nayak, G. Leatherman, and S. Ramey, "Reliability Studies of a 10nm High-performance and Low-power CMOS Technology Featuring 3rd Generation FinFET and 5th Generation HK/MG," in *IEEE Int. Reliability Physics Symposium*, 2018, pp. 6F.4–1–6F.4–6.

- [2] S. Ramey, M. Chahal, P. Nayak, S. Novak, C. Prasad, and J. Hicks, "Transistor Reliability Variation Correlation to Threshold Voltage," in Int. Reliability Physics Symposium, 2015, pp. 3B.2.1–3B.2.6.

- [3] A. R. Brown, J. R. Watling, A. Asenov, G. Bersuker, and P. Zeitzoff, "Intrinsic Parameter Fluctuations in MOSFETs due to Structural Nonuniformity of High-κ Gate Stack Materials," in *Proc. Simulation of Semiconductor Processes and Devices*, 2005, pp. 27–30.

- [4] S. Tyaginov, et al., "Statistical Analysis of Tunnel Currents in Scaled MOS Structures with a Non-uniform Oxide Thickness Distribution," Solid-State Electronics, vol. 49, no. 7, pp. 1192–1197, 2005.

- [5] S. R. Stiffler, et al., "Process Technology for IBM 14-nm Processor Designs Featuring Silicon-On-Insulator FinFETs," IBM Journal of Research and Development, vol. 62, no. 2/3, pp. 11:1–11:7, 2018.

[6] J. H. Lee, Y. M. Shcu, C. C. Wu, Y. M. Liu, Y. C. Chou, and S. C. Chin,

- [6] J. H. Lee, Y. M. Shcu, C. C. Wu, Y. M. Liu, Y. C. Chou, and S. C. Chin, "An Electrical Failure Analysis (EFA) Flow to Quantitatively Identify Invisible Defect on Individual Transistor: Using the Characterization of Random Dopant Fluctuation (RDF) as an Example," in *Int. Symp. Physical and Failure Analysis of Integrated Circuits (IPFA)*, 2018, pp. 1–5

- [7] A. Asenov, "Random Dopant Induced Threshold Voltage Lowering and Fluctuations in sub-0.1 μm MOSFET's: A 3-D Atomistic Simulation Study," *IEEE Transactions on Electron Devices*, vol. 45, no. 12, pp. 2505–2513, 1998.

- [8] B. Kaczer, et al., "Origins and Implications of Increased Channel Hot Carrier Variability in nFinFETs," in Int. Reliability Physics Symposium, 2015, pp. 3B.5.1–3B.5.6.

- [9] C. H. Tu et al., "Transistor Variability after CHC and NBTI Stress in 90 nm pMOSFET Technology," *Electronics Letters*, vol. 45, no. 16, pp. 854–856, 2009.

- [10] E. R. Hsieh, S. S. Chung, C. H. Tsai, R. M. Huang, C. T. Tsai, and C. W. Liang, "New Observations on the Physical Mechanism of Vthvariation in Nanoscale CMOS Devices after Long Term Stress," in *Int. Reliability Physics Symposium*, 2011, pp. XT.9.1–XT.9.2.

- [11] P. Magnone, F. Crupi, N. Wils, H. P. Tuinhout, and C. Fiegna, "Characterization and Modeling of Hot Carrier-Induced Variability in Subthreshold Region," *IEEE Transactions on Electron Devices*, vol. 59, no. 8, pp. 2093–2099, 2012.

- [12] S. S. Chung, "The Process and Stress-Induced Variability Issues of Trigate CMOS Devices," in *IEEE International Conference of Electron Devices and Solid-State Circuits*, June 2013, pp. 1–2.

- [13] R. Bottini, A. Ghetti, S. Vigano, M. G. Valentini, P. Murali, and C. Mouli, "Non-Poissonian Behavior of Hot Carrier Degradation Induced Variability in MOSFETs," in *Int. Reliability Physics Symposium*, 2018, pp. 6E.7–1–6E.7–6.

- [14] C. Liu, K. T. Lee, S. Pae, and J. Park, "New Observations on Hot Carrier Induced Dynamic Variation in Nano-scaled SiON/poly, HK/MG and FinFET Devices Based on On-the-fly HCI Technique: The Role of Single Trap Induced Degradation," in *Int. Electron Devices Meeting*, 2014, pp. 34.6.1–34.6.4.

- [15] W. McMahon, K. Matsuda, J. Lee, K. Hess, and J. Lyding, "The Effects of a Multiple Carrier Model of Interface States Generation of Lifetime Extraction for MOSFETs," in *Int. Conference on Modeling and Simulation of Microsystem*, vol. 1, 2002, pp. 576–579.

- Simulation of Microsystem, vol. 1, 2002, pp. 576–579.

[16] W. McMahon, A. Haggag, and K. Hess, "Reliability Scaling Issues for Nanoscale Devices," *IEEE Trans. Nanotech.*, vol. 2, no. 1, pp. 33–38, 2003.

- [17] A. Bravaix, C. Guerin, V. Huard, D. Roy, J. Roux, and E. Vincent, "Hot-Carrier Acceleration Factors for Low Power Management in DC-AC Stressed 40nm NMOS Node at High Temperature," in *Int. Reliability Physics Symposium*, 2009, pp. 531–546.

- [18] Y. Randriamihaja, X. Federspiel, V. Huard, A. Bravaix, and P. Palestri, "New Hot Carrier Degradation Modeling Reconsidering the Role of EES in Ultra Short n-channel MOSFETs," in *Int. Reliability Physics Symposium*, 2013, pp. 1–5.

- Symposium, 2013, pp. 1–5.

[19] S. Tyaginov, et al., "Physical Modeling of Hot-Carrier Degradation for Short- and Long-Channel MOSFETs," in Int. Reliability Physics Symposium, 2014, pp. XT.16–1–16–8.

[20] S. Tyaginov, et al., "A Predictive Physical Model for Hot-Carrier Degra-

- [20] S. Tyaginov, et al., "A Predictive Physical Model for Hot-Carrier Degradation in Ultra-Scaled MOSFETs," in Proc. Simulation of Semiconductor Processes and Devices, 2014, pp. 89–92.

- [21] M. Bina, et al., "Modeling of Hot Carrier Degradation Using a Spherical Harmonics Expansion of the Bipolar Boltzmann Transport Equation," in Int. Electron Devices Meeting, 2012, pp. 713–716.

- [22] P. Sharma, et al., "Modeling of Hot-Carrier Degradation in nLDMOS Devices: Different Approaches to the Solution of the Boltzmann Transport Equation," *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1811–1818, 2015.

- [23] A. Makarov, et al., "Hot-Carrier Degradation in FinFETs: Modeling, Peculiarities, and Impact of Device Topology," in *Int. Electron Devices Meeting*, 2017, pp. 13.1.1–13.1.4.

[24] A. Makarov, et al., "Modeling the Effect of Random Dopants on Hot-

- [24] A. Makarov, et al., "Modeling the Effect of Random Dopants on Hot-Carrier Degradation in FinFETs," in Int. Reliability Physics Symposium, 2019, pp. 1–7.

- [25] A. Makarov, et al., "Stochastic Modeling of the Impact of Random Dopants on Hot-Carrier Degradation in n-FinFETs," IEEE Electron Device Letters, vol. 40, no. 6, pp. 870–873, 2019.

- [26] M. Bina, et al., "Predictive Hot-Carrier Modeling of n-channel MOS-FETs," *IEEE Transactions on Electron Devices*, vol. 61, no. 9, pp. 3103–3110, 2014.

- [27] S. Tyaginov, et al., "Understanding and Modeling the Temperature Behavior of Hot-Carrier Degradation in SiON nMOSFETs," IEEE Electron Device Letters, vol. 37, no. 1, pp. 84–87, Jan 2016.

- [28] http://viennashe.sourceforge.net/, 2014.

- [29] E. Bury, et al., "Array-based Statistical Characterization of CMOS Degradation Modes and Modeling of the Time-Dependent Variability Induced by Different Stress Patterns in the  $V_{\rm G}, V_{\rm D}$  bias space," in Int. Reliability Physics Symposium, 2019, pp. 1–6.

- [30] A. Asenov, et al., "Random Telegraph Signal Amplitudes in sub 100 nm (Decanano) MOSFETs: a 3D 'Atomistic' Simulation Study," in Int. Electron Devices Meeting, 2000, pp. 279–282.

- [31] A. Asenov, et al., "Problems with the Continuous Doping TCAD Simulations of Decananometer CMOS Transistors," *IEEE Transactions* on Electron Devices, vol. 61, no. 8, pp. 2745–2751, Aug 2014.