# On Correlation Between Hot-Carrier Stress Induced Device Parameter Degradation and Time-Zero Variability

Alexander Makarov, Philippe Roussel, Erik Bury, Michiel Vandemaele, Alessio Spessot, Dimitri Linten, Ben Kaczer, and Stanislav Tyaginov

Abstract—We investigate correlation between linear drain currents  $(I_{\rm d,lin})$  in unstressed n-channel FinFETs and relative  $I_{\rm d,lin}$  changes  $(\Delta I_{\rm d,lin})$  during hot-carrier degradation (HCD). For this analysis we simulate 200 different realizations of a FinFET where each of these devices has its own unique distribution of random dopants. Our study shows that devices with superior performance (with higher time-zero  $I_{\rm d,lin}$  values) degrade faster than initially "worse" transistors (with lower initial  $I_{\rm d,lin}$  currents) and, correspondingly, device lifetime also decreases with the time-zero  $I_{\rm d,lin}$ .

*Index Terms*—Hot-carrier degradation, random dopants, variability, physical modeling, FinFETs, carrier transport, interface traps

### I. Introduction

In scaled field-effect transistors (FETs) the problem of device reliability has recently been reformulated in terms of time-dependent variability of device characteristics, as opposed to the deterministic picture typical for large-area transistors [1]. This paradigm shift is related to the stochastic nature of defect generation where a charged defect can be randomly placed in a device. Such a defect can impact transistor characteristics in different manners, depending on its position. Moreover, even pristine nanoscale FETs are not microscopically identical and sample-to-sample variability of transistor parameters at time-zero can be broad [2]. One can envisage that samples with superior properties degrade with a different rate compared to FETs of a poor quality.

Among these lines, Kerber and Nigam [3] showed experimental evidence that the threshold voltage values ( $V_{\rm th}$ ) in "virgin" FETs and their shifts  $\Delta V_{\rm th}$  during bias temperature instability (BTI) stress are correlated. In other words, transistors with better characteristics degrade faster and therefore have worse lifetimes as compared to initially "bad" devices. Quite to contrary, Hussin *et al.* [4] reported that  $\{V_{\rm th}, \Delta V_{\rm th}\}$  pairs are uncorrelated. The same tendency was shown by Angot *et al.* [5]. In addition, variability induced by self-heating was studied by the group of Asenov [6]; the authors showed that self-heating reduces the ON-current fluctuations.

This work was supported in part by the European Union's Horizon 2020 research and innovation programme under the Marie Sklodowska-Curie grant agreement No. 794950 and by the Austrian Science Fund (FWF), grant No. P31204-N30.

A. Makarov is with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria.

Ph. Roussel, E. Bury, M. Vandemaele, A. Spessot, D. Linten, B. Kaczer and S. Tyaginov are with imec, Leuven 3001, Belgium.

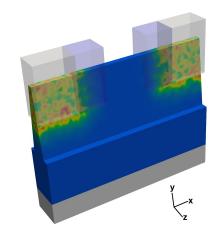

Fig. 1. A schematic representation of the FinFET with random dopants.

Finally, Gerrer and co-authors [7] discussed an increase in the defect generation rate in the vicinity of the percolation path and this behavior was attributed to a higher current density in the percolation path. Therefore, we conclude that there is correlation between time-zero and time-dependent variabilities of device characteristics during stress.

As for hot-carrier degradation (HCD) – which is reported to be the most detrimental reliability issue in modern MOSFETs [8] – Schlünder *et al.* [9] showed a strong correlation between

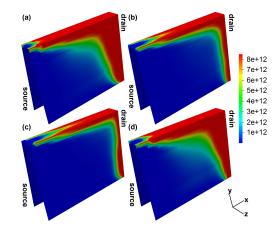

Fig. 2.  $N_{\mathrm{it}}$  densities shown for four different realizations of RD configurations corresponding to the same continuous doping profile. Calculations were performed for  $V_{\mathrm{ds}}=1.8\,\mathrm{V}$ ,  $V_{\mathrm{gs}}=1.9\,\mathrm{V}$  and  $t=200\,\mathrm{s}$ . The concentrations  $N_{\mathrm{it}}$  can be substantially different in devices with different RD configurations.

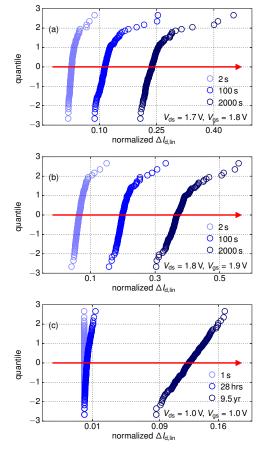

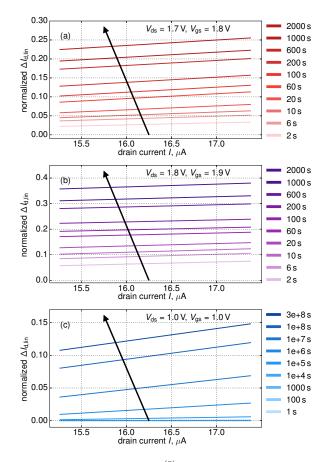

Fig. 3. Distributions of the normalized linear drain current change as probit plots calculated for three different combinations of  $V_{\rm gs}$  and  $V_{\rm ds}$ . One can see that the distributions become wider at longer stress times.

parameters in virgin devices and changes of these parameters. These authors have also shown that devices with initially higher drain current degrade faster than worse transistors with lower currents. However, to the best of our knowledge, no simulation studies of this correlation have been performed so far.

Thus, the goal of this work is to investigate correlation between time-zero values  $(I_{\rm d,lin}^{(0)})$  of the linear drain current  $(I_{\rm d,lin})$  in n-channel FinFETs and relative changes of these currents  $(\Delta I_{\rm d,lin})$  during hot-carrier stress and, further, HCD device lifetimes. For this, we use our recently developed stochastic model for HCD [10,11].

# II. THE MODELING FRAMEWORK

The framework for a stochastic description of HCD has been derived from the deterministic approach to hot-carrier degradation modeling [12–14], which was shown to represent HCD over a wide class of devices which includes high-voltage FETs (such as LDMOS transistors) [15], scaled planar FETs [13,16] and ultra-scaled FETs of 3D architectures, i.e. FinFETs [17] and NWFETs [18]. Within this approach, HCD is considered to be driven by dissociation of Si-H bonds at the  $\mathrm{Si/SiO_2}$  interface which can be triggered by the single-

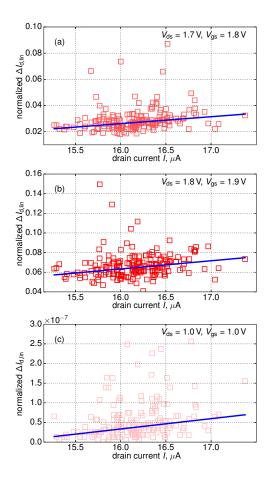

Fig. 4. Normalized changes in the linear drain current  $\Delta I_{\rm d,lin}$  plotted against time-zero values of the drain current  $I_{\rm d,lin}^{(0)}$ . The linear fit obtained with the robust correlation test shows that the median  $\Delta I_{\rm d,lin}$  increases with  $I_{\rm d,lin}^{(0)}$ . Data are shown at t=2s for  $V_{\rm ds}=1.7$  V,  $V_{\rm gs}=1.8$  V and  $V_{\rm ds}=1.8$  V,  $V_{\rm gs}=1.9$  V and at t=1s for  $V_{\rm ds}=V_{\rm gs}=1.0$  V.

and multiple-carrier mechanisms of Si-H bond rupture, as well as by their superpositions. As suggested in our previous publications [13, 16], as well as by Randriamihaja et al. [19, 20], the most probable pathway of the Si-H bond dissociation reaction is related to preexcitation of the bond by several cold carriers followed by a hot carrier bombardment which breaks the bond. To compute the rates of these processes, we use the carrier energy distribution functions which are obtained from a solution of the Boltzmann transport equation with the deterministic transport simulator ViennaSHE [21]. For obtaining the device architecture the Sentaurus Process simulator [22] is employed. Note that Sentaurus Process generates device structures with continuous doping profiles. Since the Si/dielectric interface is a disordered system, the bond-breakage energy is a stochastically distributed quantity and our HCD model assumes that this energy follows the normal distribution.

Our statistical analysis considers the impact of random dopants (RDs) on HCD and was conducted using experimental data measured employing n-channel FinFETs (which are schematically depicted in Fig. 1). These devices have a

Fig. 5. Linear fits of  $\Delta I_{

m d,lin}$  vs.  $I_{

m d,lin}^{(0)}$  for all stress time steps extracted from the simulated data using the robust correlation test.

gate length of  $L_{\rm g}=40\,{\rm nm}$ , an operating voltage of  $V_{\rm dd}=0.9\,{\rm V}$  and a high-k gate stack composed from  ${\rm SiO_2}$  and  ${\rm HfO_2}$  layers with a resulting equivalent oxide thickness of  $\sim 1.2\,{\rm nm}$ . These devices were stressed at three different combinations of source-gate ( $V_{\rm gs}$ ) and source-drain ( $V_{\rm ds}$ ) voltages:  $V_{\rm ds}=1.6\,{\rm V},\,V_{\rm gs}=1.7\,{\rm V},\,V_{\rm ds}=1.7\,{\rm V},\,V_{\rm gs}=1.8\,{\rm V};$  and  $V_{\rm ds}=1.8\,{\rm V},\,V_{\rm gs}=1.9\,{\rm V}$ . HC stress was performed at room temperature for  $\sim 2\,{\rm ks}$ . All these combinations correspond to  $V_{\rm gs}\sim V_{\rm ds}$ , i.e. to the worst-case conditions of hot-carrier degradation in short-channel devices [23,24]. During HC stress changes in the linear drain current  $\Delta I_{\rm d,lin}$  ( $I_{\rm d,lin}$  corresponds to  $V_{\rm ds}=0.05\,{\rm V}$  and  $V_{\rm gs}=V_{\rm dd}$ ) were recorded as functions of stress time t. In our recent publication [17] the deterministic HCD model was shown to accurately reproduce experimental  $\Delta I_{\rm d,lin}(t)$  dependencies.

In the stochastic approach to HCD modeling the device architecture with continuous doping profiles was used to generate a set of 200 different instantiations with discrete dopants (see [10,11] for details). In each of these instantiations RDs are distributed throughout the device in a unique manner. Then for each of these RD configurations we solved the Boltzmann transport equation, obtained carrier energy distribution functions, calculated interface state densities  $N_{\rm it}$  (depicted in Fig. 2), and then  $\Delta I_{\rm d,lin}(t)$  traces. The dependencies of  $\Delta I_{\rm d,lin}(t)$

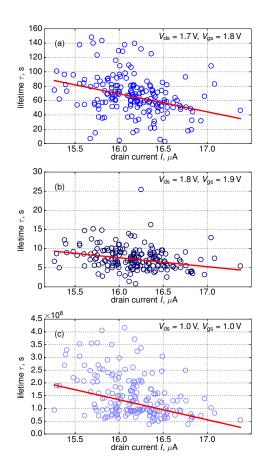

Fig. 6. Dependencies of device lifetime on the time-zero linear drain current  $I_{\rm d,lin}^{(0)}$  extracted from statistical data. One can see that devices with higher  $I_{\rm d,lin}^{(0)}$  degrade faster, i.e. the corresponding lifetimes are shorter.

on stress time t were used to extract device lifetimes (lifetime is defined as time when the relative change of the linear drain current reaches 10%). Note that all these calculations were preformed for two stress voltages ( $V_{\rm ds}=1.7~{\rm V},~V_{\rm gs}=1.8~{\rm V}$  and  $V_{\rm ds}=1.8~{\rm V},~V_{\rm gs}=1.9~{\rm V}$ ) and for much milder biases  $V_{\rm ds}=V_{\rm gs}=1.0~{\rm V}$  which imitate conditions very similar to the operating regime.

# III. RESULTS AND DISCUSSIONS

Fig. 3 shows distributions of  $\Delta I_{\rm d,lin}$  changes evaluated for three aforementioned combinations of stress voltages. These  $\Delta I_{\rm d,lin}$  distributions become broader with stress time. Also, as we showed in [10,11], distributions of the linear drain current  $I_{\rm d,lin}$  become broader. This trend contradicts the result reported by Schlünder *et al.* [9] where the authors showed that the drain current variability slightly improved during long-term (up to 10 years) hot carriers stress. However, Schlünder and co-authors used a technique which allows extrapolation to long stress times at device use conditions; such techniques are typically based on empirical/phenomenological expressions and therefore are not sufficient to capture the entire complexity of HCD.

Fig. 4 shows  $\{\Delta I_{\rm d,lin}, I_{\rm d,lin}^{(0)}\}$  tuples (where  $I_{\rm d,lin}^{(0)}$  is the time-zero linear drain current) obtained for 200 instantiations and plotted for all three combinations of stress voltages and one stress time step with  $t=2\,\rm s$ . Because the data shown in Fig. 4 are very scattered, in order to extract a (possible)  $\Delta I_{\rm d,lin}(I_{\rm d,lin}^{(0)})$  dependence we performed the robust linear fits using the Kendall rank correlation coefficient [25]. One can see that all three datasets exhibit highly significant rank correlation. Moreover, plotted trends clearly show that the change in the linear drain current becomes more pronounced in FinFETs with higher values of  $I_{\rm d,lin}^{(0)}$ .

In the same manner we computed  $\Delta I_{\rm d,lin}(I_{\rm d,lin}^{(0)})$  dependences for each stress time step which are summarized in Fig. 5. We can conclude that for each value of t the degradation remains more pronounced in "initially better" devices (i.e. in devices with higher  $I_{\rm d,lin}^{(0)}$  values). Dependencies of device lifetime on the time-zero linear drain current (see Fig. 6) show visible TTF reduction with increasing  $I_{\rm d,lin}^{(0)}$  and this behavior is consistent with the trend pronounced in Figs. 4 and 5. Note finally, that a very similar reduction of  $\Delta V_{\rm th}$  variability at long BTI stresses was previously reported in [3].

### IV. CONCLUSIONS

We statistically processed linear drain current HCD traces  $\Delta I_{\rm d,lin}(t)$  which were calculated for 200 configurations of random dopants in the n-channel FinFET. This analysis allowed us to identify correlation between time-zero linear drain currents and their changes during stress and then extract the dependence of device lifetime on  $I_{\rm d,lin}(t=0)$ . The obtained trends show that superior FinFETs with initially higher  $I_{\rm d,lin}$  values degrade faster and have shorter lifetimes.

# REFERENCES

- [1] T. Grasser, B. Kaczer, W. Gös, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, J. Franco, M. Toledano-Luque, and M. Nelhiebel, "The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps," *IEEE Transactions on Electron Devices*, vol. 58, no. 11, pp. 3652–3666, 2011.

- [2] A. Asenov, G. Slavcheva, A. R. Brown, J. H. Davies, and S. Saini, "Increase in the Random Dopant Induced Threshold Fluctuations and Lowering in sub-100 nm MOSFETs due to Quantum Effects: a 3-D Density-gradient Simulation Study," *IEEE Transactions on Electron Devices*, vol. 48, no. 4, pp. 722–729, Apr 2001.

- [3] A. Kerber and T. Nigam, "Correlation of BTI induced device parameter degradation and variation in scaled Metal Gate / High-k CMOS technologies," in 2014 IEEE International Reliability Physics Symposium, June 2014, pp. 6A.6.1–6A.6.6.

- [4] R. Hussin, S. M. Amoroso, L. Gerrer, B. Kaczer, P. Weckx, J. Franco, A. Vanderheyden, D. Vanhaeren, N. Horiguchi, and A. Asenov, "Interplay Between Statistical Variability and Reliability in Contemporary pMOSFETs: Measurements Versus Simulations," *IEEE Transactions on Electron Devices*, vol. 61, no. 9, pp. 3265–3273, Sep. 2014.

- [5] D. Angot, V. Huard, L. Rahhal, A. Cros, X. Federspiel, A. Bajolet, Y. Carminati, M. Saliva, E. Pion, F. Cacho, and A. Bravaix, "BTI Variability Fundamental Understandings and Impact on Digital Logic by the Use of Extensive Dataset," in 2013 IEEE International Electron Devices Meeting, Dec 2013, pp. 15.4.1–15.4.4.

- [6] L. Wang, A. R. Brown, M. Nedjalkov, C. Alexander, B. Cheng, C. Millar, and A. Asenov, "Impact of Self-Heating on the Statistical Variability in Bulk and SOI FinFETs," *IEEE Transactions on Electron Devices*, vol. 62, no. 7, pp. 2106–2112, July 2015.

- [7] L. Gerrer, R. Hussin, S. M. Amoroso, J. Franco, P. Weckx, M. Simicic, N. Horiguchi, B. Kaczer, T. Grasser, and A. Asenov, "Experimental Evidences and Simulations of Trap Generation along a Percolation Path," in 2015 45th European Solid State Device Research Conference (ESSDERC), Sep. 2015, pp. 226–229.

- [8] A. Rahman, J. Dacuna, P. Nayak, G. Leatherman, and S. Ramey, "Reliability Studies of a 10nm High-performance and Low-power CMOS Technology Featuring 3rd Generation FinFET and 5th Generation HK/MG," in 2018 IEEE International Reliability Physics Symposium (IRPS), March 2018, pp. 6F.4–1–6F.4–6.

- [9] C. Schlünder, J. Berthold, F. Proebster, A. Martin, W. Gustin, and H. Reisinger, "On the Influence of BTI and HCI on Parameter Variability," in 2017 IEEE International Reliability Physics Symposium (IRPS), April 2017, pp. 2E–4.1–2E–4.8.

- [10] A. Makarov, B. Kaczer, P. Roussel, A. Chasin, A. Grill, M. Vandemaele, G. Hellings, E.-M. El-Sayed, T. Grasser, D. Linten, and S. Tyaginov, "Modeling the Effect of Random Dopants on Hot-Carrier Degradation in FinFETs," in *Proc. International Reliability Physics Symposium (IRPS)*, 2019, pp. 6C.3.1–6C.3.6.

- [11] A. Makarov, B. Kaczer, P. Roussel, A. Chasin, A. Grill, M. Vandemaele, G. Hellings, A. El-Sayed, T. Grasser, D. Linten, and S. Tyaginov, "Stochastic Modeling of the Impact of Random Dopants on Hot-Carrier Degradation in n-FinFETs," *IEEE Electron Device Letters*, vol. 40, no. 6, pp. 870–873, June 2019.

- [12] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmail, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Interface Traps Density-of-states as a Vital Component for Hot-carrier Degradation Modeling," *Microelectronics Reliability*, vol. 50, pp. 1267–1272, 2010.

- [13] S. Tyaginov, M. Bina, J. Franco, Y. Wimmer, D. Osintsev, B. Kaczer, and T. Grasser, "A Predictive Physical Model for Hot-Carrier Degradation in Ultra-Scaled MOSFETs," in *Proc. Simulation of Semiconductor Processes and Devices (SISPAD)*, 2014, pp. 89–92.

- [14] S. Tyaginov, M. Jech, J. Franco, P. Sharma, B. Kaczer, and T. Grasser, "Understanding and Modeling the Temperature Behavior of Hot-Carrier Degradation in SiON nMOSFETs," *IEEE Electron Device Letters*, vol. 37, no. 1, pp. 84–87, Jan 2016.

- [15] P. Sharma, S. Tyaginov, Y. Wimmer, F. Rudolf, K. Rupp, M. Bina, H. Enichlmair, J.-M. Park, R. Minixhofer, H. Ceric, and T. Grasser, "Modeling of Hot-Carrier Degradation in nLDMOS Devices: Different Approaches to the Solution of the Boltzmann Transport Equation," *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1811–1818, 2015.

- [16] S. Tyaginov, M. Bina, J. Franco, D. Osintsev, O. Triebl, B. Kaczer, and T. Grasser, "Physical Modeling of Hot-Carrier Degradation for Short- and Long-Channel MOSFETs," in *Proc. International Reliability Physics Symposium (IRPS)*, 2014, pp. XT.16–1–16–8.

- [17] A. Makarov, S. E. Tyaginov, B. Kaczer, M. Jech, A. Chasin, A. Grill, G. Hellings, M. Vexler, D. Linten, and T. Grasser, "Hot-Carrier Degradation in FinFETs: Modeling, Peculiarities, and Impact of Device Topology," in *Proc. International Electron Devices Meeting (IEDM)*, 2017, pp. 13.1.1–13.1.4.

- [18] M. Vandemaele, B. Kaczer, S. Tyaginov, Z. Stanojević, A. Makarov, A. Chasin, E. Bury, H. Mertens, D. Linten, and G. Groeseneken, "Full (Vg, Vd) Bias Space Modeling of Hot-Carrier Degradation in Nanowire FETs," in 2019 IEEE International Reliability Physics Symposium (IRPS), March 2019, pp. 1–7.

- [19] Y. Randriamihaja, A. Zaka, V. Huard, M. Rafik, D. Rideau, D. Roy, A. Bravaix, and P. Palestri, "Hot Carrier Degradation: From Defect Creation Modeling to Their Impact on NMOS Parameters," in *Proc. International Reliability Physics Symposium (IRPS)*, 2012, pp. 1–4.

- [20] Y. Randriamihaja, X. Federspiel, V. Huard, A. Bravaix, and P. Palestri, "New Hot Carrier Degradation Modeling Reconsidering the Role of EES in Ultra Short n-channel MOSFETs," in *Proc. International Reliability Physics Symposium (IRPS)*, 2013, pp. 1–5.

- [21] M. Bina, K. Rupp, S. Tyaginov, O. Triebl, and T. Grasser, "Modeling of Hot Carrier Degradation Using a Spherical Harmonics Expansion of the Bipolar Boltzmann Transport Equation," in *Proc. International Electron Devices Meeting (IEDM)*, 2012, pp. 713–716.

- [22] Sentaurus Process User guide, O-2018.06, Synopsys, 2018.

- [23] A. Bravaix and V. Huard, "Hot-Carrier Degradation Issues in Advanced CMOS Nodes," in Proc. European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF), tutorial, 2010, pp. 1267– 1272.

- [24] S. Rauch and G. L. Rosa, "CMOS Hot Carrier: From Physics to End Of Life Projections, and Qualification," in *Proc. International Reliability Physics Symposium (IRPS)*, tutorial, 2010.

- [25] M. G. Kendall, "A New Measure of Rank Correlation," *Biometrika*, vol. 30, no. 1-2, pp. 81–93, 06 1938.