# Full $(V_g, V_d)$ Bias Space Modeling of Hot-Carrier Degradation in Nanowire FETs

Michiel Vandemaele\*<sup>†</sup>, Ben Kaczer<sup>†</sup>, Stanislav Tyaginov<sup>†</sup>§¶, Zlatan Stanojević<sup>‡</sup>, Alexander Makarov<sup>§</sup>, Adrian Chasin<sup>†</sup>, Erik Bury<sup>†</sup>, Hans Mertens<sup>†</sup>, Dimitri Linten<sup>†</sup> and Guido Groeseneken\*<sup>†</sup>

\*ESAT, KU Leuven, Leuven, Belgium Email: michiel.vandemaele@imec.be †imec, Leuven, Belgium †Global TCAD Solutions GmbH, Vienna, Austria §Institute for Microelectronics, TU Wien, Vienna, Austria ¶Ioffe Physical-Technical Institute, St.-Petersburg, Russia

Abstract—Simulations of hot-carrier degradation of nanowire field-effect transistors are reported. The simulations rely on the carrier energy distribution function, obtained by solving the Boltzmann transport equation. To model the contribution of impact ionization, the hydrodynamic scheme is employed. A range of pertinent physical mechanisms is invoked and discussed to adequately reproduce HCD measurements in the full  $(V_{\rm g},V_{\rm d})$  bias space. Impact ionization is discussed as an important ingredient of HCD at low gate, high drain voltages.

Index Terms—hot-carrier degradation, nanowire FETs, carrier energy distribution function, interface defects, TCAD, impact ionization

## I. INTRODUCTION

Together with bias temperature instability (BTI) and time-dependent dielectric breakdown (TDDB), hot-carrier degradation (HCD) is one of the main MOSFET reliability concerns. Hot carriers (HCs) are electrons or holes with large kinetic energies gained from high electric fields in a transistor. When colliding with the MOSFET Si-SiO<sub>2</sub> interface, HCs can break Si-H bonds present there, causing formation of defects and distortion of the transistor's characteristics. In the most recent CMOS technologies, HCD is becoming critical because the transistors continue to scale while the supply voltage remains approximately constant [1], [2].

Two different HC interface state generation modes are observed experimentally in scaled transistors [3]–[5], as evidenced by the fact that the measured (normalized) timesto-failure follow either a stress drain voltage dependence or a stress current dependence (sometimes an additional third 'mixed' mode in between is distinguished). These two HC modes are normally identified as the single-particle (SP) and the multiple-particle (MP) mechanisms of Si-H bond breakage, respectively. In the former, a single carrier collides with the Si-H bond and has sufficient energy to break it in one strike. In the latter, multiple carriers, each having insufficient energy to break the bond, induce vibrational excitations of the bond upon collision and increase the bond energy. This lowers the potential barrier for the bond rupture reaction, which allows a less energetic carrier to break the bond [6].

Physics-based modeling of HCD is desired i) to enhance understanding of this FET reliability problem and ii) to ultimately be able to predict HCD to guide and optimize CMOS technology development. During circuit operation, many transistors experience not fixed, but changing voltages on their gate and drain contacts. Combined with the occurrence of different HC modes (SP and MP mechanism) depending on the applied  $(V_g, V_d)$  stress, this necessitates modeling HCD over the full  $(V_g, V_d)$  bias space. The occurrence of both the SP and MP process also requires to calculate the carrier energy distribution function (DF) for the device by solving the Boltzmann transport equation (BTE) to model HCD [7]–[11].

This work focusses on DF based simulations of HCD of NW FETs over the full  $(V_{\rm g},V_{\rm d})$  bias space and quantitatively compares the results to measurements. The first section explains the simulation methodology and the physical effects which are captured. Next, the text discusses the results of the simulations and how they compare to the measured data. The last section summarizes the work.

# II. METHODOLOGY

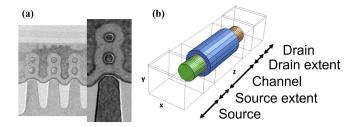

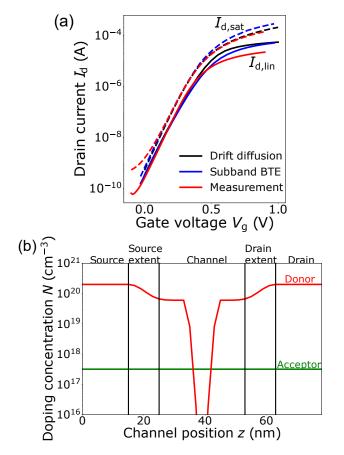

The devices studied in this work are Si nMOS NW FETs containing each 8 wires with a gate length of 28 nm and a diameter of 9 nm (Fig. 1a). We refer to Mertens *et al.* [12], [13] and Chasin *et al.* [3] for the description of the fabrication and HC measurements of the transistors, respectively. A 3D simulation structure with 1 NW was used (Fig. 1b). Calibration of the time-0 threshold voltage and subthreshold slope was done by thorough tuning of the doping profiles in the simulation structure and matching the result of drift-diffusion simulations in Minimos-NT [14], [15] to the measurements (Fig. 2), similar to Bufler *et al.* [16]. The *I-V* curves were also calculated by solving the subband Boltzmann Transport Equation (BTE), resulting in the same subthreshold slope and threshold voltage as the drift-diffusion solution (Fig. 2a), except for a difference in the gate work function of 30 meV.

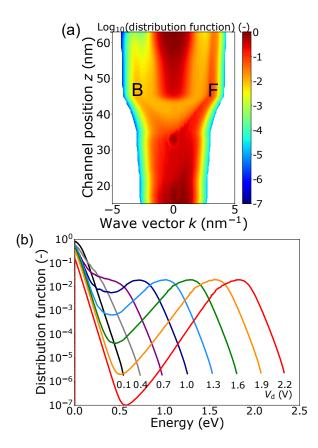

The subband BTE is solved for the NW FET in the channel and the source/drain extension regions using GTS NDS [17], [18] to obtain the electron DF (Fig. 3). Phonon, ionized

Fig. 1. (a) TEM cross-section and (b) simulation structure of the nanowire (NW) FET. The NW has a diameter of  $\sim 9$  nm. The real device has 8 NWs in parallel, but only 1 NW is simulated.

Fig. 2. (a) Nanowire *I-V* curves calculated before stress (i.e. at time-0) by solving the drift-diffusion equations (black curves) and the subband BTE (blue curves). The 2 methods result in a gate work function difference of 30 meV. (b) Calibrated doping profiles in the device used to calculate the curves in (a).

impurity and surface roughness scattering are captured in the calculation of the DF, but impact-ionization (I/I) and electron-electron scattering are presently not. We solved the coupled Schrödinger-Poisson equations in the planes perpendicular to the transport direction to take quantum effects into account. Self-heating is not included in the simulations, but the ingredients of the model (e.g. the DFs) are temperature dependent. This allows in principle to extend the model with self-heating, by performing simulations at the real (elevated) device temperature (obtained from measurements or simulations) instead of at the ambient temperature.

Fig. 3. (a) Distribution function in position (z) - wave vector (k) space for  $V_{\rm g}=1.9$  V,  $V_{\rm d}=1$  V. The letters 'F' and 'B' indicate the stream of forward moving and backscattered carriers in the device, respectively. (b) Distribution functions at the drain end of the channel for  $V_{\rm g}=1.9$  V and varying drain voltages.

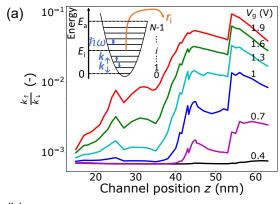

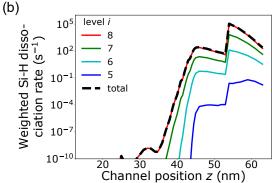

To calculate the density of interface defects (broken Si-H bonds), the approach of Bina et al. [8] is followed. The vibrational states of the Si-H bonds are modeled using a truncated harmonic oscillator potential with a distance  $\hbar\omega = 0.25 \text{ eV}$ between the vibrational levels (inset of Fig. 4a) [19]. The bond vibrational energy increases or decreases with one energy quantum  $\hbar\omega$  at the excitation rate  $k_{\uparrow}$  or de-excitation rate  $k_{\downarrow}$  respectively (Fig. 4a). Both incident carriers (through the multi vibrational excitation (MVE) acceleration integral [8]) and interactions of the bond with the lattice can initiate these transitions. In each vibrational state i, complete dissociation of the Si-H bond is possible at a rate  $r_i$  (Fig. 4b). Bond breakage can be initiated both by colliding carriers (through the antibonding (AB) acceleration integral [8]) or thermally. The total Si-H dissociation rate R, taking into account contributions form all vibrational levels, is given by:

$$R = \frac{1}{M} \sum_{i=0}^{N-1} r_i \left(\frac{k_{\uparrow}}{k_{\downarrow}}\right)^i \quad \text{with} \quad M = \sum_{i=0}^{N-1} \left(\frac{k_{\uparrow}}{k_{\downarrow}}\right)^i \tag{1}$$

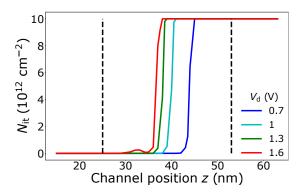

and is then converted into a density of interface defects (Fig. 5) as follows:

Fig. 4. (a) Ratio of the Si-H bond excitation  $(k_{\uparrow})$  and de-excitation  $(k_{\downarrow})$  rate for varying  $V_{\rm g}$  at  $V_{\rm d}=1$  V. (inset of a) Schematic depiction of the truncated harmonic potential used to model the vibrational energy of the Si-H bonds with the definition of the physical quantities discussed. (b) Si-H bond dissociation rate  $r_{\rm i}$  from each level i, weighted with the occupation of that level for  $V_{\rm g}=1.9$  V,  $V_{\rm d}=1$  V. The black dotted line is the total Si-H dissociation rate, i.e. the sum of the different curves for each i.

$$N_{\rm it}(z,t) = N_{\rm it,max}(1 - \exp\left(-R(z)t\right)) \tag{2}$$

The number of broken Si-H bonds saturates with time to the level of dangling bonds  $N_{\rm it,max}$  present before hydrogen passivation.

Contrary to Bina *et al.* [8], the MVE and AB acceleration integrals are not calculated as an integral over energy of the product of the DF with a scattering cross section, the density-of-states (DOS) and the carrier velocity. Instead, the acceleration integral is obtained using Fermi's golden rule from the quantum mechanical overlap between the state k and k' of the carrier before and after its interaction with the Si-H bond. This overlap is summed over all possible states k and k' and is calculated in GTS NDS [17].

For the interface defects, we employed a DOS  $g(\epsilon)$  which is uniform as a function of energy, i.e.  $g(\epsilon)=g_0=$  constant for  $\epsilon_{\min}<\epsilon<\epsilon<\epsilon_{\max}$  and  $g(\epsilon)=0$  otherwise. This uniform DOS is a simplification, but it should not strongly affect the results for the degradation parameters considered in this work ( $\Delta I_{\rm d}$  and  $\Delta V_{\rm th}$ ), since the Fermi level does not change much above the threshold voltage. Matching of the simulated degradation to the measured one was obtained by adjusting the energy positions  $\epsilon_{\min}$  and  $\epsilon_{\max}$ .

Fig. 5. Simulated interface defect profiles  $N_{\rm it}$  along the channel for different  $V_{\rm d}$  at  $V_{\rm g}=1.9$  V. The vertical dotted lines indicate the borders between the source extension, channel and drain extension regions.

To model the BTI component in the measured data, we added pre-existing bulk oxide defects in the HfO<sub>2</sub> layer in the simulations. The energy position of the oxide defects is 3.82 eV above the valence band edge and the concentration is  $2.9 \times 10^{20}$  cm<sup>-3</sup> (cfr. Rzepa *et al.* [20]). We calibrated the occupancy of the oxide defects to the measured  $\Delta V_{\rm th}$  for every  $V_{\rm g}$  at  $V_{\rm d}$  = 0.1 V and assumed the occupancy to be independent of  $V_{\rm d}$  in the ( $V_{\rm g}$ ,  $V_{\rm d}$ ) bias space.

The device with defects is simulated again to obtain the degradation ( $\Delta V_{\rm th}$ ,  $\Delta I_{\rm d,lin}$ ,  $\Delta I_{\rm d,sat}$ ,  $\Delta I_{\rm d,sat,rev}$ ). We calculated the post-stress I-Vs by solving the drift-diffusion equations. The simulated on-current of the NW FET is not calibrated to the measured one. Despite this, we still capture the main degradation trends with the simulations, because we consider relative current changes (i.e. normalized to the pre-stress I-V). Unless specified otherwise, we performed simulations for  $T=125~{}^{\circ}\text{C}$  and  $t=530~\mathrm{s}$ , corresponding to the measurements in [3]. The sense drain voltages in the linear and saturation region were 0.05 V and 0.9 V respectively.

# III. RESULTS AND DISCUSSION

When viewed in position (z) - wave vector (k) space, the DF shows a 'high probability stream' towards increasing positive momenta p ( $p = \hbar k$ ) for increasing z values (Fig. 3a, indicated with 'F'). This represents the movement of electrons from the source to the drain. Due to the scattering in the device, a second, smaller stream towards negative momenta is formed (Fig. 3a, indicated with 'B'). At fixed position z and as function of energy, the DF first shows a Maxwellian behavior, followed by a minimum, a peak and finally a thermal high-energy tail (Fig. 3b). For some positions, the Maxwellian shape at low energies is not present (not shown). The tail of the DF shifts to higher energies when moving from source to drain. The minimum becomes more pronounced for increasing  $V_{\rm d}$ .

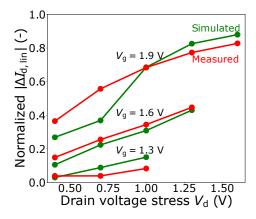

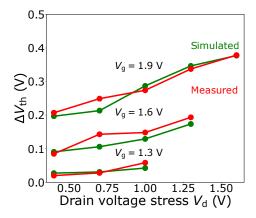

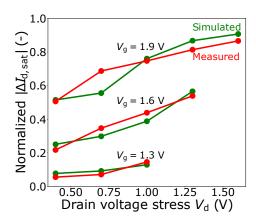

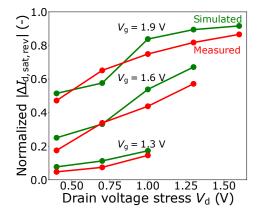

We simulated the stress-induced shift of several FET parameters ( $V_{\rm th}$ ,  $I_{\rm d,lin}$ ,  $I_{\rm d,sat}$ ,  $I_{\rm d,sat,rev}$ ) over the full ( $V_{\rm g},V_{\rm d}$ ) bias space. We obtained reasonable agreement between measurements and simulations using a single parameter set for

Fig. 6. Simulated vs. measured shift in linear drain current for  $V_{\rm d} < V_{\rm g}$ .

Fig. 7. Simulated vs. measured shift in threshold voltage for  $V_{

m d} < V_{

m g}$ .

$V_{\rm d} < V_{\rm g}$  (Figs. 6 - 9). For this, the traps had to be located over the energy range of  $[\epsilon_{\rm min} = \epsilon_{\rm v} + 0.11 \ {\rm eV},$   $\epsilon_{\rm max} = \epsilon_{\rm v} + 1.21 \ {\rm eV}]$ , with  $\epsilon_{\rm v}$  being the Si valence band edge. For most of these bias points, the total Si-H bond breakage rate is dominated by dissociation from the upper level in the oscillator potential (i=8, Fig. 4b). This indicates that the MP mechanism is dominant in this region. With increasing stress, the interface defect front propagates deeper in the channel towards the source (Fig. 5), causing larger degradation.

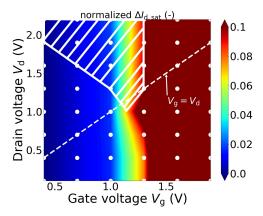

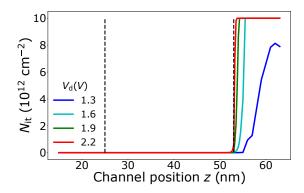

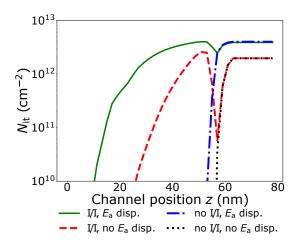

For  $V_{\rm d}>V_{\rm g}$ , the simulations do not reproduce the measured degradation. At some  $(V_{\rm g},V_{\rm d})$  points in this region, degradation is completely missing in the simulations (Fig. 10, white hatched area, compare to Fig. 3 in [3]), while at other points the simulated degradation is too low. For the bias points with no degradation in the simulations, defects are created only in the drain extension and do not enter the channel (Fig. 11), thereby influencing the post-stress I-V negligibly. From the measurements, it was concluded that mostly the SP mechanism is dominant in this region. For the bias points with too low degradation, defects are present in the channel in the simulations, but similarly they do not extend deep enough into the channel to cause the (larger) measured degradation.

The origin of this discrepancy is the fact that I/I is ignored in the calculation of the DF. During their travel toward the source,

Fig. 8. Simulated vs. measured shift in saturation drain current for  $V_{\rm d} < V_{\rm g}$ .

Fig. 9. Simulated vs. measured shift in saturation reverse drain current for  $V_{\rm d} < V_{\sigma}$ .

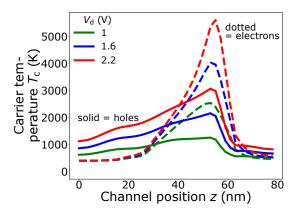

holes generated by I/I gain energy and can create defects deeper in the channel, as suggested by Tyaginov *et al.* [21]. To illustrate this idea, we performed hydrodynamic (HD) simulations of the nanowire FET including I/I. Contrary to solving the subband BTE, HD simulations only give the average carrier energy (temperature) and not the full carrier energy DF. According to the HD simulations (Fig. 12), the hole temperature profile is more 'smeared out' towards the source compared to the electron temperature profile. This points to energetic holes being more spread out over the channel compared to electrons and is consistent with the above idea of holes being able to create defects closer to the source.

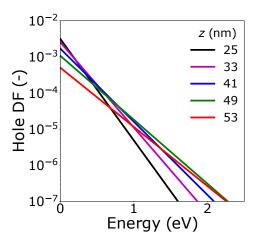

To model the ability of holes to generate traps, an approximated hole DF represented by a heated Maxwellian distribution was employed (Fig. 13):

$$f(\epsilon, z) = C(z) \exp\left(-\frac{\epsilon}{k_{\rm B}T_{\rm h}(z)}\right)$$

(3)

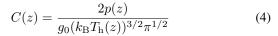

where  $T_{\rm h}$  is the average hole temperature obtained from the HD simulations. The normalization constant C was fixed by requiring that the heated Maxwellian represents the hole concentration p from the simulations:

Fig. 10. Simulation of the shift in saturation drain current  $\Delta I_{\rm d,sat}$  after stress over the full  $(V_{\rm g},V_{\rm d})$  bias space. Only shifts up to 10% are shown. The white dots are the bias points at which stress was applied and the white hatched area indicates degradation which is seen in the measurements [3], but is missing in the simulations.

Fig. 11. Simulated interface defect profiles  $N_{\rm it}$  along the channel for different  $V_{\rm d}$  at  $V_{\rm g}=0.7$  V. The vertical dotted lines indicate the borders between the source extension, channel and drain extension regions. For this low gate voltage, the defect profile is located only in the drain extension and does not enter the channel, causing limited degradation to the post-stress I-V.

where a parabolic DOS  $g(\epsilon)=g_0\sqrt{\epsilon}$  was used for the holes. This analytic DF for the holes generated by I/I was then considered together with the numerical electron DF obtained before (Fig. 3) to calculate the density of interface defects (Fig. 14). Although a heated Maxwellian shape is a too crude approximation for the DF [22], it can be useful to make a first, qualitative estimate of the effect of I/I on the  $N_{\rm it}$ -profile in the region of missing degradation. For this estimate, the AB and MVE acceleration integrals were calculated as in Bina  $et\ al.$  [8] instead of using the quantum mechanical method described above to simplify the calculation.

In the high  $V_{\rm d}$ , low  $V_{\rm g}$  corner of the bias space (i.e. the region of missing degradation), the generated holes add a large contribution to the interface defect profile (Fig. 14). The so-obtained defect density profiles were then used to simulate the

Fig. 12. Average electron and hole temperature (= energy) obtained from hydrodynamic simulations of the NW FET including impact ionization for  $V_{\rm g}=0.4$  V. The hole temperature profile is more 'smeared out' towards the source, indicating the presence of energetic holes at the source side which create defects there.

Fig. 13. Heated Maxwellian hole DFs at different positions z along the channel for  $V_{\rm g}=0.4$  V,  $V_{\rm d}=2.2$  V. The temperature of the heated Maxwellians is taken equal to the carrier temperature obtained from the hydrodynamic simulations with impact ionization.

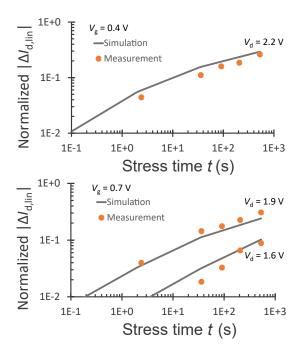

time evolution of the linear drain current degradation for three bias points with missing degradation. To obtain the correct time slope, it is necessary to consider the dispersion of the activation energy  $E_{\rm a}$  for Si-H bond rupture, as discussed by Bina *et al.* [8]. This ingredient was not used for the previous results ( $V_{\rm d} < V_{\rm g}$ ) and additionally increases the interface defect density in the high  $V_{\rm d}$ , low  $V_{\rm g}$  region (Fig. 14). With the inclusion of the  $E_{\rm a}$  dispersion and the approximate treatment of I/I, a reasonable agreement between measurements and simulations could be obtained for these bias points (Fig. 15).

# IV. CONCLUSIONS

We performed modeling of HCD in NW FETs based on calculations of carrier energy DFs. To obtain these DFs, we employed both the full solution of the BTE and the simplified HD scheme. The latter was used to model the effect of I/I. For  $V_{\rm d} < V_{\rm g}$ , the solution of the BTE without I/I gives a reasonable agreement with measured HCD data. For low  $V_{\rm g}$ ,

Fig. 14. Simulated interface defect density  $N_{\rm it}$  after inclusion of i) impact ionization (I/I) with a heated Maxwellian as DF for the generated holes and ii) dispersion of the activation energy  $E_{\rm a}$  for Si-H bond breakage in the model (green curve). The simulation was done for stress voltages  $V_{\rm g} = 0.4$  V,  $V_{\rm d} = 2.2$  V and a stress time t = 530 s. For comparison, the  $N_{\rm it}$  profiles obtained when adding only one or none of the two changes (I/I and/or  $E_{\rm a}$  dispersion) are also shown.

Fig. 15. Simulation of the time evolution of the degradation of linear drain current for three  $(V_{\rm g},V_{\rm d})$  points in the region where degradation was missing (see Fig. 10). For these bias points, the inclusion of impact ionization and the dispersion of the Si-H bond breakage energy  $E_{\rm a}$  gives a reasonable agreement between measurements and simulations.

high  $V_{\rm d}$  combinations, the addition of I/I and the dispersion of the activation energy for Si-H bond breakage add a significant contribution to the interface defect profile and are needed to reproduce the measured HCD data.

### ACKNOWLEDGMENT

Michiel Vandemaele is supported by a PhD Fellowship of the Research Foundation - Flanders (application number 11A3619N). Stanislav Tyaginov is supported by the European Union's Horizon 2020 research and innovation programme (Marie Sklodowska-Curie grant agreement number 794950).

### REFERENCES

- S. Novak et al., "Transistor aging and reliability in 14 nm tri-gate technology," in 2015 IEEE International Reliability Physics Symposium (IRPS), pp. 2F-2, IEEE, 2015.

- [2] A. Rahman, J. Dacuna, P. Nayak, G. Leatherman, and S. Ramey, "Reliability studies of a 10 nm high-performance and low-power CMOS technology featuring 3<sup>rd</sup> generation finFET and 5<sup>th</sup> generation HK/MG," in 2018 IEEE International Reliability Physics Symposium (IRPS), pp. 6F–4, IEEE, 2018.

- [3] A. Chasin et al., "Complete degradation mapping of stacked gate-all-around Si nanowire transistors considering both intrinsic and extrinsic effects," in 2017 IEEE International Electron Devices Meeting (IEDM), pp. 7–1, IEEE, 2017.

- [4] E. Bury et al., "Self-heating-aware CMOS reliability characterization using degradation maps," in 2018 IEEE International Reliability Physics Symposium (IRPS), pp. 2A–3, IEEE, 2018.

- [5] A. Laurent et al., "Hot carrier degradation in nanowire transistors: physical mechanisms, width dependence and impact of self-heating," in 2016 IEEE Symposium on VLSI Technology, pp. 1–2, IEEE, 2016.

- [6] W. McMahon, K. Matsuda, J. Lee, K. Hess, and J. Lyding, "The effect of a multiple carrier model of interface trap generation on lifetime extraction for MOSFETs," in *Proc. International Conference* on Modeling and Simulation of Microsystems (MSM), vol. 1, pp. 576– 579, 2002.

- [7] S. Tyaginov and T. Grasser, "Modeling of hot-carrier degradation: physics and controversial issues," in 2012 IEEE International Integrated Reliability Workshop Final Report (IIRW), pp. 206–215, IEEE, 2012.

- [8] M. Bina et al., "Predictive hot-carrier modeling of n-channel MOS-FETs," *IEEE Transactions on Electron Devices*, vol. 61, no. 9, pp. 3103– 3110, 2014.

- [9] S. Tyaginov et al., "Understanding and modeling the temperature behavior of hot-carrier degradation in SiON nMOSFETs," IEEE Electron Device Letters, vol. 37, no. 1, pp. 84–87, 2016.

- [10] A. Makarov et al., "Hot-carrier degradation in finFETs: modeling, peculiarities, and impact of device topology," in 2017 IEEE International Electron Devices Meeting (IEDM), pp. 13–1, IEEE, 2017.

- [11] S. Reggiani et al., "Characterization and modeling of electrical stress degradation in STI-based integrated power devices," Solid-State Electronics, vol. 102, no. 12, p. 25–41, 2014.

- [12] H. Mertens et al., "Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates," in 2016 IEEE Symposium on VLSI Technology, pp. 1–2, IEEE, 2016.

- [13] H. Mertens et al., "Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates," in 2016 IEEE International Electron Devices Meeting (IEDM), pp. 19–7, IEEE, 2016.

- [14] http://www.globaltcad.com/en/products/minimos-nt.html.

- [15] M. Vandemaele et al., "Distribution function based simulations of hotcarrier degradation in nanowire FETs," in 2018 IEEE International Integrated Reliability Workshop (IIRW), IEEE, 2018.

- [16] F. M. Bufler, K. Miyaguchi, T. Chiarella, N. Horiguchi, and A. Mocuta, "On the ballistic ratio in 14 nm-node finFETs," in 2017 47<sup>th</sup> European Solid-State Device Research Conference (ESSDERC), pp. 176–179, IEEE, 2017.

- [17] http://www.globaltcad.com/en/products/gts-nano-device-simulator.html.

- [18] M. Karner *et al.*, "Vertically stacked nanowire MOSFETs for sub-10 nm nodes: advanced topography, device, variability, and reliability simulations," in *2016 IEEE International Electron Devices Meeting* (*IEDM*), pp. 30–7, IEEE, 2016.

- [19] C. Guerin, V. Huard, and A. Bravaix, "General framework about defect creation at the Si/SiO<sub>2</sub> interface," *Journal of Applied Physics*, vol. 105, no. 11, p. 114513, 2009.

- [20] G. Rzepa et al., "Complete extraction of defect bands responsible for instabilities in n and pfinFETs," in 2016 IEEE Symposium on VLSI Technology, pp. 1–2. IEEE, 2016.

- Technology, pp. 1–2, IEEE, 2016.

[21] S. Tyaginov et al., "Secondary generated holes as a crucial component for modeling of HC degradation in high-voltage n-MOSFET," in 2011 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 123–126, IEEE, 2011.

- [22] T. Grasser, H. Kosina, and S. Selberherr, "Influence of the distribution function shape and the band structure on impact ionization modeling," *Journal of Applied Physics*, vol. 90, no. 12, pp. 6165–6171, 2001.