### **PAPER • OPEN ACCESS**

# Reliability of scalable ${\rm MoS}_2$ FETs with 2 nm crystalline ${\rm CaF}_2$ insulators

To cite this article: Yury Yu Illarionov et al 2019 2D Mater. 6 045004

View the <u>article online</u> for updates and enhancements.

# **2D** Materials

#### **OPEN ACCESS**

#### RECEIVED

21 March 2019

# REVISED

10 May 2019

ACCEPTED FOR PUBLICATION

11 June 2019

# PUBLISHED

1 July 2019

Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence.

Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### **PAPER**

# Reliability of scalable MoS<sub>2</sub> FETs with 2 nm crystalline CaF<sub>2</sub> insulators

Yury Yu Illarionov<sup>1,2</sup>, Alexander G Banshchikov<sup>2</sup>, Dmitry K Polyushkin<sup>3</sup>, Stefan Wachter<sup>3</sup>, Theresia Knobloch<sup>1</sup>, Mischa Thesberg<sup>1</sup>, Mikhail I Vexler<sup>2</sup>, Michael Waltl<sup>1</sup>, Mario Lanza<sup>4</sup>, Nikolai S Sokolov<sup>2</sup>, Thomas Mueller<sup>3</sup> and Tibor Grasser<sup>1</sup>

- <sup>1</sup> Institute for Microelectronics (TU Wien), Gusshausstrasse 27–29, 1040 Vienna, Austria

- <sup>2</sup> Ioffe Physical-Technical Institute, Polytechnicheskaya 26, 194021 St-Petersburg, Russia

- <sup>3</sup> Institute for Photonics (TU Wien), Gusshausstrasse 27–29, 1040 Vienna, Austria

- <sup>4</sup> Institute of Functional Nano & Soft Materials, Soochow University, 199 Ren-Ai Road, Suzhou 215123, People's Republic of China

E-mail: illarionov@iue.tuwien.ac.at and grasser@iue.tuwien.ac.at

Keywords: reliability, transistor, calcium fluoride, MoS2, hysteresis, charged defects

Supplementary material for this article is available online

#### **Abstract**

Two-dimensional (2D) semiconductors are currently considered a very promising alternative to Si for channel applications in next-generation field-effect transistors of sub-5 nm designs. However, their huge potential cannot be fully exploited owing to a lack of competitive insulators which are required to effectively separate the channel from the gate, while being scalable down to few nanometers thicknesses. Recently we have made an attempt at addressing this issue by using crystalline CaF<sub>2</sub> insulators and demonstrated competitive MoS<sub>2</sub> devices with the insulator thickness of only about 2 nm. Here we report a detailed study of the performance, reliability and thermal stability of these devices. We demonstrate that, in contrast to SiO<sub>2</sub> and other amorphous oxides, CaF<sub>2</sub> has a very low density of insulator defects which are responsible for the hysteresis and long-term drifts of the transistor characteristics. At the same time, CaF<sub>2</sub> exhibits smaller leakage currents and higher electric stability compared to hBN. By comparing our MoS<sub>2</sub> transistors with CaF<sub>2</sub> fabricated using MoS<sub>2</sub> films of different quality, we show that the major limitations on the performance and reliability of these devices come from the bare channel rather than from the superior  $CaF_2$  insulator. Finally, we perform the first study of degradation mechanisms only observed for tunnel-thin gate insulators in 2D devices. While these degradation mechanisms are similar for hBN and CaF<sub>2</sub>, they are less pronounced in CaF<sub>2</sub>. Our results therefore present a solution to a very important roadblock on the way towards fully scalable 2D nanoelectronics with competitive performance and reliability.

Next-generation field-effect transistors (FETs) with two-dimensional (2D) channel materials provide a means to overcome the limitations of Si technologies and enable scaled channel geometries below 5 nm, thereby extending Moore's law. Starting from the first graphene FETs [1, 2], several groups have fabricated functional FETs with other 2D materials. Among them most attention has been paid to transition metal dichalcogenides such as MoS<sub>2</sub> [3–8], MoSe<sub>2</sub> [9], MoTe<sub>2</sub> [10], WS<sub>2</sub> [11] and WSe<sub>2</sub> [12, 13]. In addition, successful demonstrations of FETs with more exotic materials such as black phosphorus [14, 15] and even silicene [16] can be also found in the literature. Up to now, MoS<sub>2</sub> FETs have been shown to exhibit the best performance, with sub-threshold swing (SS) [8] values

down to 69 mV dec<sup>-1</sup> and on/off current ratios [6] up to  $10^{10}$ . Furthermore, several attempts on circuit integration of MoS<sub>2</sub> FETs have been also reported [17–19].

Despite all recent progress achieved on 2D FET prototypes, the transition towards commercial 2D FETs still remains a challenge. The main reasons for this are the absence of fully scalable fabrication process flows and a poor reliability of the currently available devices, which are mainly due to the absence of competitive insulators for these new technologies. For instance, conventional oxides, such as SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, are amorphous when grown in thin layers and contain numerous defects. This leads to a poor quality of the interfaces with 2D channels and thus strongly

degraded device performance and reliability [20–22]. On the other side, the use of 2D hexagonal boron nitride (hBN), which is often considered to be the best insulator for future 2D devices [23, 24], has indeed resulted in significantly enhanced channel mobilities [25] and improved reliability [21, 26], owing to a van der Waals interface between hBN and 2D semiconductors. However, hBN has a small out-of-plane low-frequency dielectric constant of either 3.76 [27] or 5.06 [28], a small bandgap of about 6 eV [29] and unfortunate band offsets to most 2D materials. As such, hBN appears to be barely suitable for the use in ultra-scaled 2D devices with equivalent oxide thicknesses (EOT) below 1 nm (corresponding to a physical thickness of below 1.3 nm in hBN), as it will lead to excessive thermionic and tunneling leakage currents.

In our recent work [30] we have made an attempt to overcome this bottleneck and reported functional MoS<sub>2</sub> FETs with crystalline calcium fluoride (fluorite, CaF<sub>2</sub>) of only about 2 nm thickness, while reaching SS down to 90 mV dec<sup>-1</sup> and on/off current ratios up to 10<sup>7</sup> already for the first prototypes. In contrast to conventional oxides and hBN, CaF2 insulators satisfy all the conditions required for scalable 2D electronics, a huge bandgap ( $E_g = 12.1 \text{ eV}$ ) and a comparably high dielectric constant ( $\varepsilon = 8.43$ ) [31]. This allows us to achieve tunnel leakage currents which are comparable to those through the typically used high-k oxides even for sub-1 nm EOT, while outperforming hBN and SiO<sub>2</sub> by several orders of magnitude [30, 32]. At the same time, the inert CaF<sub>2</sub>(111) surface forms a quasi van der Waals interface [33] with 2D materials (figure 1(a)), which is of much higher quality than the interfaces between 2D materials and currently used oxides. This, in particular, makes heteroepitaxy of 2D materials on CaF<sub>2</sub>(111) possible, as already confirmed for MoSe<sub>2</sub> [34] and MoTe<sub>2</sub> [35]. Finally, the layer thickness and crystalline quality of CaF<sub>2</sub> can be controlled onsite when growing this material on Si(111) substrates using molecular beam epitaxy (MBE), see more details in the methods section.

While opening a way to the further development of 2D FETs and other emerging devices with various fascinating fluoride materials [36-38], we argue that estimation of the real potential of any new technology requires proper understanding of their reliability. In particular, all previously reported 2D FETs suffer from charge trapping by insulator defects. This charge trapping appears as a fast sweep hysteresis [20, 21, 39–42] and long-term drifts of the gate transfer characteristics [21, 43–46], which are known from Si technologies as bias-temperature instabilities (BTI) [47, 48]. Here we examine  $CaF_2(2 nm)/MoS_2$  FETs similar to those reported in our previous work [30] and pay particular attention to their reliability. By comparing the results for CaF<sub>2</sub>/MoS<sub>2</sub> FETs with different channel quality and their counterparts with hBN and SiO<sub>2</sub>, we demonstrate that in devices with CaF2 insulators the main reliability, performance and thermal stability limitations are

due to the bare MoS<sub>2</sub> channel and its interaction with adsorbates. As for the CaF<sub>2</sub> insulator, we show that it contains a very small number of defects and starts to degrade only under extreme electrical overloads above 7 MV cm<sup>-1</sup>, which is far above the requirements for normal operation of our devices. The results provide additional confirmation that CaF<sub>2</sub> is a very promising insulator for 2D electronics.

# 1. CaF<sub>2</sub>/MoS<sub>2</sub> devices

Our devices are back-gated bilayer MoS<sub>2</sub> FETs with a channel grown by chemical vapour deposition (CVD) [49] and transferred onto the CaF<sub>2</sub>/Si(111) substrates using the method presented in [50]. CaF<sub>2</sub> films of about 6–7 monolayers (ML, 1 ML =0.315 nm) have been grown on atomically clean Si(111) surface using our established MBE process [51], which is a fully scalable technology. The thickness of CaF<sub>2</sub> was confirmed to be about 2 nm using transmission electron microscope (TEM) [30]. The source/drain contact pads are made of Ti/Au and the channel lengths and widths are between 400 and 800 nm for different devices (see more details in the methods section).

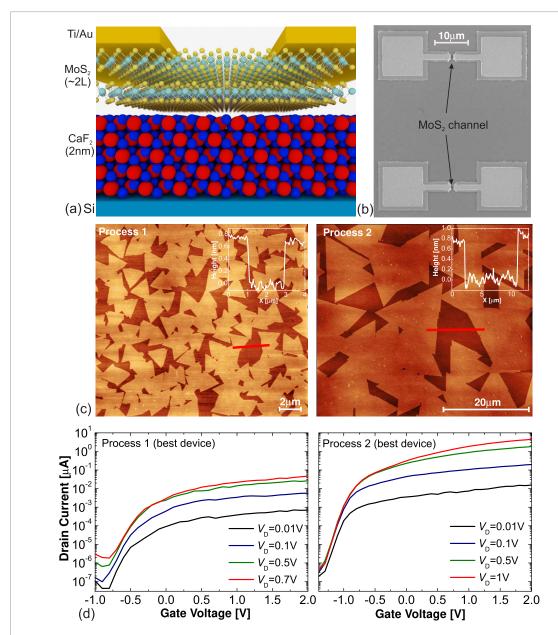

The schematic channel cross-section of our CaF<sub>2</sub>/ MoS<sub>2</sub> FETs is shown in figure 1(a). As the layered structure of CaF<sub>2</sub> with its F-Ca-F monolayers is rather similar to that of 2D materials, the interface with MoS<sub>2</sub> is well-defined and contains a quasi van der Waals gap [33]. Most importantly, a F-terminated atomically flat surface does not provide any dangling bonds, which are typically present in 2D FETs with amorphous oxides. In figure 1(b) we show the scanning electron microscope (SEM) image of our devices which consist of two contact pads connected to the MoS2 channel in between. We fabricated two sets of devices on nearly identical CaF<sub>2</sub>/Si(111) substrates but with MoS<sub>2</sub> films of differently adjusted CVD growth processes. Namely, in our first CVD growth experiments (Process 1) the control of the sulfur concentration in the chamber was limited, and during the next experiments (Process 2) this has been considerably improved. As shown by atomic force microscope (AFM) images in figure 1(c), the quality of the Process 1 MoS<sub>2</sub> films is considerably lower than that of Process 2. This appears in nearly ten times larger grain sizes of MoS<sub>2</sub> in Process 2, which is known to be an important figure of merit for the quality of CVD-grown films [52–54]. Namely, the film with the larger grain size contains less grain boundaries, which leads to a smaller number of intrinsic defects and improved electrical properties. In figure 1(d) we compare the gate transfer  $(I_D - V_G)$  characteristics of two best (among few tens) devices fabricated using both processes. In agreement with the results of [53], by using MoS<sub>2</sub> films of Process 2 we achieve more competitive devices with a maximum measured on current of about 5  $\mu$ A (or about 6  $\mu$ A  $\mu$ m<sup>-1</sup> if normalized to the channel width), which is two orders of magnitude larger than for the best Process 1 FET. This is likely

Figure 1. (a) Atomistic structure of the channel area of our CaF<sub>2</sub>/MoS<sub>2</sub> FETs with the quasi van der Waals interface between F-terminated CaF<sub>2</sub>(111) and MoS<sub>2</sub>. (b) SEM image of two devices. (c) AFM images of the MoS<sub>2</sub> films grown by CVD on sapphire obtained from the substrate areas where the growth remains in the nucleation stage and the film is not formed completely. The insets show height profiles measured along the red lines, indicating monolayer structure of triangular MoS<sub>2</sub> grains. For a more optimized growth (Process 2) MoS<sub>2</sub> grains are nearly ten times larger than those of Process 1, which results in a considerable improvement of the film quality. Note that in the areas with continuous MoS<sub>2</sub> layer the grains are slightly smaller for both processes [30]. (d) The  $I_D - V_G$  characteristics of the two best devices fabricated using both processes from several tens each. The device with the MoS<sub>2</sub> channel of Process 2 exhibits a considerably better performance.

because with channel dimensions between 400 and 800 nm, some devices are located relatively far away from the grain boundaries of  $10-15~\mu m$  sized MoS<sub>2</sub> grains, which is barely possible for the Process 1 films with MoS<sub>2</sub> grains of only about 1  $\mu m$ .

### 2. Results and discussion

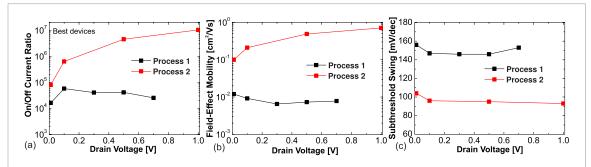

In figure 2 we compare the performance characteristics of the best FETs at different drain voltages. For the Process 2 devices the best values of the on/off current ratio, field-effect mobility and SS are respectively 10<sup>7</sup>, 0.7 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and 93 mV dec<sup>-1</sup>, which is considerably better than the maximum

values of their Process 1 counterparts. At the same time, the performance of the Process 1 device starts to degrade already for  $V_{\rm D}$  above 0.1V, while the Process 2 device reaches the performance maximum at higher  $V_{\rm D}$ . Since both devices were fabricated using nearly identical CaF<sub>2</sub> layers, all these results allow us to conclude that, owing to a defect-free nature of CaF<sub>2</sub> surface, in our CaF<sub>2</sub>/MoS<sub>2</sub> FETs the major performance limitations are coming from the quality of the MoS<sub>2</sub> channel. Especially strong improvement is achieved in SS, which is mainly degraded by defects in the MoS<sub>2</sub> channel. Therefore, for CaF<sub>2</sub>/MoS<sub>2</sub> FETs with defect-free MoS<sub>2</sub> films we expect SS to be more close to 60 mV dec<sup>-1</sup>.

2D Mater. **6** (2019) 045004 Y Yu Illarionov et al

Figure 2. The on/off current ratio (a), field-effect mobility (b) and subthreshold swing (c) of the devices from figure 1(c) versus the drain voltage. For the device from Process 2 all values are considerably better. An increase of the on/off current ratio versus  $V_D$  confirms both the high quality of the MoS<sub>2</sub> channel, which allows to achieve a high degree of current control, and good insulator properties of CaF<sub>2</sub>, which suppress the gate leakage even for higher  $V_D$ .

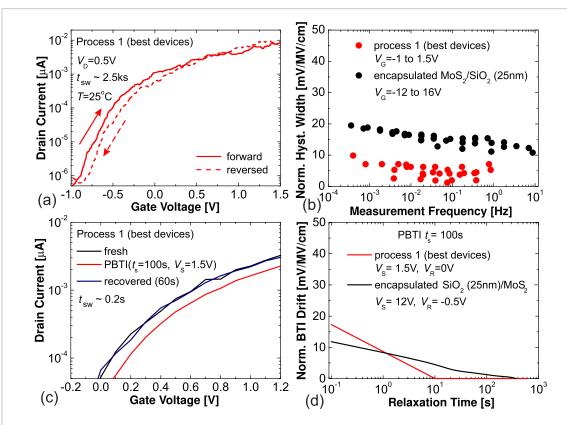

Next we proceed with the reliability characterization of Process 1 transistors. From about fifty of these devices, not more than five exhibited a distinctively better performance. As shown in figure 3, the best CaF<sub>2</sub>/MoS<sub>2</sub> FETs fabricated using small grain MoS<sub>2</sub> films already exhibit a competitive reliability. For instance, the hysteresis width in these devices does not exceed 0.15 V (figure 3(a)) even for sweep times  $t_{sw}$  of several kiloseconds. As suggested previously [21], we normalize the hysteresis widths measured using different  $t_{\text{sw}}$  by the insulator field factor  $K = \Delta V_{\text{G}}/d_{\text{ins}}$ , with  $\Delta V_{\rm G}$  being the width of the sweep range and  $d_{\rm ins}$ the insulator thickness, and plot them versus the measurement frequency  $f = 1/t_{sw}$ . As shown in figure 3(b), the hysteresis in our CaF<sub>2</sub>/MoS<sub>2</sub> FETs is smaller than that of SiO<sub>2</sub>(25 nm)/MoS<sub>2</sub> transistors reported in our previous work [6]. This is quite remarkable since in the latter devices the MoS2 films were grown directly on the SiO<sub>2</sub> substrate [55] and were thus of much higher quality [7] with grain size exceeding 100  $\mu$ m. Also note that these reference devices used a high-quality Al<sub>2</sub>O<sub>3</sub> encapsulation which has been shown to reduce the hysteresis width.

The small hysteresis observed is fully consistent with the weak positive BTI (PBTI) degradation seen in these devices. In figures 3(c) and (d) we show that even after PBTI stress at a gate voltage of  $V_S = 1.5 \text{ V}$  (corresponding to an insulator field of 7.5 MV cm $^{-1}$ ) the degradation is fully recoverable within a maximum tens of seconds. This is in contrast to encapsulated SiO<sub>2</sub>/ MoS<sub>2</sub> FETs, where the recovery at a certain recovery voltage  $V_R$  takes up to a kilosecond after a weaker 4.8  $MV \text{ cm}^{-1}$  stress (figure 3(d)). The latter suggests that while in SiO<sub>2</sub>/MoS<sub>2</sub> FETs with its amorphous oxide charge trapping is due to oxide defects with widely distributed time constants [56], in crystalline CaF<sub>2</sub> a similar distribution of defects is missing. As such, in CaF<sub>2</sub>/MoS<sub>2</sub> devices the main contribution likely comes from the defects in MoS2 and adsorbates (e.g. water molecules) bonded at the CaF<sub>2</sub>/MoS<sub>2</sub> interface, which are known to be very fast [42]. However, stressing of CaF<sub>2</sub> at even higher electric fields (up to 15 MV cm<sup>-1</sup>) sometimes leads to activation of other failure mechanisms, which are also present in MoS<sub>2</sub> FETs with

about 4 nm thick hBN insulators and in our Process 2 devices with CaF<sub>2</sub> (see figures S1–S3 in the supporting information (SI) (stacks.iop.org/TDM/6/045004/mmedia)). These issues are likely associated with the creation of new defects in tunnel-thin gate insulators subjected to strong electrical stress and not related to the channel quality.

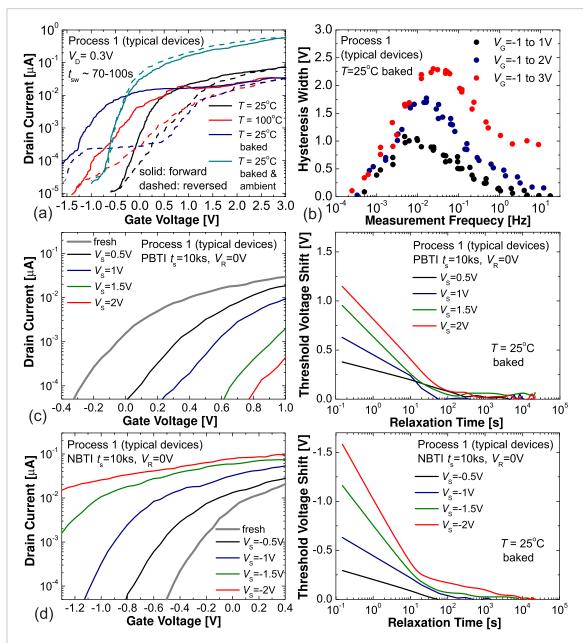

In order to further understand the impact of the MoS<sub>2</sub> channel quality on the performance and reliability of our CaF<sub>2</sub>/MoS<sub>2</sub> FETs, we analyze more typical devices of Process 1. In contrast to the best devices, these devices likely contain several grain boundaries within their channel, which results in degraded performance. As shown in figure 4(a), in typical Process 1 devices a considerable hysteresis is observed. Although this hysteresis is not sizably reduced at T = 100 °C, no increase is observed either. This would be in contradiction with thermally activated charge trapping by insulator defects and suggests that the contribution comes from adsorbates interacting with channel defects [41], which serve as energetically favorable attachment sites. These channel defects are likely S vacancies, which in these devices should be mostly concentrated near the grain boundaries [57]. At the same time, the hysteresis considerably increases after 5h at T = 100 °C. Also, we observe a transformation of the  $I_D - V_G$  characteristics and a negative shift of the threshold voltage  $V_{\rm th}$ , which can be explained by thermally enhanced creation of S vacancies in MoS<sub>2</sub> [57-59] (for more details about the measurement history of this device see figure S4 in the SI). These S vacancies can be created either by chemical reaction of bare MoS<sub>2</sub> with residual H<sub>2</sub> in the vacuum chamber [58] or by intrinsic mechanism catalyzed by the grain boundaries, which can be involved in complex reaction pathways [57]. As such, we identify the interaction of preexisting and newly created S vacancies in MoS2 with adsorbed water molecules [41] as the most possible reason for the hysteresis. As was reported previously [41], the typical time constants of these processes are tens of seconds. While being consistent with our results (figure 4), these values are considerably larger than the time constants of a direct charge trapping of carriers by channel defects, which therefore can not contribute to the

2D Mater. **6** (2019) 045004 Y Yu Illarionov *et al*

**Figure 3.** (a) The slow sweep  $I_D - V_G$  characteristic measured for one of the best Process 1 devices. (b) The normalized hysteresis widths for our bare channel CaF<sub>2</sub>/MoS<sub>2</sub> FETs are even smaller than for Al<sub>2</sub>O<sub>3</sub> encapsulated SiO<sub>2</sub>/MoS<sub>2</sub> FETs reported in our previous work [6]. (c) The fast sweep  $I_D - V_G$  characteristics measured before and after a  $t_s = 100$  s PBTI stress. (d) In contrast to SiO<sub>2</sub>/MoS<sub>2</sub> FETs, the degradation is completely recoverable already within the first ten seconds. The measured BTI drifts are normalized by the insulator fields.

hysteresis and BTI [42]. Interestingly, air exposure of a previously baked device for several minutes leads to an improvement of the device performance and suppression of the hysteresis, which suggests that created S vacancies become substituted (e.g. by oxygen atoms [60]) and thus excluded from the processes causing the hysteresis.

In figure 4(b) we show the hysteresis width plotted versus the measurement frequency as measured for a baked device prior to air exposure. We observe a clear maximum as predicted in our previous work [21], where a similar behaviour has been also observed for MoS<sub>2</sub> FETs with hBN insulators. While this feature has been also predicted for charge trapping by oxide defects [21], for oxide/2D FETs the maximum is typically not observable in experiments because of the very broad distribution of time constants. In contrast, the interaction of MoS<sub>2</sub> (and probably hBN [21]) defects with adsorbates should be a much faster process compared to charge trapping by slow oxide traps, which leads to a clear maximum already at moderate sweep frequencies. Interestingly, a decrease of the hysteresis width for slow sweeps is accompained by a strong transformation of the  $I_D - V_G$  characteristics (see figure S5 in the SI). After baking this issue is observed even for the best devices discussed above, which indicates an overall poor thermal stability of the MoS<sub>2</sub> film with small grain size (see figure S6 in the SI).

PBTI and negative BTI (NBTI) in these devices appear to be due to the same fast  $MoS_2$  defects as the hysteresis. In figures 4(c) and (d) we show that the dynamics of these issues are dominated by the fast trapping component, which is rather strong (especially after baking) but tends to recover completely even after a  $10 \, \text{MV cm}^{-1}$  stress for  $10 \, \text{ks}$ . Following the work of [41], we suggest that during NBTI stress (or negative  $V_G$  during the hysteresis sweep) the S vacancies become occupied by positive  $H^+$  ions of water molecules, and during PBTI (or positive  $V_G$  during the hysteresis sweep) by negative  $O^{2-}$  ions. As soon as the stress is removed, the number of S vacancies occupied by  $O^{2-}$  and  $H^+$  ions quickly returns to the equilibrium at the recovery voltage  $V_R = 0$ .

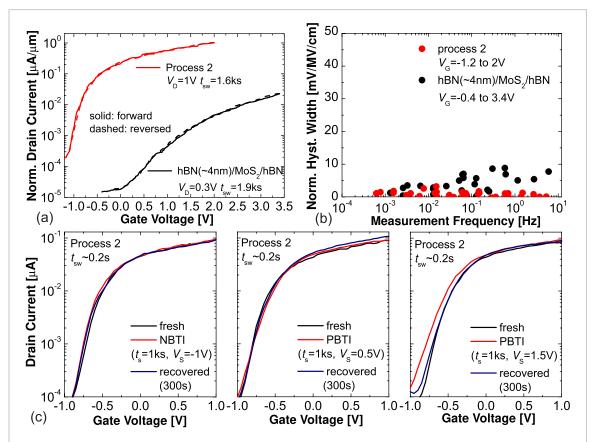

We proceed with the analysis of the reliability of our Process 2 CaF<sub>2</sub>(2 nm)/MoS<sub>2</sub> FETs and compare our results with those obtained for sandwiched hBN/MoS<sub>2</sub>/hBN devices with exfoliated channel and gate insulator thickness of about 4 nm. In figure 5(a) we show that the hysteresis in both devices is negligible even for kilosecond sweep times, while the performance of the devices with CaF<sub>2</sub> is considerably better (for more details see figure S1 in the SI). At the same time, a more negative threshold voltage of the devices with CaF<sub>2</sub> is likely because of their bare channel, which allows accumulation of positive fixed charges (e.g. adsorbates on top of the channel or passive S vacan-

**Figure 4.** (a) The  $I_D - V_G$  characteristics measured for a typical Process 1 device before, during and after baking at T = 100 °C. The hysteresis increases after baking and becomes suppressed by subsequent ambient exposure. (b) The hysteresis width measured after baking at T = 100 °C exhibits a clear maximum versus f. (c) Evolution of the  $I_D - V_G$  characteristics after subsequent PBTI stresses with increasing  $V_S$  and corresponding recovery traces. (d) Related results for NBTI measured on the same device. In both cases the degradation is dominated by fast defects which are likely located in MoS<sub>2</sub> and interact with water adsorbates.

cies). As shown in figure 5(b), the hysteresis in our  $CaF_2/MoS_2$  FETs is not observed even for faster sweeps, while the device with hBN exhibits some signs of fast trap contribution which agrees well with our previous observations [21]. These results confirm the high quality of both the  $CaF_2/MoS_2$  interface and the large grain  $MoS_2$  film of our Process 2.

In figure 5(c) we show the evolution of the  $I_D - V_G$  characteristics of our Process 2 devices under different bias stress conditions. If the applied insulator field is less than 5 MV cm<sup>-1</sup>, both NBTI and PBTI degradations are weak. This further confirms the defect-free nature of the CaF<sub>2</sub>/MoS<sub>2</sub> interface and the absence of active fast defects in the Process 2 MoS<sub>2</sub> films, which is different from their Process 1 counterparts dis-

cussed above. However, a PBTI stress at 7.5 MV cm $^{-1}$  leads to a recoverable negative shift of the threshold voltage, which can be attributed to the creation of new defects in CaF $_2$  while approaching the typically assumed breakdown field of about 10 MV cm $^{-1}$ . As soon as the insulator field and/or the stress time are further increased, this kind of degradation becomes stronger and is also observed to be weakly recoverable (see figures S2 and S3 in the SI). However, the insulator fields and stress times required to observe such a negative shift can be different for different devices and are likely given by the local CaF $_2$  thickness and quality. A similar degradation with a negative shift after PBTI stress has been observed also for our devices with Process 1 MoS $_2$  films and hBN( $\sim$ 4 nm)/MoS $_2$ /hBN FETs.

**Figure 5.** (a) The  $I_D-V_G$  characteristics of our Process 2 CaF $_2$ (2 nm)/MoS $_2$  and hBN( $\sim$ 4 nm)/MoS $_2$ /hBN FETs ( $I_D$  is normalized by the channel width) exhibit a negligible hysteresis even for kilosecond sweep times. (b) The hysteresis widths normalized by the insulator field factor are also small for both technologies, though some fast traps are likely present in the hBN layer. (c) BTI degradation and recovery in our Process 2 CaF $_2$ (2 nm)/MoS $_2$  FETs. NBTI stressing at  $V_S=-1$  V (insulator field of -5 MV cm $^{-1}$ ) and PBTI at  $V_S=0.5$  V (insulator field of 2.5 MV cm $^{-1}$ ) result in negligible degradation. PBTI at  $V_S=1.5$  V (insulator field of 7.5 MV cm $^{-1}$ ) causes a small negative shift of the device characteristics, which is fully recoverable at  $V_R=-0.5$  V.

This allows us to conclude that this issue is common for all devices with scaled gate insulators. Remarkably,  $CaF_2$  appears to be more stable with respect to strong electrical stress than hBN (see figure S3 in the SI). It is worth noting that the results of figure 5 are the closest to the reliability thresholds expected for mature  $CaF_2/MoS_2$  FETs, while figures 3 and 4 show that the potential of these devices can be concealed by the dominating impact of channel defects and adsorbates. The latter can be addressed by further improvement of the  $MoS_2$  growth techniques and the use of suitable encapsulation schemes.

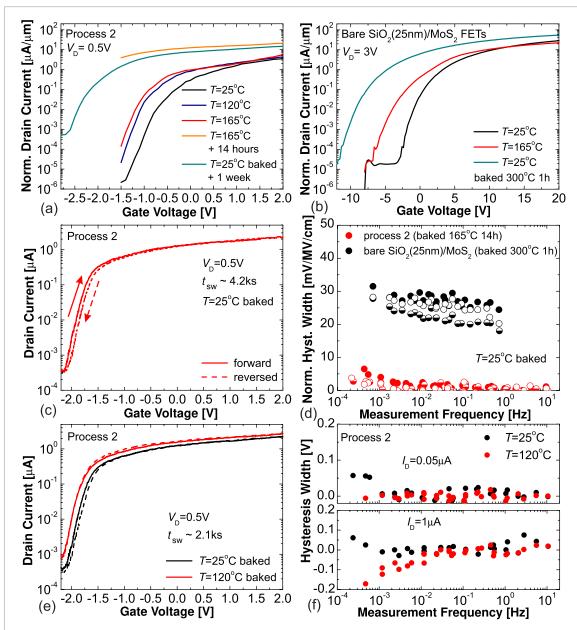

Next we examine the thermal stability of our Process 2 CaF<sub>2</sub>/MoS<sub>2</sub> FETs. Similarly to their Process 1 counterparts, at high temperature these devices exhibit a negative shift of  $V_{\rm th}$  (figure 6(a)). After 14 h at 165 °C,  $V_{\rm th}$  becomes more close to the critical stress voltages allowed for 2 nm CaF<sub>2</sub> films, and partially recovers when the temperature is returned to 25 °C. This negative  $V_{\rm th}$  shift is very similar to that studied previously in our SiO<sub>2</sub>(25 nm)/MoS<sub>2</sub> FETs [6,61] (figure 6(b)). The latter devices have been baked even at 300 °C, which was possible due to the more stable MoS<sub>2</sub> films with 100  $\mu$ m grain size (against 10–15  $\mu$ m in our Process 2) grown by CVD directly on top of the SiO<sub>2</sub> substrate [7,55]. As has been shown for the SiO<sub>2</sub>/MoS<sub>2</sub> devices (see figure S7 in the SI), a weakly recoverable

negative shift of  $V_{\rm th}$  is a typical feature of bare channel devices. In contrast, encapsulated devices exhibit a fully reversible transformation of the  $I_{\rm D}-V_{\rm G}$  characteristics at higher temperatures. This further confirms that the origin of this negative shift is the creation of S vacancies acting as positive charges, which might be more efficient when bare  ${\rm MoS}_2$  is interacting with the environment of the vacuum chamber [58, 59] and catalyzed by the grain boundaries [57].

Nevertheless, baking of our Process 2 devices does not lead to a considerable increase of the hysteresis (figure 6(c)). One possible reason for this is that in large grain size MoS<sub>2</sub> films the penetration of adsorbates to the CaF<sub>2</sub>/MoS<sub>2</sub> interface is less efficient, owing to the lack of grain boundaries. As such, newly created S vacancies are not able to interact with these adsorbates as described in [41] and remain passive, which is very different from Process 1 devices with small grain MoS<sub>2</sub> films. On the other side, channel defects are known to be very fast to contribute to the hysteresis by direct charge trapping of carriers [42]. As a result, in baked Process 2 devices the normalized hysteresis is nearly an order of magnitude smaller than in their SiO<sub>2</sub>(25 nm)/  $MoS_2$  counterparts (figure 6(d)). This is despite the fact that the overall quality of the directly grown MoS<sub>2</sub> with at least 100  $\mu$ m grains used in the latter case is obviously better [7], which is confirmed by the absence of

Figure 6. Evolution of the  $I_D - V_G$  characteristics of our Process 2 CaF<sub>2</sub>(2 nm)/MoS<sub>2</sub> FETs (a) and bare channel SiO<sub>2</sub>(25 nm)/MoS<sub>2</sub> FETs [6,61] (b) during and after high temperature treatment ( $I_D$  is normalized by the channel width). In both cases a negative threshold voltage shift is observed. (c) For the Process 2 devices the hysteresis remains small even after baking at 165 °C. (d) The hysteresis widths normalized by the insulator field factor for our Process 2 devices with CaF<sub>2</sub> are considerably smaller than for bare channel SiO<sub>2</sub>(25 nm)/MoS<sub>2</sub> FETs. For both technologies the measurements have been performed on baked devices with negatively shifted  $V_{th}$ , and the results for three different devices are plotted. (e) Subsequent heating of baked Process 2 devices up to 120 °C leads to switching of the hysteresis towards the counterclockwise direction. (f) While the standard clockwise hysteresis around  $V_{th}$  becomes annealed (top), the counterclockwise hysteresis appears for slower sweeps and starts to be localized above  $V_{th}$  (bottom).

the fast trapping issues discussed above for our Process 1 devices even after baking at 300 °C. This allows us to conclude that even in bare channel devices the hysteresis dynamics may be strongly dependent on the gate insulator used. At the same time, virtually defect-free crystalline  $\text{CaF}_2$  is superior compared to amorphous  $\text{SiO}_2$  with its numerous oxide defects, which makes devices with  $\text{CaF}_2$  more competitive even if the  $\text{MoS}_2$  growth process is less optimized.

Finally, we examine the temperature dependence of the hysteresis in our Process 2 CaF<sub>2</sub>/MoS<sub>2</sub> devices. As shown in figure 6(e), subsequent heating of baked devices up to 120 °C leads to a switching of the hysteresis from clockwise towards counterclockwise, which

becomes more pronounced at 165 °C (see figure S8 in the SI) until the device fails at slower sweeps. This is again similar to our observations on bare channel SiO<sub>2</sub>/ MoS<sub>2</sub> FETs [61]. Since in the latter devices this issue was found to be suppressed after encapsulation (see figure S8 in the SI), we suggest that counterclockwise hysteresis observed at higher temperatures originates from thermally and bias enhanced chemical interaction between bare MoS<sub>2</sub> channel and the environment. For instance, one possible reason might be the creation/substitution of S vacancies, though this requires further investigation. In fact, the clockwise hysteresis observed around  $V_{\rm th}$  at 25 °C completely disappears at 120 °C and becomes substituted by the counter-

clockwise hysteresis localized above  $V_{\rm th}$  (figure 6(f)). Annealing of the clockwise hysteresis with no thermal activation further confirms that this issue is mostly due to adsorbates attached to the CaF<sub>2</sub>/MoS<sub>2</sub> interface, even though in Process 2 devices their concentration is rather small. At the same time, the absence of slow thermally activated charge trapping in CaF<sub>2</sub> prevents non-volatile memory switching [62] of the hysteresis at higher temperatures, which is also known for our previously studied bare channel SiO<sub>2</sub>/MoS<sub>2</sub> FETs [61] (see figure S8 in the SI). Namely, in devices with CaF<sub>2</sub> this switching is substituted by simple counterclockwise hysteresis at higher temperatures, owing to no interplay between different hysteresis mechanisms.

#### 3. Conclusions

We have reported a detailed performance and reliability study of bilayer CVD-grown MoS2 FETs with only 2 nm thick crystalline CaF<sub>2</sub> insulators. We have found that in these devices the hysteresis and long-term drifts of the gate transfer characteristics are mainly due to fast intrinsic defects in the MoS<sub>2</sub> channel interacting with adsorbates, while the CaF2 insulator itself contains much lower amount of defects. As a result, we have demonstrated that the performance, reliability and thermal stability of devices with CaF<sub>2</sub> strongly depend on the quality of the MoS<sub>2</sub> channel which is directly related to the grain size of the film. We also compared our results for CaF2/MoS2 FETs with our previous observations on MoS<sub>2</sub> devices with SiO<sub>2</sub> and hBN. This allowed us to clearly show that crystalline CaF<sub>2</sub> is currently the most promising insulator for 2D devices. On the other side, the major performance- and reliability-related limitations of CaF<sub>2</sub>/MoS<sub>2</sub> FETs can be addressed by using higher quality MoS<sub>2</sub> films and protecting them with suitable encapsulation layers. Finally, for the first time we observed a special degradation mechanism which arises in devices with tunnel-thin gate insulators and found that CaF<sub>2</sub> outperforms hBN with respect to this issue as well. As such, we conclude that our CaF2/MoS2 FETs present a route towards competitive and fully scalable 2D nanoelectronics.

### 4. Methods

#### 4.1. Device fabrication

Fabrication of our devices consists of MBE growth of 2 nm thick CaF<sub>2</sub> films, CVD growth of bilayer MoS<sub>2</sub>, transfer of the MoS<sub>2</sub> films onto the CaF<sub>2</sub> surface and e-beam lithography steps to shape the devices.

CaF<sub>2</sub> layers were grown on n-Si(111) substrates with  $N_{\rm D}=10^{15}~{\rm cm^{-3}}$  and small miscut (5 to 10 angular minutes). These substrates were carefully cleaned by using a chemical treatment. Then, a protective oxide

layer was formed using the method of Shiraki [63] and subsequently removed by annealing for 2 min at 1200 °C under ultra-high vacuum conditions ( $\sim 10^{-8} - 10^{-7}$  Pa). After this, the CaF<sub>2</sub> film was grown on this atomically clean 7 × 7 Si(111) surface using an MBE process with the optimal growth temperature of 250 °C and deposition rate of about 1.3 nm min<sup>-1</sup>. The crystalline quality of the formed CaF<sub>2</sub> layers was examined using reflection high-energy electron diffraction (RHEED) [64] with an electron energy of 15 keV.

Bilayer MoS<sub>2</sub> films were grown on c-plane sapphire substrates using the CVD process of [49] with sulfur and MoO3 as powder precursors and ultrahigh-purity Ar as the carrier gas. The growth was performed at atmospheric pressure and a temperature of 750 °C. While adjusting the control of the sulfur concentration in the reaction chamber during growth, we obtained two different kinds of MoS<sub>2</sub> films. These are the Process 1 MoS<sub>2</sub> films, which are one of the first grown using this setup, and Process 2 films obtained already after some tuning of the control of the sulfur concentration. At the nucleation stage Process 1 films were found to consist of relatively small grains of about  $1-2 \mu m$ , while in the Process 2 films the grain size was about 10–15  $\mu$ m indicating a better quality. As soon as the layer is formed completely, the grain size in both cases becomes slightly smaller [30].

In order to shape the devices, we applied several e-beam lithography steps. First we sputtered 15–20  $\mu$ m sized SiO<sub>2</sub>(5–10 nm)/Ti/Au contact pads for the probes, with this additional SiO<sub>2</sub> layer required to minimize possible parasitic leakage currents. After this,  $7 \times 7$ mm MoS<sub>2</sub> film was transferred onto the CaF<sub>2</sub>/Si(111) substrate using a polystyrene film as a carrier polymer which was then dissolved in toluene, following the method of [50]. The transferred MoS<sub>2</sub> film was subsequently etched by reactive ion etching, in order to define the channels with L and W varied between 400 and 800 nm. Finally, the channels were contacted by e-beam evaporated Ti/Au pads deposited on top of MoS<sub>2</sub> in preshaped contact areas. This second layer of Ti/Au was slightly extended out of the first metal layer to contact MoS<sub>2</sub> on top of the bare CaF<sub>2</sub> surface in order to finally shape MoS<sub>2</sub> FETs with 2 nm CaF<sub>2</sub> gate insulator.

# 4.2. Electrical characterization

Electrical characterization of our CaF<sub>2</sub>/MoS<sub>2</sub> FETs consisted in the measurements of the performance parameters, hysteresis and long-term BTI drifts of the  $I_{\rm D}-V_{\rm G}$  characteristics. These measurements were performed using a Keithley 2636 parameter analyzer in the chamber of a Lakeshore probestation either in a vacuum ( $\sim$ 5 × 10<sup>-6</sup> Torr) or in ambient conditions, in complete darkness and at temperatures ranging from 25 °C to 165 °C. When characterizing the device performance, we used the autorange measurement

mode to correctly resolve the on/off current ratio. The hysteresis of the  $I_D - V_G$  characteristics was studied using our established measurement technique [21] based on double sweeps with varied sweep times. For a convenient comparison of the data for different devices and measurement conditions, we plot the extracted hysteresis widths versus the measurement frequency  $f = 1/t_{sw}$ , with  $t_{sw}$  being the total sweep time, and normalize them by the insulator field factor  $K = \Delta V_{\rm G}/d_{\rm ins}$ , where  $\Delta V_{\rm G}$  is the width of the sweep range and  $d_{ins}$  is the insulator thickness. The BTI drifts were measured using subsequent stress/recovery rounds with fast  $(t_{\rm sw} \sim 0.2 \text{ s}) I_{\rm D} - V_{\rm G}$  sweeps performed at different recovery stages [21, 45]. We express the obtained results using the recovery traces of the threshold voltage shift versus the relaxation time. For convenient comparison of the results for different devices, we normalize the measured threshold voltage shifts by the stress insulator fields.

# Acknowledgment

The authors thank for the financial support through the Austrian Science Fund FWF grants n° I2606-N30 and I4123-N30. TM, DKP and SW acknowledge financial support by the Austrian Science Fund FWF (START Y 539-N16) and the European Union (Grant agreement No. 785219 Graphene Flagship). This work was partly supported by the Russian Foundation for Basic Research (Grant No. 18-57-80006 BRICS\_t). We gratefully acknowledge Dr Kirby Smithe and Prof Eric Pop fo providing us SiO<sub>2</sub>/MoS<sub>2</sub> FETs. YYI is a member of Mediterranean Institute of Fundamental Physics (MIFP).

# **Competing interests**

The authors declare no competing interests.

## **ORCID** iDs

Yury Yu Illarionov https://orcid.org/0000-0003-4323-1389

Theresia Knobloch https://orcid.org/0000-0001-5156-9510

Michael Waltl https://orcid.org/0000-0001-6042-759X

Mario Lanza **b** https://orcid.org/0000-0003-4756-8632

Tibor Grasser https://orcid.org/0000-0001-6536-2238

# References

- [1] Novoselov K, Geim A, Morozov S, Jiang D, Zhang Y, Dubonos S, Grigorieva I and Firsov A 2004 *Science* **306** 666–9

- [2] Lemme M, Echtermeyer T, Baus M and Kurz H 2007 *IEEE Electron Device Lett.* **27** 1–12

- [3] Radisavljevic B, Radenovic A, Berivio J, Giacometti V and Kis A 2011 Nat. Nanotechnol. 6 147–50

- [4] Kang J, Liu W and Banerjee K 2014 Appl. Phys. Lett. 104 093106

- [5] Chuang S et al 2014 Nano Lett. 14 1337-42

- [6] Illarionov Y, Smithe K, Waltl M, Knobloch T, Pop E and Grasser T 2017 IEEE Electron Device Lett. 38 1763–6

- [7] Smithe K, Suryavanshi S, Munoz-Rojo M, Tedjarati A and Pop E 2017 ACS Nano 11 8456–63

- [8] Bolshakov P, Zhao P, Azcatl A, Hurley P, Wallace R and Young C 2017 Appl. Phys. Lett. 111 032110

- [9] Liao W, Wei W, Tong Y, Chim W K and Zhu C 2017 Appl. Phys. Lett. 111 082105

- [10] Cho Y, Park J, Kim M, Jeong Y, Ahn J, Kim T, Choi H, Yi Y and Im S 2018 Adv. Funct. Mater. 28 1801204

- [11] Yang L et al 2014 Nano Lett. 14 6275-80

- [12] Liu W, Kang J, Sarkar D, Khatami Y, Jena D and Banerjee K 2013 Nano Lett. 13 1983–90

- [13] Prakash A and Appenzeller J 2017 ACS Nano 11 1626–32

- [14] Li L, Yu Y, Ye G, Ge Q, Ou X, Wu H, Feng D, Chen X and Zhang Y 2014 Nat. Nanotechnol. 9 372–7

- [15] Chen X et al 2018 ACS Nano 12 5003–10

- [16] Tao L, Cinquanta E, Chiappe D, Grazianetti C, Fanciulli M, Dubey M, Molle A and Akinwande D 2015 Nat. Nanotechnol. 10 227

- [17] Wang H, Yu L, Lee Y-H, Shi Y, Hsu A, Chin M, Li L-J, Dubey M, Kong J and Palacios T 2012 *Nano Lett.* 12 4674–80

- [18] Das T, Chen X, Jang H, Oh I-K, Kim H and Ahn J-H 2016 Small 12 5720–7

- [19] Wachter S, Polyushkin D K, Bethge O and Mueller T 2017 Nat. Commun. 8 14948

- [20] Guo Y, Wei X, Shu J, Liu B, Yin J, Guan C, Han Y, Gao S and Chen Q 2015 Appl. Phys. Lett. **106** 103109

- [21] Illarionov Y, Rzepa G, Waltl M, Knobloch T, Grill A, Furchi M, Mueller T and Grasser T 2016 2D Mater. 3 035004

- [22] Illarionov Y, Knobloch T, Waltl M, Rzepa G, Pospischil A, Polyushkin D, Furchi M, Mueller T and Grasser T 2017 2D Mater. 4 025108

- [23] Jang S, Youn J, Song Y and Lee S 2016 Sci. Rep. 6 30449

- [24] Hui F, Pan C, Shi Y, Ji Y, Grustan-Gutierrez E and Lanza M 2016 Microelectron. Eng. 163 119–33

- [25] Lee G-H et al 2013 ACS Nano 7 7931–6

- [26] Lee C, Rathi S, Khan M, Lim D, Kim Y, Yun S, Youn D-H, Watanabe K, Taniguchi T and Kim G-H 2018 Nanotechnology 39 335202

- [27] Laturia A, Van de Put M and Vandenberghe W 2018 npj 2D Mater. Appl. 2 6

- [28] Geick R, Perry C and Rupprecht G 1966 Phys. Rev. 146 543

- [29] Cassabois G, Valvin P and Gil B 2016 Nat. Photon. 10 262-6

- [30] Illarionov Y et al 2019 Nat. Electron. 2 230-5

- [31] Hayes W 1974 Crystals with the Fluorite Structure (Oxford: Clarendon)

- [32] Illarionov Y, Vexler M, Suturin S, Fedorov V and Sokolov N 2010 *Tech. Phys. Lett.* **36** 404–7

- [33] Koma A, Saiki K and Sato Y 1990 Appl. Surf. Sci. 41 451-6

- [34] Vishwanath S et al 2015 2D Mater. 2 024007

- [35] Vishwanath S et al 2018 J. Cryst. Growth 482 61-9

- [36] Ravez J 1997 J. Phys. III 7 1129-44

- [37] Kaveev A, Anisimov O, Banshchikov A, Kartenko N, Ulin V and Sokolov N 2005 J. Appl. Phys. 98 013519

- [38] Banshchikov A, Golosovskii I, Krupin A, Koshmak K, Sokolov N, Chernenkov Y, Yagovkina M, Ulin V and Tabuchi M 2015 Phys. Solid State 57 1647–52

- [39] Late D, Liu B, Matte H, Dravid V and Rao C 2012 ACS Nano 6 5635–41

- [40] Li T, Du G, Zhang B and Zeng Z 2014 Appl. Phys. Lett. 105 093107

- [41] Di Bartolomeo A, Genovese L, Giubileo F, Iemmo L, Luongo G, Foller T and Schleberger M 2017 2D Mater. 5 015014

- [42] Knobloch T, Rzepa G, Illarionov Y, Waltl M, Schanovsky F, Stampfer B, Furchi M, Mueller T and Grasser T 2018 IEEE J. Electron Dev. Soc. 6 972–8

- [43] Cho K, Park W, Park J, Jeong H, Jang J, Kim T-Y, Hong W-K, Hong S and Lee T 2013 ACS Nano 7 7751–8

- [44] Yang S, Park S, Jang S, Kim H and Kwon J-Y 2014 *Phys. Status Solidi* 8 714–8

- [45] Illarionov Y, Smith A, Vaziri S, Ostling M, Mueller T, Lemme M and Grasser T 2014 Appl. Phys. Lett. 105 143507

2D Mater. **6** (2019) 045004 Y Yu Illarionov et al

- [46] Illarionov Y, Waltl M, Rzepa G, Kim J-S, Kim S, Dodabalapur A, Akinwande D and Grasser T 2016 ACS Nano 10 9543–9

- [47] Huard V, Denais M and Parthasarathy C 2006 *Microelectron*. *Reliab.* 46 1–23

- [48] Grasser T 2012 Microelectron. Reliab. 52 39-70

- [49] Dumcenco D et al 2015 ACS Nano 9 4611–20

- [50] Gurarslan A, Yu Y, Su L, Yu Y, Suarez F, Yao S, Zhu Y, Ozturk M, Zhang Y and Cao L 2014 ACS Nano 8 11522–8

- [51] Illarionov Y, Vexler M, Fedorov V, Suturin S and Sokolov N 2014 J. Appl. Phys. 115 223706

- [52] van der Zande A, Huang P, Chenet D, Berkelbach T, You Y, Lee G, Heinz T, Reichmann D, Muller D and Hone J 2013 Nat. Mater. 12 554–61

- $[53]\ Zhang\ J\ et\ al\ 2014\ ACS\ Nano\ 6024-30$

- [54] Ling X, Lee Y-H, Lin Y, Fang W, Yu L, Dresselhaus M and Kong J 2014 Nano Lett. 14 464–72

- [55] Smithe K, English C, Suryavanshi S and Pop E 2017 2D Mater.  $4\,011009$

- [56] Grasser T, Wagner P-J, Reisinger H, Aichinger T, Pobegen G, Nelhiebel M and Kaczer B 2011 Analytic modeling of the bias temperature instability using capture/emission time maps IEEE Int. Electron Devices Meeting pp 27.4.1–4

- [57] Yu Z, Zhang Y-W and Yakobson B 2015 Nano Lett. 15 6855-61

- [58] Kim B et al 2013 RSC Adv. 3 18424-9

- [59] Leong W, Li Y, Luo X, Nai C, Quek S and Thong J 2015 Nanoscale 7 10823–31

- [60] Krivosheeva A, Shaposhnikov V, Borisenko V, Lazzari J-L, Waileong C, Gusakova J and Tay B 2015 *J. Semicond.* **36** 122002

- [61] Illarionov Y, Smithe K, Waltl M, Grady R, Deshmukh S, Pop E and Grasser T 2018 Annealing and encapsulation of CVD-MoS<sub>2</sub> FETs with 10<sup>10</sup> on/off current ratio *Proc. of 76th Device Research Conf.* pp 1–2

- [62] He G et al 2016 Nano Lett. 16 6445–51

- [63] Ishizaka A and Shiraki Y 1986 J. Electrochem. Soc. 133 666-71

- [64] Sokolov N, Alvarez J and Yakovlev N 1992 Appl. Surf. Sci.