Field Effect Transistors www.afm-journal.de

# **Engineering Field Effect Transistors with 2D Semiconducting Channels: Status and Prospects**

Xu Jing, Yury Illarionov, Eilam Yalon, Peng Zhou, Tibor Grasser, Yuanyuan Shi, and Mario Lanza\*

The continuous miniaturization of field effect transistors (FETs) dictated by Moore's law has enabled continuous enhancement of their performance during the last four decades, allowing the fabrication of more powerful electronic products (e.g., computers and phones). However, as the size of FETs currently approaches interatomic distances, a general performance stagnation is expected, and new strategies to continue the performance enhancement trend are being thoroughly investigated. Among them, the use of 2D semiconducting materials as channels in FETs has raised a lot of interest in both academia and industry. However, after 15 years of intense research on 2D materials, there remain important limitations preventing their integration in solid-state microelectronic devices. In this work, the main methods developed to fabricate FETs with 2D semiconducting channels are presented, and their scalability and compatibility with the requirements imposed by the semiconductor industry are discussed. The key factors that determine the performance of FETs with 2D semiconducting channels are carefully analyzed, and some recommendations to engineer them are proposed. This report presents a pathway for the integration of 2D semiconducting materials in FETs, and therefore, it may become a useful guide for materials scientists and engineers working in this field.

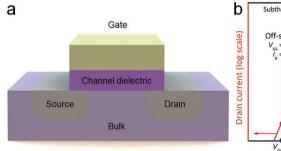

with four terminals (i.e., gate, drain, source, and bulk; see Figure 1a), in which the current flowing between drain and source  $(I_{DS})$  can be controlled by tuning the voltage between gate and bulk  $(V_G)$ . Mass-production of FETs started in the late 1970s using silicon-related materials, i.e., a polysilicon gate, silicon dioxide (SiO<sub>2</sub>) as a gate dielectric, and silicon as the channel material in the bulk.[4,5] The adjustment of  $I_{DS}$  is caused by the modulation of the electrical resistance of the Si material between the drain and source electrodes due to the electrical field generated by V<sub>G</sub>, which forms a channel of minority charge carriers in the Si material right beneath the gate dielectric. The main figures of merit of an FET are the transfer characteristic ( $I_{\rm DS}$  vs  $V_{\rm G}$ , for a specific  $V_{DS}$ ; see Figure 1b) and the output characteristic ( $I_{DS}$  vs  $V_{DS}$ , for various  $V_{G}$ ; see Figure 1c). From the transfer characteristic one can extract several important operational parameters of the FET:

## 1. Introduction

The field effect transistor (FET) is the most important electronic device in modern integrated circuits for information processing and storage<sup>[1,2]</sup> and modern electronic chips contain billions of FETs per square millimeter.[3] An FET is an electronic device

- i) The OFF state current ( $I_{OFF}$ ), which should be as low as possible to minimize standby power consumption, and the ON state current ( $I_{ON}$ ), which should be high to ensure enough power supply to the circuitry connected at the output.<sup>[1,6]</sup>

- ii) The current ratio between ON and OFF states  $(I_{ON}/I_{OFF})$ , which in switches for digital logic applications is required to be larger than  $10^5$ .[6-8]

X. Jing, Prof. M. Lanza Institute of Functional Nano and Soft Materials (FUNSOM) Collaborative Innovation Center of Suzhou Nano Science and Technology

Soochow University 199 Ren-Ai Road, Suzhou 215123, China

E-mail: mlanza@suda.edu.cn Dr. Y. Illarionov, Prof. T. Grasser Institute for Microelectronics (TU Wien) Gusshausstrasse 27-29, 1040 Vienna, Austria Dr. Y. Illarionov Ioffe Physical-Technical Institute

Polytechnicheskaya 26, 194021 St. Petersburg, Russia

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adfm.201901971.

Prof. E. Yalon. Dr. Y. Shi Andrew and Erna Viterbi Faculty of Electrical Engineering Technion-Israel Institute of Technology Haifa 32000, Israel Prof. P. Zhou State Key Laboratory of ASIC and System School of Microelectronics **Fudan University** Shanghai 200433, China Dr. Y. Shi Materials Science and Engineering Department Guangdong Technion-Israel Institute of Technology 241 Daxue Road, 515063 Shantou, China

DOI: 10.1002/adfm.201901971

www.afm-iournal.de

- iii) The threshold voltage ( $V_{\rm th}$ ), which is the value of  $V_{\rm G}$  at the transition from OFF state to ON state in the transfer characteristic. [1,6]

- iv) The subthreshold slope (SS), which is the slope of the loglinear regime of the transfer characteristic in the subthreshold region. This parameter can be calculated using Equation (1)

$$SS = \frac{d(\log I_{DS})}{dV_{G}} = \left[\frac{dV_{G}}{d(\log I_{DS})}\right]^{-1}$$

(1)

Its inverse value (S = 1/SS), called subthreshold swing, is also often used in the literature. Both of them indicate how well the FET can be switched with respect to the applied  $V_G$ ; a low SS (large S) is desired.

v) The field effect mobility, which is used to estimate the drift velocity of the carriers throughout the channel at a given (relatively low) electric field. Its value can be evaluated using the FET transconductance as shown by Equation (2)<sup>[10,11]</sup>

$$\mu = \left[ \frac{\mathrm{d}I_{\mathrm{DS}}}{\mathrm{d}V_{G}} \middle| \times \left[ \frac{L}{WC_{G}V_{\mathrm{DS}}} \right] \right] \tag{2}$$

in which L is the channel length, W is the channel width, and  $C_{\rm G}$  is the capacitance between the channel and the gate per unit area. It is worth noting that the value of  $C_{\rm G}$  may change depending on the structure of the device (see Section 2.2 and Figure 2), and this has produced important mobility overestimations in the past.<sup>[10,12]</sup>

On the other hand, from the output characteristic it is possible to evaluate the quality of the contact between the semiconducting channel and electrodes. Ideally, this contact should be Ohmic in order to facilitate charge transfer, which should be manifested with clear linear dependence of  $I_{\rm DS}$  at low  $V_{\rm DS}$  in the output characteristic (as displayed in Figure 1c).

The rapid development of modern electronic technologies has been strongly linked to the continuous enhancement of the performance of FETs, which has been mainly related to its miniaturization, according to the Moore's law. [13,14] However, as the scaling down of the FET is reaching nanometric sizes, the devices face fundamental limitations—critical parts of the device cannot scale down below few atoms in length—and some reliability problems (e.g., leakage current [15] and

Xu Jing received his bachelor degree in materials science and engineering in 2015 from the Changshu Institute of Technology. Since September 2015 he has been a Ph.D. student at Soochow University, where he works on the fabrication and characterization of 2D material-based electronic devices. From January to December 2017,

he was a visiting scholar at University of Texas at Austin (USA), where he worked under the supervision of professor Deji Akinwande on the synthesis of 2D materials on metal-coated wafers.

Mario Lanza is a Young 1000 Talent full professor in nanoelectronics at Soochow University. He received his Ph.D. degree in electronic engineering in 2010 at the Universitat Autonoma de Barcelona. In 2010–2011, he was an NSFC postdoctoral fellow at Peking University, and in 2012–2013 he was a Marie Curie postdoctoral fellow at

Stanford University. In 2019 he became a distinguished lecturer of the IEEE - Electron Devices Society (USA). His research group, which comprises 15–20 graduate students and postdocs, focuses on the development of advanced electronic devices using 2D materials, with a special interest in resistive switching applications.

poor heat dissipation<sup>[16]</sup>) become more and more severe. Consequently, new strategies to enhance their performance are required. Among all of them, the introduction of new materials with better properties (i.e., higher dielectric constant and

Dialii-Source voltage

Figure 1. a) Schematic of a traditional FET. b) Typical transfer characteristics ( $I_{DS}$  vs  $V_{CS}$ ) of an n-type 2D material channel FET device. Note that the scale of the red curve is logarithmic and the blue one is linear. Reproduced under the terms and conditions of the Creactive Commons CC BY 3.0 Unported License. [1] Copyright 2015, Royal Society of Chemistry. c) Typical shape of the output characteristics ( $I_{DS}$  vs  $V_{DS}$ ) of an n-type 2D material channel FET device. Saturation of  $I_{DS}$  can be observed with larger gate voltage ( $V_g$ ). Reproduced with permission. [9] Copyright 2018, Royal Society of Chemistry.

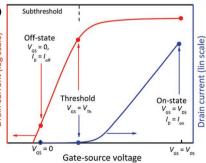

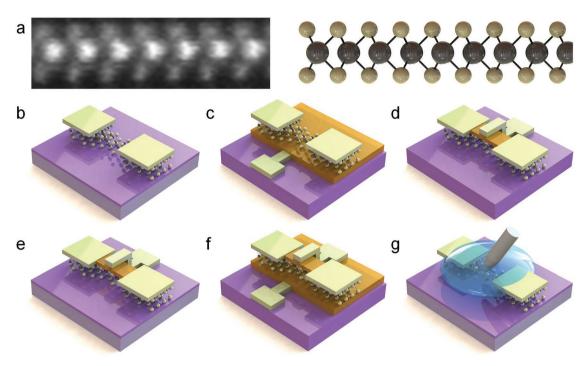

Figure 2. a) Atomic-resolution TEM image of monolayer WSe<sub>2</sub> (2.45 nm  $\times$  0.73 nm) and corresponding schematic. Reproduced with permission. <sup>[35]</sup> Copyright 2018, Springer Nature. Basic 2D material–based FET structures (using MoS<sub>2</sub> as example): b) back-gated FET with Si as gate. Reproduced with permission. <sup>[75]</sup> Copyright 2016, Elsevier Ltd; c) back-gated FET with manufactured metal gate electrode; d) top-gated FET; dual gate FET structure with Si back gate e) and patterned back gate f); g) liquid-gated FET structure.

larger carriers mobility) appears to be one of the most promising. As an example, in the early 2000 the SiO2 gate dielectric of FETs became extremely thin, which dramatically increased the leakage currents flowing from/to the gate electrode. This remarkably increased the power consumption of the FETs and, more importantly, reduced their reliability (lifetime).[15] This problem was temporarily mitigated using alternative gate dielectric materials with a higher dielectric constant, which allow generating the same gate capacitance (i.e., necessary to form the channel)<sup>[17]</sup> using much thicker stacks, contributing to reduce the leakage current orders of magnitude. These materials, referred to as high-k dielectrics, have become now the standard in advanced FETs.<sup>[18]</sup> Another example is the use of materials with higher carrier mobility as channel of the FET (i.e., InSb, InAs, InP, GaAs, and GaN), [19] so that their operation speed can be further enhanced. However, these materials are more expensive and form a poor interface with traditional insulators, and for these reasons thy have still not been implemented in commercial FETs for mass production.

One recent strategy to enhance the performance (i.e., operation speed,  $I_{\rm ON}/I_{\rm OFF}$ , and SS) of FETs is the introduction of 2D materials as channel between the source and the drain. This strategy was first proposed in 2004. [20] In that work graphene was synthesized by mechanical exfoliation (repeated peeling) of highly oriented pyrolytic graphite (HOPG), and used as channel in FET devices patterned on 300 nm SiO<sub>2</sub>/Si substrates using electron beam lithography (EBL). The devices exhibited remarkably high carrier concentration, high room temperature carrier mobility (3000–10 000 cm² V<sup>-1</sup> s<sup>-1</sup> for few-layer graphene [20]), and record cutoff frequencies ( $f_{\rm T}=26~{\rm GHz}$ )—this is the

frequency at which the current gain becomes unity. [21] After that, the mobility of graphene-based FETs was further enhanced to 350 000 cm² V $^{-1}$  s $^{-1}$ ,[22] and nowadays the best values of cutoff frequency reported for such type of devices is 427 GHz. [23] Despite these promising developments, graphene FETs show a very poor  $I_{\rm ON}/I_{\rm OFF}$  ratio (<10)[24] due to its absence of a bandgap, which makes their power consumption in standby mode very high. [25]

In 2011, a semiconducting 2D layered material, molybdenum disulfide (MoS<sub>2</sub>) was used to fabricate FETs following the same procedure previously used for graphene, [10] and despite the mobility of the resulting devices (2-7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1[12]</sup>) was remarkably lower than that of graphene FETs, the currents in standby mode were effectively reduced by up to six orders of magnitude.[10] After this pioneering work, many other groups fabricated FETs using MoS2 and other 2D semiconductors, most of them from the family of transition metal dichalcogenides (TMDs) with the general formula of  $MX_2$  (being M = transitionmetal and X = chalcogen) such as  $MoSe_2$ , [26]  $MoTe_2$ , [27]  $WSe_2$ , [28] and WS<sub>2</sub>, <sup>[29]</sup> and reported cutting-edge device performances. In addition to TMDs, single-element 2D semiconductors such as phosphorene, i.e., black phosphorous (BP) in the single-layer limit, have also been used to fabricate FETs with even higher mobility than 2D-TMDs.<sup>[30]</sup> Nowadays, MoS<sub>2</sub> FETs exhibiting  $I_{\rm ON}/I_{\rm OFF}$  current ratios >10<sup>9[31]</sup> and subthreshold swings down to 62 mV decade<sup>-1</sup> for monolayer device<sup>[32]</sup> have been readily fabricated by many groups. However, so far the mobilities measured in FETs using 2D semiconducting materials are still behind that of Si-based transistors, [1] meaning that it is not expected that this technology can be used for applications that require a higher

www.afm-journal.de

mobility. However, FETs with channels made of 2D semiconducting materials can still provide many other exotic properties (e.g., flexibility and transparency) which can make them very attractive for several optoelectronic and straintronic applications.

Despite this progress, developing FETs with channels made of 2D semiconducting materials at wafer level for industrial applications remains a big challenge, due to the complex growth and manipulation of the 2D material, and also due to important reliability problems appeared during device fabrication (e.g., poor interface with other materials). In this paper, the status of FETs with channels made of 2D semiconducting materials is reviewed in depth providing critical opinions on the real usefulness and industrial applicability of the prototypes constructed. In section 2, we review the methods to synthesize the 2D materials and the existing 2D-FET device configurations. Sections 3-6 discuss the effect of electrode/channel contact resistance, dielectric environment, channel length, and channel thickness (respectively) on the performance of the 2D-FETs. Finally, in Section 7 the effect of the temperature is discussed for different channel thicknesses, device structures and dielectric environments.

## 2. Device Fabrication

## 2.1. Materials Synthesis

In order to be compatible with typical transistor requirements for logic applications—defined in the technology roadmap for semiconductors (ITRS)<sup>[3]</sup>—the 2D semiconducting materials implemented as channels in FETs need to have a large enough bandgap (>0.4 eV) and a high carriers mobility (>500 cm² V $^{-1}$  s $^{-1}$ ). [6,33] The synthesis methods used need to ensure large lateral (wafer scale) size, uniform thickness (along the entire wafer) and low density of defects (e.g.,  $\approx\!\!8\times10^{12}$  cm $^{-2}$  in MoS2 $^{[34]}$ ). Since the first isolation of graphene via mechanical exfoliation in 2004,  $^{[20]}$  more and more techniques have been developed to synthesize monolayer and few-layer-thick 2D materials, including liquid phase exfoliation (LPE), chemical vapor deposition (CVD), physical vapor deposition (PVD), and molecular beam epitaxy.

### 2.1.1. Mechanical Exfoliation

Almost all 2D materials can be obtained by mechanical exfoliation from a raw crystal source, which is formed by particles containing many layers stacked on top of each other. While in each layer the atoms are strongly linked to each other by covalent bonds, the layers adhere to each other by van der Waals forces, which are relatively small. Consequently, these layers can be easily separated (i.e., exfoliated) by applying low mechanical stresses. If this exfoliation process is repeated several times, the thickness of the raw material can be reduced down to a few (<20) layers, and sometimes even to one single layer. It is worth noting that the term 2D used in most literature is not strictly correct when talking about multilayer materials and/or single layer materials with more than one plane, such as WSe<sub>2</sub> in which one layer is formed by three planes that are not

vertically aligned (see Figure 2a).<sup>[35]</sup> However, for consistency with the existing literature, in this review paper all these materials will be encompassed by the term 2D.

Mechanical exfoliation was the first (and is still the most frequently used) method to synthesize 2D materials for fundamental scientific studies. By repeated folding and unfolding of a scotch tape containing the raw material in solid crystal form, the stacked layers can be separated from each other, and when the resulting flakes are thin enough, they can be adhered to the target substrate by applying perpendicular pressure and removing the tape. For TMDs this process can be carried out under normal air atmosphere, but in the case of black phosphorous and other air-sensitive 2D materials a nitrogen glove box or other an environmental chamber filled with another inert gas is required. [36,37] Conventional mechanical exfoliation normally gives rise to contamination on the surface of exfoliated 2D materials, such as the residual polymers from the tape, which can produce undesired performance alterations in the FETs (mobility degradation and hysteresis) during normal operation.[38] So after mechanical exfoliation of 2D materials, some researchers washed the surface of exfoliated 2D materials using acetone (or other solvents) for some minutes or hours<sup>[39,40]</sup> or thermal annealing.<sup>[41]</sup>

Although many FET prototypes have been constructed using 2D materials synthesized by this method, the very small lateral size of the flakes (<50  $\mu m$ ) and their inhomogeneous and uncontrollable thicknesses are preventing its industrial use. Apart from the physical limitations, mechanical exfoliation is also a very slow process that requires human labor, which is thus expensive. Therefore, when studying research articles on 2D material–based FETs produced by this method, readers need to be aware that these are fundamental research papers with zero applicability at the industrial level.  $^{[42]}$

In order to fabricate 2D materials at an industrial scale, methods different from mechanical exfoliation are currently under development and their main properties will be summarized in the following sections.

#### 2.1.2. Liquid Phase Exfoliation

The LPE method consists of separating the layers by applying a gentler shear stress to the raw powder material (instead of the extreme mechanical force used during mechanical exfoliation), by immersing it in a liquid solvent exposed to ultrasonication.[11,43] Depending on the interplane van der Waals forces of each material and the thickness desired, the power, time and type of solvent used during the sonication process should be adjusted.[44-46] After sonication, a centrifugation step is necessary to separate thin flakes from bigger (useless) particles. The resulting product, which is offered by several manufacturers worldwide, [47] is a solution containing a given density of 2D flakes with specific lengths and thicknesses; these solutions sometimes require an additional polymer stabilizer to avoid flakes agglomeration. However, a recent report warned that most manufacturers tend to advertise too optimistic (fake) information about the thickness and lateral size of their product.<sup>[47,48]</sup> This indicates that producing high-quality monolayer 2D materials using this method is very difficult. Then, the 2D flakes can be deposited onto target substrates by

ADVANCED FUNCTIONAL MATERIALS

drop-and-dry,<sup>[49]</sup> inkjet printing,<sup>[50]</sup> or spray methods,<sup>[44,51]</sup> which in the best cases lead to a few-nanometer-thick layer made of many micrometric 2D flakes with random orientations and defective flake-to-flake bonding. Although this method might in principle be suitable for industrial applications (because it can easily cover entire wafers by spin coating) it results in electrons/holes scattering in the film, which degrades the mobility and overall performance of the FETs.[11] Nevertheless, solving this challenge seems to be much more feasible than developing a scalable mechanical exfoliation approach, and in the past few years the LPE method has been improved remarkably. One common strategy in this direction is to use an electrochemical treatment to intercalate different species into gap between layers (i.e., lithium<sup>[52]</sup> and tetraheptylammonium bromide<sup>[53]</sup>), which facilitates their separation during sonication. In October 2018, one breaking report<sup>[53]</sup> presented the fabrication of waferscale electrical circuits based on FETs with channels made of MoS<sub>2</sub> films synthesized via LPE method, and for the first time exhaustive (and useful) device-to-device variability information was reported. It is worth noting that even in this work none of the transistors had monolayer channels as all of them were based on mixed MoS2 thicknesses; interestingly, the thickness fluctuations observed in that work did not seem to be a significant problem in terms of device performance and variability.

## 2.1.3. Chemical Vapor Deposition

CVD synthesis method has recently attracted a considerable amount of attention because it can produce different 2D materials with controllable thicknesses at the wafer scale. In general, the precursors (in gas, liquid, or solid state) are inserted into a tube furnace containing a catalyst substrate. When nanoparticles from the precursor reach the surface of the catalyst substrate, a chemical reaction takes place at those locations (also named seeds). With the time, these seeds expand/grow laterally on the surface of the catalyst substrate until nucleating to each other, resulting in a continuous polycrystalline film. [54,55] For example, the first synthesis of  $MoS_2$  via the CVD method was reported by inserting  $MoO_3$  powder (as Mo source) and sulfur powder (as S source) into a tube furnace containing a piece of  $SiO_2/Si$  using  $N_2$  as carrier gas. [56]

The main challenge of this method for scalable FET production is that the density of point defects (i.e., lattice distortions) in the  $MoS_2$  sheets is much larger than inside exfoliated nanoflakes, especially at the nucleation sites (i.e., grain boundaries). Although this can degrade the mobility of the charge carriers (as in the LPE method), decent mobilities have been reported (i.e.,  $\approx 24~\rm cm^2~V^{-1}~s^{-1}$  for CVD-grown monolayer top-gated  $MoS_2$  FETs at room temperature,  $^{[57]}$  56 cm $^2~V^{-1}~s^{-1}$  for CVD-grown back-gated  $MoS_2$  FETs $^{[58]}$ ). Consequently, several companies started to commercialize large-area 2D materials grown via CVD approach.  $^{[59-61]}$

One particular issue is that the diameter of the tube furnace needs to be small in order to keep a homogeneous atmosphere that results in small thickness fluctuations of the 2D material, which considerably limits the size of the substrates that can be loaded. Some woks reported the use of large tube furnaces to produce large-area films, <sup>[62]</sup> but most scientists still prefer

to use small tubes in order to achieve higher quality. To solve this problem, industrial facilities use systems where entire wafers can be loaded, and where their chambers use shower-like technology with hundreds of microtubes for homogeneous carrier gas and precursor injection (like the Black Magic from Aixtron<sup>[63]</sup>). In addition, these systems allow using plasma during the growth of the 2D material, which provides a better temperature control and avoids substrate de-wetting.

Another challenge facing the CVD approach is that it uses high temperatures up to 1100 °C, which (unlike in LPE method) impedes the deposition of the 2D material directly on the target wafers. To solve this problem, two potential solutions have been suggested. The first potential solution is to reduce the growth temperature, which so far has resulted in very poor material quality (i.e., prohibitive amount of lattice distortions and thickness fluctuations). In fact, one can find in the literature plenty of manuscripts claiming that they managed to grow graphene and other 2D materials at low temperatures (<450 °C) via CVD, but the quality of the material is never correctly characterized (via statistical analysis of cross-sectional TEM images), the carriers' mobility is always much lower, the performance of the devices shown are never proved statistically, and (more importantly) there is no company in the world offering 2D materials grown via CVD at low temperatures (<450 °C). Consequently, this approach is still not reliable and several important voices in the field indicated that solving this problem may be extremely complex, as using a high temperature is necessary to produce the chemical reactions. And the second potential solution is to grow the 2D material on an independent substrate and transfer it on the target wafer using a low temperature process. Although this may introduce some polymer contamination and may result in the generation of cracks (which are larger and more abundant in monolayers due to their lower mechanical strength), this second route seems to be much more feasible, and sophisticated wafer-scale transfer methods have been already developed.<sup>[64]</sup> It is also worth noting that some 2D semiconducting materials, such as phosphorene, have so far never been synthesized by CVD approach. In the best case, ≈40 nm thick BP films that exhibited typical p-type semiconductor behavior<sup>[65]</sup> was synthesized from red phosphorus thin films initially deposited on the substrate. Recent reports claimed the synthesis of phosphorene via CVD,[66] however, the quality demonstrated is still very far from that of exfoliated phosphorene (i.e., barely invisible A<sub>g</sub><sup>1</sup> Raman peak at  $365 \text{ cm}^{-1}$ ).

## 2.1.4. Physical Vapor Deposition

PVD is another bottom-up synthesis method that has also been employed to prepare 2D materials. Within the category of PVD, different subtechniques have been developed. Ultrathin films of TMD materials have been deposited on a substrate by sputtering approach, [67] which uses high energy ions to vaporize the raw (powder source) 2D material. This method is attractive because it requires relatively low working temperatures (room temperature to 400 °C), and offers high deposition rates ( $\approx 1 \text{ Å s}^{-1}$ ). [67–70] Other PVD-related methods used to prepare 2D materials are local heating by pulsed laser<sup>[71]</sup> (which evaporates

ADVANCED FUNCTIONAL MATERIALS

target locally and form 2D materials on substrate), and general heating by a furnace (which physical transport MoS2 from powder source to substrate).<sup>[72]</sup> So far, the 2D semiconducting films grown via PVD-related methods show much lower grain size than those grown via CVD approach,[73] which results in a much larger density of defects at the grain boundaries and reduces the performance of the FETs. Despite some works using PVD-related methods claimed the growth of 2D materials films with supreme quality, in fact there is still no company offering 2D materials grown using this method. In the case of phosphorene, it has been suggested that pulsed laser deposition can be used to deposit ultrathin amorphous BP (a-BP) films (with a highly disordered structure) using a bulk BP crystal source, [74] and the resulting devices exhibited p-type semiconducting behavior—but one should keep in mind that such a-BP material does not hold the genuine properties of real exfoliated phosphorene.

Table 1 summarizes the most relevant synthesis methods used to prepare MoS2, WSe2, WS2, and BP (see Table 1). While topdown methods (mechanical exfoliation, LPE) have been widely adopted for the preparation of both TMDs and phosphorene in research labs, the limited lateral size and large thickness fluctuations will result in large device-to-device variability and thus impede their application in industry. On the other hand, bottomup methods (CVD, PVD) have been studied in sufficient detail and have already been successfully used for the synthesis of TMDs, but still require more time and effort before they can be adopted for phosphorene synthesis. In particular, the CVD method results in uniform 2D material films with large lateral size and decent device performance, which makes it the most promising for future solid-state microelectronic devices fabrication; although the recent report in ref. [46] on MoS<sub>2</sub>-based circuits fabricated via LPE also put again the eyes of the community on this method.

## 2.2. Device Configuration

The device structure of 2D-FETs is very similar to that of traditional silicon on insulator (SOI) FETs, although different configurations have been studied for research purposes. Among them, the most common are as follows:

- i) Back-gated 2D-FET (Figure 2b).<sup>[75]</sup> This is the easiest way to build 2D-FET prototypes and most often used in basic studies. In this configuration the 2D material is directly grown or transferred on a conductive or semiconducting substrate with a dielectric layer on top. After that, the source and drain electrodes are deposited and the 2D material is selectively etched to form the channel. Some groups have studied the field effect without patterning a channel,<sup>[76]</sup> which is not ideal as it results in difficulties regarding estimations of the mobility (the channel width, *W*, in Equation (2) is unknown) and device-to-device variability problems. By using this configuration, there is no need to pattern a gate electrode, as the bulk material of the wafer below the superficial dielectric acts as gate. It is also worth noting that this gate is common for all devices on the wafer.

- ii) Back-gated 2D-FET with patterned (individual) metal gate electrode (Figure 2c). This method can provide much higher controllability of the electrical field, compared to the single-back (common) gate FET. Some authors split the channel by patterning two gate electrodes (one next to each other) with different voltage control, and managed to form a p-n junction for ambipolar conduction.<sup>[77]</sup>

- iii) Top-gated 2D-FET (Figure 2d). This structure is similar to the previous one, with the main difference that the patterned gate electrode is placed above the 2D channel.<sup>[78]</sup> In this configuration the top gate insulator can also work as encapsulating layer covering the entire channel, which can considerably improve the mobility of the FET, as a cleaner interface is created.<sup>[10,79,80]</sup>

- iv) Dual-gated 2D-FET. This device configuration, which can use a substrate (Figure 2e) or patterned back-gate (Figure 2f), provides the highest degree of controllability of the charge carriers in the 2D channel.

- v) Liquid-gating 2D-FET structure (Figure 2f). This is not a real device structure but a test structure only suitable for scientific purposes to explore the conduction limits of 2D-FETs, as the liquid gate cannot be implemented at the circuit level. However, we wanted to include it in this section because it has been widely used for several studies. In this test structure an ionic liquid is used as gate to create electric double layers at the liquid/channel interface, which acts as an

Table 1. Methods used to prepare or synthesize the most common 2D materials used as channel in FETs.

| Materials        | Тор-                      | down                       | Bottom-up                                                                                                                                                   |                                                    |  |  |  |

|------------------|---------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

|                  | Mechanical exfoliation    | Liquid phase exfoliation   | Chemical vapor deposition                                                                                                                                   | Physical vapor deposition Yes,                     |  |  |  |

| MoS <sub>2</sub> | Yes                       | Yes                        | Yes,                                                                                                                                                        |                                                    |  |  |  |

|                  | Demonstrated in ref. [10] | Demonstrated in ref. [11]  | Reaction of component precursor vapors <sup>[56]</sup>                                                                                                      | Sputter deposition <sup>[67]</sup>                 |  |  |  |

|                  |                           |                            | Chalcogenization of a predeposited layer [210]                                                                                                              | Pulsed laser deposition [71]                       |  |  |  |

|                  |                           |                            |                                                                                                                                                             | Thermal evaporation deposition <sup>[72]</sup>     |  |  |  |

| WSe <sub>2</sub> | Yes                       | Yes                        | Yes                                                                                                                                                         | Yes,                                               |  |  |  |

|                  | Demonstrated in ref. [28] | Demonstrated in ref. [211] | Reaction of component precursor vapors <sup>[212]</sup><br>Chalcogenization of a predeposited layer <sup>[213]</sup>                                        | Thermal evaporation deposition <sup>[214]</sup>    |  |  |  |

| WS <sub>2</sub>  | Yes                       | Yes                        | Yes                                                                                                                                                         | Yes,                                               |  |  |  |

| _                | Demonstrated in ref. [29] | Demonstrated in ref. [43]  | Reaction of component precursor vapors[215]                                                                                                                 | Thermal evaporation deposition <sup>[217]</sup>    |  |  |  |

|                  |                           |                            | Chalcogenization of a predeposited layer [216]                                                                                                              |                                                    |  |  |  |

| 3P               | Yes                       | Yes                        | No,                                                                                                                                                         | No,                                                |  |  |  |

|                  | Demonstrated in ref. [30] | Demonstrated in ref. [218] | Suggested p-type semiconductor behavior <sup>[65]</sup><br>claimed successful growth, but the perfor-<br>mances is far form exfoliated ones <sup>[66]</sup> | Attempt of pulsed laser deposition <sup>[74]</sup> |  |  |  |

ultrathin dielectric for minimal screening of electric field. This strategy resulted in a higher performance because the strong band-bending caused by the liquid gate effectively reduces the Schottky barrier thickness at the MoS<sub>2</sub>/metal contacts.<sup>[81]</sup>

For all these different device configurations it is extremely important to select a good dielectric material compatible with the 2D channel to reduce charge impurity scattering, which is known to be a key factor limiting the mobility of devices.<sup>[82]</sup> The dielectric materials traditionally used in CMOS technologies, i.e., SiO<sub>2</sub> and high-k dielectrics (e.g., HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>), have resulted in a low quality interface with the 2D material. The main reason is that 2D materials have very smooth interfaces without dangling bonds, and hence oxides tend to poorly nucleate on their surface. Often a nucleation layer is needed, such as a thin Al layer before the deposition of Al<sub>2</sub>O<sub>3</sub>.<sup>[83]</sup> Such nucleation layers may introduce damage to the interface and generate interfacial states that result in trapping and scattering of charge carriers. To solve this problem, one promising solution is to use 2D insulating materials, such as hexagonal boron nitride (h-BN), as gate dielectric for the 2D-FET.[84-87] This is because these 2D insulators ideally also have no dangling bonds and can adhere to the 2D semiconductors by van der Waals attraction, resulting in a minimized amount of interface states. Moreover, h-BN dielectric stacks have shown a very high reliability when exposed to electrical fields, [88-91] and have been already implemented in FETs,<sup>[87]</sup> resistive switching based nonvolatile memories,<sup>[92–98]</sup> and electronic synapses. [99,100] Other wide bandgap 2D layered materials that may adhere to the 2D semiconducting channel by van der Waals attraction may also work well as gate dielectric in 2D-FETs. More intense research in this direction should result in a higher performance and faster development of this technology.

After device construction, postprocessing (e.g., vacuum annealing) is often employed to remove impurities at the metal/2D material interface (i.e., polymer residues, water and/or oxygen molecules on the channel<sup>[28,101–103]</sup>), improve the adhesion of the metallic contacts,<sup>[104]</sup> and reduce metal/2D materials contact resistance.<sup>[105]</sup> The contact resistance of metal/2D materials is considered one of the factors that most degrades the performance of 2D-FETs (i.e., reduce effective mobility, produce hysteresis, limit max current).<sup>[106,107]</sup> Although there are some known strategies to reduce it, such as patterning edge contacts,<sup>[108]</sup> using metallic 2D layers<sup>[109]</sup> and introducing heavy doping,<sup>[110]</sup> it remains a key bottleneck to the performance of 2D devices.

It is important to emphasize that all the processes involved in the fabrication of the devices should be scalable (not only the synthesis of the 2D material). Up to now, most investigations in this field used EBL to pattern the electrodes and/or channel of the devices. [111,112] In situ metallic electrode deposition within the vacuum chamber of focused ion beam (by metal gas decomposition using ion gun) has also been often employed. [113] However, these methods do not allow patterning several devices in parallel, and consequently they are not scalable. Furthermore, this represents a very strong limitation in terms of characterization, as very few devices can be fabricated and this does not allow collecting statistical information about the devices (i.e.,

yield, device-to-device variability). This is by far the main criticism to nearly all academic publications in this field: they only show one, two, three, few devices, and consequently their findings may not be reliable/trustable. Using scalable processes for metal deposition (i.e., electron beam evaporator, sputtering) and device shape patterning (photolithography), plus collecting statistical information (i.e., yield, variability) of the devices is really the way to go. Refs. [53,114,115] may be taken as good examples of 2D material—based FET fabrication using only scalable approaches.

Overall, there is nothing impeding scientists the use of scalable processes to fabricate their devices. The methods are there, and they have been already used in some investigations. [53,114,115] The problem is that fabricating hundreds of devices in a scalable manner and provide statistical information about their performance is much more complex, expensive and time consuming than fabricating one single transistor via mechanical exfoliation and EBL, plus the data obtained using scalable approaches are normally not so spectacular. Therefore, many academics prefer to get nice data for their papers, even if they have to use unrealistic fabrication approaches that are useless for the development of real 2D material–based FET technology. Only a more technology-oriented mentality would lead to remarkable improvements in this field.

# 3. Effect of the Electrode/Channel Contact Resistance

When semiconducting 2D materials are connected to metal electrodes, a Schottky barrier is formed at the interface due to the misalignment energy levels of the two materials, which results in an effective contact resistance that limits the device performance. The Schottky barrier will absorb a non-negligible amount of the voltage applied, reducing the real potential difference at the channel region, and thus producing a lower effective charge carrier mobility. This results in the degradation of the electrical performance of the 2D-FET (i.e.,  $I_{DS}$ ,  $V_{th}$ ,  $\mu$ ).

The Schottky barrier at the metal/channel interface can be lowered by introducing a postprocessing annealing step (i.e., vacuum, inert gas), although this always increases the complexity and cost of the fabrication process. Another option would be to simply use a material for the electrodes with a work function that matches the electron affinity of the semiconducting channel. However, even in that case a Schottky barrier may still exist due to strong Fermi level pinning.<sup>[79]</sup> This effect has been extensively investigated in devices with metal-MoS<sub>2</sub> contacts, but seems to be potentially less pronounced in other TMDs<sup>[116,117]</sup>—because the forming energy of chalcogen vacancies (e.g., S, Se) in other TMDs (i.e., MoSe2, WS2) is larger than that of sulfur vacancies in MoS<sub>2</sub>, which may reduce the number of vacancies in such TMDs compared to MoS<sub>2</sub>. Doping the metal/channel interface with substoichiometric oxides  $(MoO_{x_2}^{[118,119]} TiO_{x_2}^{[120]} and AlO_{x_2}^{[110]})$  and/or  $NO_2^{[121]}$ can efficiently lower the Schottky barrier, due to the suppression of Fermi level pinning at the interface of 2D materials and metal electrodes. Another option is to insert a buffer layer between the metal and the 2D channel, such as graphene<sup>[122]</sup> or a thin insulating dielectric layer (such as 2 nm MgO, [123]

1 nm TiO<sub>2</sub>, [124] or 1–2 layer 2D insulating h-BN[85,125]), to form a tunneling buffer layer resulting in a metal-insulator-semiconductor (MIS) structure, which has shown a remarkable reduction of the Schottky barrier with small tunneling resistance.

## 4. Effect of the Dielectric Environment

#### 4.1. Gate Dielectric

In early studies, back-gated MoS2 FETs on SiO2 dielectric wafers were commonly used; however, the performance of these devices does approach to that theoretically predicted. This is most likely due to random charged impurities or Coulomb impurities within the 2D semiconducting channels<sup>[126]</sup> or on their surfaces, which can cause Coulomb scattering—that is the dominant scattering effect reducing the performance of 2D-FETs. [7,127] Charged impurities originate from a variety of impurity sources, such as residual metal ions in the dielectric, impurities at the 2D material/substrate interface, and residual solvent or adsorbed gas molecules during the device fabrication. These nonidealities act as point charges and interact with electrons/holes in the 2D material through long range Coulomb interactions. Intrinsic electrical properties of monolayer  $MoS_2$  are known to be affected by charged impurities.<sup>[128,129]</sup> A promising avenue to improve the mobility of 2D-FET devices is the effective reduction and screening of extrinsic scattering centers. In addition, the carrier transport in the 2D material channel of the FETs can be degraded by remote interaction between the electrons and the optical phonons at the surface of the substrate.

These unfavorable interactions can be weakened by using a proper dielectric environment,[10,129] a solution that has also been proposed for graphene FETs.[130,131] By more effectively suppressing Coulomb scattering effects from charged impurities at the channel/dielectric interface, a monolayer MoS<sub>2</sub> device on a high-k dielectric environment has exhibited high room temperature mobility up to ≈150 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.[129] Large dielectric constant of high-k material contributes to the reduction of effective size of Coulomb impurities.[129] Moreover, the room temperature mobility of MoS2 channels in FETs is theoretically predicted to increase with increasing dielectric constant of the dielectric film in contact with it  $(k_{\rm HfO2}>k_{\rm Al2O3}>k_{\rm SiO2})$ .[129]

Until now, a large number of dielectrics have been experimentally used to get better device performance, including highk materials, [129] polymers, [132] self-assembled organic insulator and 2D insulator h-BN.[133] However, little attention has been paid to the scaling of the insulators toward sub-1 nm equivalent oxide thickness (EOT) as required for modern electronic devices, which would fully exploit the scaling potential of 2D materials. In particular, standard dielectrics such as SiO2 and high-k oxides (e.g., Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>) are amorphous, especially when grown in thin layers, and thus contain numerous defects. These defects severely degrade the reliability of 2D-FETs and make them problematic for further integration. Charge exchange between oxide defects and trap states in the channel leads to the ubiquitous hysteresis[134-137] and long-term drifts of the gate transfer characteristics<sup>[135,138,139]</sup>—often referred in Si technologies as bias-temperature instabilities (BTI).[140,141] Recently, an attempt to improve the quality of comparably thin (10 nm) HfO<sub>2</sub> films has been undertaken by crystallizing them using rapid thermal annealing (RTA), [142] but this methodology appears to be unsuitable to improve the performance of the devices due to the limited thermal stability of most TMDs.

In order to reduce these imperfections, the use of 2D layered dielectric films has been considered as dielectric candidate for 2D-FET devices, as they present an atomically flat surface free of dangling bonds. [133] Devices with h-BN dielectrics have recently exhibited considerably improved channel mobility,[133] as well as reduced hysteresis and BTI drifts.[135,143] Additionally, the fact that the lateral thermal conductivity of h-BN is very high (360 W m<sup>-1</sup> K<sup>-1</sup>) compared to SiO<sub>2</sub> (0.69-1.4 W m<sup>-1</sup> K<sup>-1</sup>),  $HfO_2$  (0.3–2.55 W m<sup>-1</sup> K<sup>-1</sup>) and  $Al_2O_3$  (0.49–2.3 W m<sup>-1</sup> K<sup>-1</sup>), [144] is also very attractive from a reliability point of view, as it can slow down the dielectric breakdown process.[88] It is worth noting that h-BN has a low dielectric constant of 5.06 and a small bandgap of about 6 eV,[145] which from a theoretical point of view might raise concerns regarding excessive gate leakage currents<sup>[146]</sup> (and consequently low ON/OFF current ratios) in devices requiring sub-1 nm EOT scaling. However, sub-1 nm (<3 layers thick) h-BN stacks have exhibited good ability to block leakage current—the I-V curves collected via CAFM in monolayer (0.33 nm thick) h-BN show that the voltage needed to raise current above the noise level (also named onset voltage,  $V_{\rm ON}^{[88]}$ ) is  $\approx 0.75$  V, [88,144] which is similar to that observed in 0.4 nm Al<sub>2</sub>O<sub>3</sub>.[147] More investigations on the leakage current of sub-1 nm h-BN compared to traditional dielectrics are required. The combination of different insulating materials stacked one of each other (i.e., Al<sub>2</sub>O<sub>3</sub> on h-BN)—a solution widely employed by the industry<sup>[148]</sup>—may be a potential solution that also deserves further exploration.

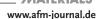

As an alternative to high-k oxides and h-BN, crystalline calcium fluoride (fluorite and CaF2) has recently been suggested as a gate insulator in MoS<sub>2</sub> FETs.<sup>[146]</sup> This material has a higher bandgap of 12.1 eV and dielectric constant of 8.43, which makes tunnel leakages negligible even for sub-1 nm EOT. At the same time, the F-terminated surface of CaF2 epitaxially grown on Si (111) is inert and contains a very low amount of defects, and can form a quasi van der Waals gap interface with MoS<sub>2</sub>. First prototypes of bare-channel back-gated MoS<sub>2</sub> FETs with only 2 nm thick CaF2 insulators have already shown ON/ OFF current ratios up to 107, subthreshold swings down to 90 mV decade<sup>-1</sup>, and a hysteresis as small as that of conventional Si/high-k FETs<sup>[146]</sup> (see Figure 3).

It should be noted that this section mainly concentrated on different gate dielectrics in contact with MoS2 material. The results using other 2D semiconducting materials with TMD structure should lead to similar results. However, reliability studies using phosphorene and silicene should are very scarce, and more work in this direction is required.

### 4.2. Encapsulating Dielectric for Stability Purposes

Dielectric films can be also used to fully surround (i.e., encapsulate) the 2D semiconducting channel of the 2D-FETs, protecting them from adsorbates coming from the ambient. So far, the performance of 2D-FET transistors with channels made

Figure 3. a) Atomic structure of the quasi van der Waals interface between F-terminated  $CaF_2(111)$  and  $MoS_2$ . b) Transmission electron microscope image confirms  $MoS_2$  channel on about 2–2.5 nm  $CaF_2$  insulator. The gate transfer c) and output b) characteristics confirm reasonable performance of the  $CaF_2(2 \text{ nm})/MoS_2$  FETs. Reproduced with permission. [146] Copyright 2019, Springer Nature.

of TMDs, such as MoS<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub>, has not been ideal. However, the relatively low mobility of TMD channels is considered to be a limit for some FET based applications. As such, an intensive search for alternative 2D materials is currently in progress. The most interesting options among them are 2D counterparts of conventional materials, such as silicene<sup>[149]</sup> and phosphorene.<sup>[150]</sup> The narrow bandgaps of these materials are between the zero bandgap of graphene and the larger bandgap of TMDs (i.e., 1.8 eV for monolayer MoS<sub>2</sub><sup>[151]</sup>) and 2.0 eV for WSe<sub>2</sub><sup>[152]</sup>), which makes them attractive due to their (theoretically) higher carriers mobility. However, in addition to the poor quality when synthesized with scalable bottom-up methods, the main problem of these materials is their poor air stability.

At the moment, studies on silicene FETs are very rare due to the extremely poor air stability of this material, i.e., in ref. [153] it was demonstrated that silicene dissolves in air after about 2 min. As such, the fabrication of silicene FETs requires very complicated processing techniques in which the channel has to be encapsulated by a metallic substrate (in the bottom) and a dielectric (on the top), and the electrodes need to be created by patterning this metallic substrate after flipped transfer.[153] These techniques are currently not available to a wide research community, and they do not allow fabrication of multiple devices in parallel. In contrast, phosphorene FETs have been successfully fabricated by many groups. Phosphorene is also very sensitive to the ambient but allows air exposure up to several hours, though this should be minimized during device fabrication. After extended air exposure, the performance of phosphorene FETs would be degraded by physical changes (i.e., volume expansion, uneven surfaces) or chemical changes (i.e., alteration of electronic structure, generation of large Schottky barrier heights) which result from surface degradation. [2] In order to solve this problem, several attempts of encapsulation of phosphorene FETs with an AlO<sub>v</sub> layer, [154-156]

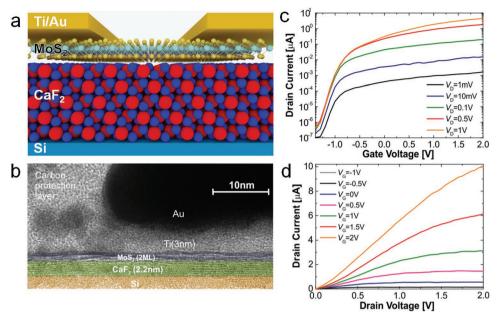

polymers<sup>[154,157]</sup> and 2D h-BN<sup>[158,159]</sup> have been reported. An efficient solution has been found only using conformal encapsulation schemes (see Figure 4).[160] Recently, at least 17 months of phosphorene FETs stability has been achieved using conformal Al<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub>/Teflon-AF encapsulation, with the latter scheme also leading to an improved device performance and reliability.[160,161] However, it is shown that the performance of phosphorene could be significantly degraded by Al<sub>2</sub>O<sub>3</sub> capping, resulting in a 5 times lower ON-state current and 3 times lower ON/OFF ratios, likely due to the moisture introduced during the ALD encapsulation process.<sup>[162]</sup> Recently, He et al.<sup>[163]</sup> demonstrated that van der Waals passivation of phosphorene FETs with dioctylbenzothienobenzothiophene (C8-BTBT) thin films allows to efficiently preserve the intrinsic properties of phosphorene. In addition, phosphorene FETs with ultraclean interfaces have been obtained by sandwiching the channel between two h-BN layers, and these devices exhibited a higher mobility of up to  $\approx 1350$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and ON/OFF ratio exceeding  $10^5$ at room temperature. However, long-term stability of phosphorene FETs encapsulated with layered materials still has to be proven, since some of these materials can be partially transparent. For instance, the devices from ref. [163] exhibit some signs of degradation already after about two weeks.

In **Table 2**, we list the performance of phosphorene based FETs, including structural information (channel length, width and thickness, device structure, including gate position, gate insulator thickness and contacts metal), measuring conditions, ON/OFF ratios and mobilities. It should be highlighted that, for research purposes, measuring in vacuum condition can be considered as another kind of dielectric environment, as the gaseous adsorbates (such as humidity and oxygen molecules) can be desorbed from surface of the 2D channel. This methodology results in higher device current measured in vacuum as compared to air. [102,103,164,165]

www.afm-journal.de

Figure 4. a) Encapsulation schemes typically used for BP FETs. Only conformal encapsulation has been found to guarantee long-term stability. b) Encapsulation with 25 nm  $Al_2O_3$  leads to at least 17 months stability of BP FETs even if the devices are intensively stressed and alternatively stored in the ambient c). Reproduced under the terms and conditions of the Creative Commons CC BY 4.0 International License. Copyright 2017, The Authors, published by Springer Nature.

In any case, it is important to highlight that performance degradation with the time due to poor stability introduces one uncontrollable variable more that can alter the reliability of the devices. This is important when considering device-to-device variability, a piece of information that is lacking in most 2D material—based FET reports.

# 5. Effect of the Channel Length

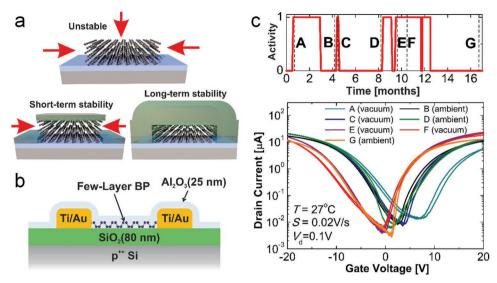

In order to achieve a better performance of the FETs (e.g., higher operation speed) and increase the amount of devices per chip (which also results in a higher performance at the circuit level), one common strategy consist on reducing the length of its semiconducting channel. However, this can produce some undesired phenomena, such as severe decrease of the ON/OFF current ratio, as well as a sharp increase in drain induced barrier lowing (DIBL) was observed during the scaling down of the channel length. These phenomena, also known as short channel effects, have been also observed in earliest reports, which used nonoptimized metal/2D material interface junctions.[166] Similar observations have also been reported in refs. [167,168]. Liu et al.[166] observed that the degradation of the electrostatic control from the gate could be more severe when the channel length is smaller than a limiting value (see Figure 5a). This characteristic length for the onset of short channel effects for planar transistors can be calculated by [169]

$$\lambda = \sqrt{\frac{\varepsilon_{\rm s}}{\varepsilon_{\rm ox}} t_{\rm s} t_{\rm ox}} \tag{3}$$

where  $\lambda$  is the characteristic length,  $\varepsilon_{\rm s}$  and  $\varepsilon_{\rm ox}$  are the permittivities of the 2D material semiconducting channel and the gate dielectric layer, and  $t_{\rm s}$  and  $t_{\rm ox}$  are the thicknesses of 2D materials semiconducting channel and gate dielectric layer. Following this formula, the characteristic channel length for 2D material

transistor can be optimized to a smaller value by using a thinner channel, a thinner gate dielectric layer or a gate dielectric layer with higher  $\varepsilon_{ox}$ . Consequently, by optimizing the dielectric layer (e.g., replacing by HfO2 or other materials with a higher permittivity), the predicted limiting or characteristic channel length for MoS<sub>2</sub> can be reduced down to ≈1–2 nm. [166,168] As shown in Figure 5a, for FETs using 5 nm thick MoS2 channels, the degradation rate of the ON/OFF ratio for short channel lengths is slower than for FETs using 12 nm thick MoS2 channels. [166] It was also observed that the mobility of the 2D material decreases severely when thinning the MoS<sub>2</sub> channel (see also Section 6). Experimental evidence of the influence of the channel thickness together with the channel length dependence has been reported in ref. [170]. The appearance of short channel effects in air as a function of channel length and channel thickness is shown in Figure 5b. In principle, short channel effect could be excluded by using longer channel or thinner channel (see Equation (3)). [79,170] In other words, thinning the channel is one possible way to make the device work when its channel has to be short.

In addition to these geometrical parameters, the quality of the electrode/channel junction and the intrinsic dielectric constant of the material selected for the channel need to be carefully engineered to suppress short channel effects in the 2D-FET. Ideally, the ON-current (or ON-resistance) of a device is supposed to be linearly dependent on the channel length; however, as shown in Figure 5c, a deviation typically occurs due to the additional metal–2D material contact resistance, [166,171] which results in a degraded lateral electrical field in the channel. In addition, the ON-resistance could be smaller when the channel is made of a 2D material with smaller dielectric constant.

Besides that, the mobility of  $MoS_2$  decreases with decreasing channel length in both back-gated (see Figure 5d) and top-gated configuration, [166,172,173] which may be attributed to two reasons. First, in 2D-FETs with metal/2D material contact resistance (which do not scale with channel length), the negative effect of the contact resistance would become more and more obvious

Table 2. Summary of BP FETs' structural parameters, measurement, and performance.

| Ref.  | L/W [μm]  | T [nm] | Preparation | Gate,<br>Gate dielectric                | Metal     | Annealing                       | Encapsulation | Measurement condition                       | Ohmic<br>contact   | ON/OFF<br>ratio                  | h mobility [cm $^2$ V $^{-1}$ s $^{-1}$ ]       | e mobility<br>[cm² V <sup>-1</sup> s <sup>-1</sup> ] |

|-------|-----------|--------|-------------|-----------------------------------------|-----------|---------------------------------|---------------|---------------------------------------------|--------------------|----------------------------------|-------------------------------------------------|------------------------------------------------------|

| [219] | 8.7/7     | 8      | ME          | Back,<br>285 nm SiO <sub>2</sub>        | 5 nm Ti   | No                              | No            | Dark, 10 <sup>-5</sup><br>mbar              | Yes                |                                  | -                                               |                                                      |

|       |           |        |             |                                         |           |                                 |               |                                             |                    | >10³ (h),<br>10 (e)              | 0.5                                             |                                                      |

| [220] | 0.45/1.85 | 12     | ME          | Back,<br>285 nm SiO <sub>2</sub>        | 5 nm Ti   | No                              | No            | 300 K                                       |                    | 600                              | 35                                              | 12                                                   |

|       |           |        |             |                                         |           |                                 |               | 4 K                                         |                    | 40 000                           | 31                                              | 14                                                   |

|       | 0.15/2    |        |             |                                         |           |                                 |               | 300 K                                       |                    | 50                               | 10                                              | 4                                                    |

|       |           |        |             |                                         |           |                                 |               | 4 K                                         |                    | 10 000                           | 8                                               | 4                                                    |

| [107] | 3/-       | 18.7   | ME          | Back,<br>90 nm SiO <sub>2</sub>         | 30 nm Ni  | No                              | No            | Ambient                                     | Yes                | ≈10 <sup>2</sup>                 | 170.5                                           |                                                      |

|       |           |        |             |                                         | 30 nm Pd  |                                 |               |                                             |                    | -                                | 186.5                                           |                                                      |

| [221] | 17.3/5.9  | 8      | ME          | Back,<br>290 nm SiO <sub>2</sub>        | 5 nm Ti   | No                              | No            | 10 <sup>-6</sup> Torr, 295 K                | Yes                | 10 <sup>4</sup>                  | 103 (positive<br>sweep), 38<br>(negative sweep) |                                                      |

| [30]  | 1.6/4.8   | 5      | ME          | Back,<br>90 nm SiO <sub>2</sub>         | 5 nm Cr   | No                              | No            |                                             | Yes                | $\approx 10^5$                   |                                                 |                                                      |

|       | 4.5/2.3   | 5      |             |                                         | (Or Ti)   |                                 |               |                                             | Yes                |                                  | 55                                              |                                                      |

|       |           | 8      |             |                                         |           |                                 |               |                                             |                    |                                  | 197                                             |                                                      |

|       |           | 10     |             |                                         |           |                                 |               |                                             |                    |                                  | 984                                             |                                                      |

| [40]  | 1/–       | 5      | ME          | Back,<br>90 nm SiO <sub>2</sub>         | 20 nm Ti  | No                              | No            |                                             | Yes                | ≈10 <sup>4</sup>                 | 286                                             |                                                      |

| [222] | 1.1/2.6   | 7.5    | ME          | Back,<br>300 nm SiO <sub>2</sub>        | 100 nm Au | Yes                             | Yes           | $5 \times 10^{-5}$ Tor, RT                  | Yes                |                                  |                                                 |                                                      |

| [223] | 1/-       | 5      | ME          | Back,<br>300 nm SiO <sub>2</sub>        | 1 nm Ti   | No                              | No            | RT                                          | Yes                | >10 <sup>5</sup>                 | 205                                             |                                                      |

| [158] |           | 8      | ME          | Back, 300 nm<br>SiO <sub>2</sub> + h-BN | 2 nm Cr   | Yes (before putting electrodes) | Yes           | 1.7 K                                       | Yes                |                                  |                                                 |                                                      |

|       |           | ≈15    |             |                                         |           |                                 |               | 300 K                                       |                    | 10 <sup>5</sup>                  | 1350 (FET<br>mobility)                          |                                                      |

|       |           |        |             |                                         |           |                                 |               |                                             |                    |                                  | 790 (Hall<br>mobility)                          |                                                      |

|       |           |        |             |                                         |           |                                 |               | 1.7 K                                       |                    | 108                              | 2700 (FET<br>mobility)                          |                                                      |

|       |           |        |             |                                         |           |                                 |               |                                             |                    |                                  | 1500 (Hall<br>mobility)                         |                                                      |

| [224] |           | 5.7    | ME          | Back,<br>300 nm SiO <sub>2</sub>        | 5 nm Ti   | No                              | Yes by BN     | Vacuum, 300 K                               |                    |                                  | >10                                             |                                                      |

|       |           | 4.5    |             |                                         |           |                                 | No            | Vacuum                                      |                    |                                  |                                                 | 10 to 100                                            |

|       |           | 5.7    |             |                                         |           |                                 | Yes by BN     | Vacuum, 200 K                               | No (h), Yes<br>(e) | 10 <sup>5</sup>                  | 86                                              | 62                                                   |

|       |           |        |             |                                         |           |                                 | No            |                                             | No (h) and (e)     |                                  | 118                                             | < 5                                                  |

| [218] |           | <10    | LE          | Back,<br>300 nm SiO <sub>2</sub>        | 20 nm Ni  | No                              | No            | $<$ 5 $\times$ 10 <sup>-4</sup> Torr, RT    | Yes                | 10 <sup>4</sup>                  | 25.9                                            |                                                      |

| [225] |           | 20     | ME          | Liquid                                  | 5 nm Cr   | Yes                             | No            | 220 K                                       |                    | ${\approx}5\times10^3$           | ≈190                                            | ≈20                                                  |

| [226] |           | 14–28  | ME          | Back,<br>200 nm SiO <sub>2</sub>        | 8 nm Cr   | No                              | No            |                                             | Yes                | 10 <sup>4</sup> -10 <sup>5</sup> | 247 (Zigzag), 392<br>(Armchair)                 |                                                      |

| [227] |           | 4.5    | ME          | Back,<br>300 nm SiO <sub>2</sub>        | 5 nm Cr   | No                              | No            | 405 nm laser,<br>≈10 <sup>-7</sup> mbar, RT | Yes                | 105                              | 142                                             |                                                      |

Table 2. Continued.

| Ref.  | L/W [μm] | T [nm] | Preparation | Gate,<br>Gate dielectric                            | Metal     | Annealing                  | Encapsulation | Measurement condition                                             | Ohmic contact      | ON/OFF<br>ratio | h mobility [cm $^2$<br>V $^{-1}$ s $^{-1}$ ] | e mobility<br>[cm² V <sup>-1</sup> s <sup>-1</sup> ] |

|-------|----------|--------|-------------|-----------------------------------------------------|-----------|----------------------------|---------------|-------------------------------------------------------------------|--------------------|-----------------|----------------------------------------------|------------------------------------------------------|

| [228] |          | 4.8    | ME          | Back,<br>300 nm SiO <sub>2</sub>                    | 5 nm Cr   | No                         | No            | 405 nm laser<br>with 40 mV,<br>≈10 <sup>-8</sup> mbar, RT         | Yes                |                 | 214.8                                        | 1                                                    |

| [49]  |          | 7.4    | LE          | Back,<br>270 nm SiO <sub>2</sub>                    | 15 nm Ti  | Material and device anneal | No            | Ambient                                                           | No                 | 10 <sup>3</sup> | 0.58                                         |                                                      |

| [229] |          | 11.5   | ME          | Top, 20 nm<br>Al <sub>2</sub> O <sub>3</sub> (ALD)  | 5 nm Ti   | No                         | Yes           | Ambient, RT                                                       | Yes (e), No<br>(h) | 500             |                                              |                                                      |

| [230] | 10.6/2.7 | 15     | ME          | Back, 25 nm<br>Al <sub>2</sub> O <sub>3</sub> (ALD) | 1.5 nm Ti | No                         | Yes           | Ambient                                                           | Yes                | >103            | 310                                          | 89                                                   |

| [231] | ≈150/5   |        | EE          | Back,<br>300 nm SiO <sub>2</sub>                    | 3 nm Ti   | Yes                        | No            | Ambient                                                           | Yes                | 104             | ≈7.3                                         |                                                      |

| [36]  | 1 μm     | 8      | ME          | Back,<br>90 nm SiO <sub>2</sub>                     | Ni        | No                         | No            | Dark, $2 \times 10^{-4}$<br>mbar, 300 K                           | Yes                |                 |                                              |                                                      |

|       |          |        |             |                                                     |           |                            |               | 633 nm with 250 mW cm $^{-2}$ , 2 $\times$ 10 $^{-4}$ mbar, 300 K |                    |                 |                                              |                                                      |

|       |          |        |             |                                                     |           |                            |               | Dark, $2 \times 10^{-4}$<br>mbar, 20 K                            | No                 |                 |                                              |                                                      |

|       |          |        |             |                                                     |           |                            |               | 633 nm with 250 mW cm $^{-2}$ , $2 \times 10^{-4}$ mbar, 20 K     |                    |                 |                                              |                                                      |

| [232] | 1.5 µm   |        | ME          | Back,<br>200 nm SiO <sub>2</sub>                    | 50 nm Au  | Yes                        | Yes           | Ambient, RT                                                       | Little barrier     | 4               |                                              |                                                      |

| [233] |          |        | ME          | Back,<br>300 nm SiO <sub>2</sub>                    | 10 nm Cr  | No                         | No            |                                                                   | Yes                | <10             | 721                                          |                                                      |

Note: L: channel length; W: channel width; T: channel thickness; ME: mechanical exfoliation; LE: liquid exfoliation; EE: electrochemical exfoliation.

when it becomes more comparable to the channel resistance during downscaling. And second, it could be possible that the velocity of the charge carriers almost/completely saturates at shorter channel lengths.<sup>[166]</sup> Based on the simulation results from ref. [174] (which studied MoS<sub>2</sub> and FinFET transistors with channel lengths down to 10 nm), even though 2D MoS2 channels showed better suppression of short channel effects than Si channels, their ON-state currents are lower than in commercial FinFETs (>1 mA  $\mu m^{-1}$  based on ITRS) due to the low carrier saturation velocity of MoS2. Nevertheless, current density >400  $\mu A~\mu m^{-1}$  was already demonstrated in monolayer MoS $_2$ with 10 nm top gates.[175]

However, we note that all the literature reports discussed above have studied short channel effects on experimental 2D-FET technologies that have not been fully optimized. For instance, further development of recently reported devices using 2 nm CaF<sub>2</sub>[146] and even 10 nm HfO<sub>2</sub>[142] might allow further minimization short channel effects for channel lengths in the several nanometer regime.

### 6. Effect of the Channel Thickness

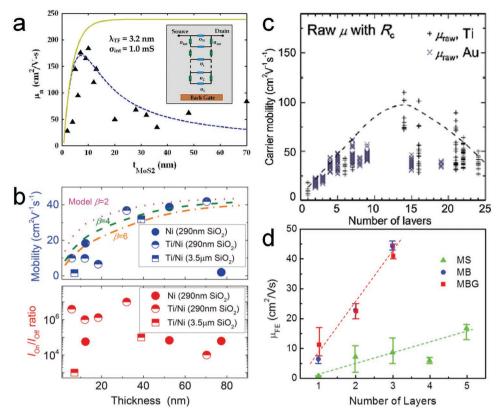

Since mobility and ON/OFF current ratio are important performance benchmarks of 2D material FETs for logic applications, their dependence on the thickness of the MoS2 channel has been discussed in several reports.[79,176-181] Although the reported mobility values show large dispersion, two observations are quite repetitive: i) there is an obvious trend suggesting that thicker MoS2 channels produce a higher mobility in the thin few-layer regime and ii) the increase of the mobility will slow down when the thickness reaches a critical value or range. Alternatively, the mobility might decrease in thicker channels because of the finite interlayer conductivity and accumulation of interlayer resistance.[79]

Das et al.<sup>[79]</sup> investigated room temperature mobility values of back-gated SiO<sub>2</sub>-supported MoS<sub>2</sub> FETs with channel thicknesses range from 2 to 70 nm (see Figure 6a). Based on their results, the channel thickness that provides the highest performance is in the range of 6-12 nm, the mobility increases monotonically with increasing channel thickness before this range (6-12 nm). The nonmonotonic trend after this range can be readily explained with a resistor network model (see the inset of Figure 6a). As the source and drain electrodes are connected only directly to the top  $MoS_2$  layer, additional interlayer resistance contributions ( $\sigma_{int}$  is the interlayer conductivity) are involved when charges flow along the lower layers, which means that the total access resistance will largely increase in 2D-FETs with thicker channels. Moreover, the gating has a higher impact in the 2D layer in contact with the gate dielectric, and screening results in a decreasing number of charges for the top MoS<sub>2</sub> layers.<sup>[79]</sup> These two factors can

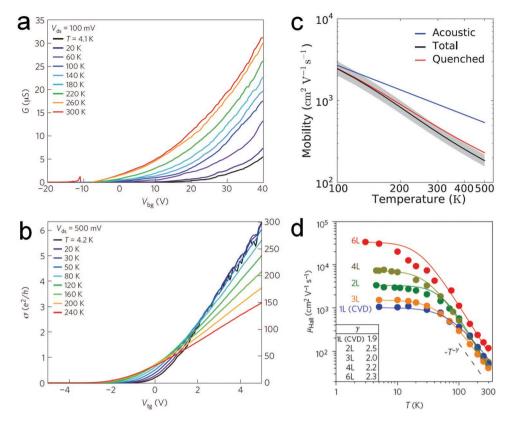

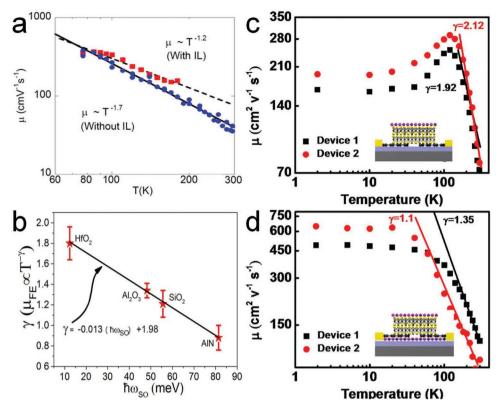

www.afm-journal.de