# Cryogenic Characterization of NH<sub>3</sub> Post Oxidation Annealed 4H-SiC Trench MOSFETs

Submitted: 2018-08-22

Revised: 2018-12-10

Accepted: 2019-02-12 Online: 2019-07-19

Judith Berens<sup>1,3,a\*</sup>, Gregor Pobegen<sup>1,b</sup>, Thomas Aichinger<sup>2,c</sup>, Gerald Rescher<sup>2,d</sup> and Tibor Grasser<sup>3,e</sup>

<sup>1</sup>KAI GmbH, Europastrasse 8, 9524 Villach, Austria

<sup>2</sup>Infineon Technologies Austria AG, Siemensstrasse 2, 9500 Villach, Austria

<sup>3</sup>Institute for Microelectronics, TU Wien, Gusshausstrasse 27-29, 1040 Vienna, Austria <sup>a</sup>JudithVeronika.Berens@k-ai.at, <sup>b</sup>Gregor.Pobegen@k-ai.at, <sup>c</sup>Thomas.Aichinger@infineon.com, <sup>d</sup>Gerald.Rescher@infineon.com, <sup>c</sup>grasser@iue.tuwien.ac.at

Keywords: 4H-SiC, interface traps, mobility, trench MOSFET, NITs, NH<sub>3</sub> POA, NO POA, TDRC

**Abstract.** We employed the thermal dielectric relaxation current method (TDRC) for the cryogenic characterization of ammonia (NH<sub>3</sub>) post oxidation annealed 4H silicon carbide (4H-SiC) trench MOSFETs. We studied differences and similarities between annealing in nitric oxide (NO) and NH<sub>3</sub>. In NO and NH<sub>3</sub> annealed trench MOSFETs, the same type of traps was found near the conduction band edge of 4H-SiC. The TDRC-signal consists of two peaks caused by interface states with a thermal emission barrier of 0.13 eV and near interface traps (NITs) with an emission barrier of approximately 0.3 eV. Significantly more interface traps close to the conduction band edge were found for the NH<sub>3</sub> annealed devices compared to the NO annealed ones. Our TDRC results indicate that NH<sub>3</sub> post oxidation anneal (POA) affects trap levels in a different way than NO POA.

## Introduction

SiC is an attractive material for high-power MOSFETs because of its high breakdown field strength. As opposed to other wide band gap semiconductor materials its native oxide is silicon dioxide (SiO<sub>2</sub>) [1], which allows to transfer processing knowledge from silicon technology. One drawback of SiC MOSFETs is that currently achieved inversion channel field effect mobilities are still far lower [1, 2] than the bulk mobility because of trapping at and near the SiC/SiO<sub>2</sub> interface. In order to reduce trapping, a POA can be performed. At the moment, nitric oxide (NO) is the most common annealing gas leading to significantly improved MOSFET performance and reliability [3, 4, 5]. However, it has been reported that an even higher mobility can be achieved by NH<sub>3</sub> anneal [6]. In order to identify the nature of the defects responsible for the mobility degradation and to investigate differences in trap level densities between NO and NH<sub>3</sub> annealed devices, we investigated n-channel trench MOSFET test structures using TDRC measurements. So far, other research groups have applied TDRC only to n-MOS structures or lateral MOSFETs [7, 8, 9]. Also, NH<sub>3</sub> annealed MOS structures were mainly studied using capacitance voltage measurements (cf. [10]). In [10], a reduction of deep interface states was reported for NH<sub>3</sub> pre-oxidation annealed capacitors on 6H-SiC with additional N<sub>2</sub> or N<sub>2</sub>O POA compared to samples without the NH<sub>3</sub> pre-oxidation anneal.

In this work, we show that the same kind of trapping states are present in NO and NH<sub>3</sub> annealed trench MOSFETs. However, both gases affect these traps differently.

## **Experimental**

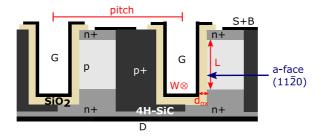

Differently annealed n-channel trench MOSFETs were fabricated on  $4^{\circ}$  off-axis, n-type 4H-SiC substrates. The SiO<sub>2</sub> gate oxide was deposited by chemical vapor deposition with subsequent POA in N<sub>2</sub>, NO or NH<sub>3</sub> (NH<sub>3</sub> (1):  $t_1$ min @  $T_1$ °C, NH<sub>3</sub> (2):  $t_2 = 3t_1$  @  $T_2 = T_1 + 15\%$ ). A cross-section of the studied trench MOSFETs can be found in Fig. 1.

Fig. 1: Cross-section of the studied trench MOSFET test structures. The channel forms in the  $(11\overline{2}0)$  crystal plane (a-face). L channel length, W channel width, G gate contact, S source contact, S bulk contact and D drain contact.

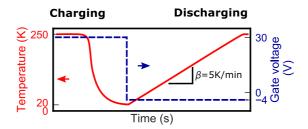

Fig. 2: TDRC measurement principle:  $V_{\rm ch}=30\,{\rm V}$  is applied to the gate while the temperature is decreased from  $T=250\,{\rm K}$  to  $20\,{\rm K}$  (approx. 1 hour). Then, the bias is switched to  $V_{\rm dis}=-4\,{\rm V}$  and the temperature gradually increased with  $5\,{\rm K/min}$ .

The TDRC measurement procedure is indicated in Fig. 2. Source and drain of the MOSFETs are grounded and the gate is charged with  $V_{\rm ch}=30\,{\rm V}$  at a temperature of 250 K . During charging, electrons are attracted to the SiC/SiO<sub>2</sub> interface where they can get captured in available trapping states. During the end of the charging process, the temperature is lowered to 20 K to slow down the emission of charges from their trapped state. Then, the gate bias is switched to  $V_{\rm dis}=-4\,{\rm V}$  (depletion) and the temperature is increased with a constant heating rate  $\beta=5\,{\rm K/min}$ . At certain temperatures, the thermal energy approaches the emission barrier and trapped electrons are thermally re-emitted into the 4H-SiC conduction band, leading to temperature dependent peaks in the gate displacement current I(T). This signal can be transformed into a density of states  $D_{\rm it}$  and an emission barrier  $E_{\rm C}-E_{\rm t}$  as described in [11], assuming the validity of Shockley-Read-Hall theory. For trench MOSFETs, the signal not only results from the channel region but from the whole trench SiC/SiO<sub>2</sub> interface. This area was extracted from CV curves at  $V_{\rm G}=15\,{\rm V}$ . The apparent channel mobility as an indicator of device performance was determined using the method of Ghibaudo [12].

### **Results and Discussion**

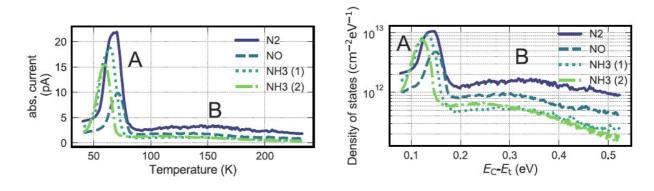

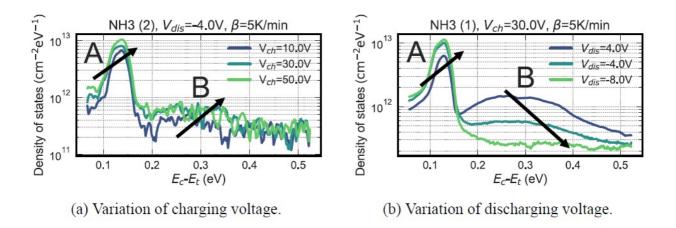

The results of the TDRC measurements are shown in Fig. 3. In general, the TDRC signal of all tested trench MOSFETs consists of two peaks representing two different trap levels. Peak A corresponds to interface traps with an emission barrier of  $0.13 \, \text{eV}$ , trap level B to near interface traps (NITs) with an emission barrier of  $0.3 \, \text{eV}$ . NITs were first described by Afanas'ev et al. [13]. The type of traps was determined by the variation of charging ( $V_{\text{ch}}$ ) and discharging ( $V_{\text{dis}}$ ) voltage (cf. [8, 14], Fig.4a and 4b). All studied POAs show the same qualitative results. The measured density of trap states in both peaks increases with higher  $V_{\text{ch}}$  indication a larger amount of trapped electrons. For more negative  $V_{\text{dis}}$ , the devices show an increasing TDRC signal in peak A and a decreasing signal in peak B. This behavior is attributed to interface traps and NITs [8].

The highest interface state density  $D_{it}$  in peak A is measured for  $N_2$  annealed MOSFETs. For NO and NH<sub>3</sub> annealed devices, we see a reduced  $D_{it}$  near the conduction band edge compared to the inert anneal in N<sub>2</sub>. This supports results by McDonald et al. [15] and Soejima et al. [6] who observed

similar behavior on different lattice planes. We therefore conclude that NO and NH<sub>3</sub> POAs passivate interface traps (peak A) to a certain extent. Additionally, both NH<sub>3</sub> POAs lead to higher  $D_{\rm it}$  than NO with  $D_{\rm it}^{\rm NO} < D_{\rm it}^{\rm NH_3~(2)} \le D_{\rm it}^{\rm NH_3~(1)}$ . We can thus clearly see that NH<sub>3</sub> has a less effective annealing effect on this trap level than NO. Regarding the density of NITs (peak B), no reliable conclusions can be drawn with TDRC measurements because most NITs can tunnel directly into the conduction band and are therefore not detectable with state-of-the-art measurement equipment [8].

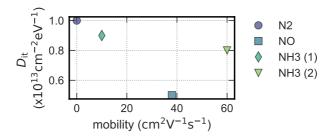

From earlier work, we expect a weak correlation between  $D_{it}$  (peak A) and the apparent channel mobility among other factors [14]. A reduced  $D_{it}$  compared to the  $N_2$  annealed MOSFET comes with an improved mobility. However, a higher mobility was measured for NH<sub>3</sub> (2) than for NH<sub>3</sub> (1) (cf. Fig. 5) even though the density of interface states of peak A is similar to NH<sub>3</sub> (1). Therefore, only a very weak correlation between peak A and the mobility may exist. Generally, a higher density of interface states in peak A was found after NH<sub>3</sub> POA than after NO POA and a lower one than after  $N_2$  POA (Fig. 5 and Fig. 3). From this, it can be concluded that peak A only partly contributes to the mobility degradation and that there are other factors, e.g. other trap levels, which have a stronger influence on the channel mobility. We assume a trap level with  $E_C - E_t > 0.13 \, \text{eV}$  to mainly cause the mobility degradation. Because [16] reports that traps close to the conduction band edge cause a low mobility, we suggest closer research on the correlation between NITs (peak B) and the apparent channel mobility with other measurement techniques.

Fig. 3: TDRC results of differently annealed trench MOSFETs. Left: I(T) plot. Right:  $D_{\rm it}$  vs. emission barrier calculated from the TDRC I(T)-plot.

Fig. 4: Energy distribution for a variation of the measurement parameters. All POAs lead to qualitatively similar results.

## **Summary**

TDRC measurements were carried out for trench MOSFETs annealed in different ambient. NO, NH<sub>3</sub> and N<sub>2</sub> annealed trench MOSFETs all show the same trap levels near the 4H-SiC conduction band edge. An interface trap level with an emission barrier of  $0.13 \, \text{eV}$  (A) and a near interface trap level with an emission barrier of  $0.3 \pm 0.1 \, \text{eV}$  (B) were found. In trap level A, we see a higher trap density for the NH<sub>3</sub> annealed devices compared to NO even though NH<sub>3</sub> (2) has a better apparent channel mobility. NH<sub>3</sub> (2) suffers from slightly less interface states than NH<sub>3</sub> (1) but has a strongly improved channel mobility. Therefore, peak A only has a very weak contribution to the degradation of the channel mobility. The main annealing effect of NH<sub>3</sub> POA, which leads to an improved channel mobility, is not identified so far. It presumably takes place in peak B (no conclusion possible with TDRC) or towards midgap. NO and NH<sub>3</sub> POA lead to the reduction of the interface trap level (peak A), however, the annealing effect on NITs (peak B) cannot be evaluated with TDRC.

Fig. 5: Anti-correlation between  $D_{it}$  of peak A and Ghibaudo mobility for annealing in different ambients.

## Acknowledgment

This work was funded by the Austrian Research Promotion Agency (FFG, Project No. 860424 and 863947).

#### References

- [1] E. Pippel, J. Woltersdorf, H. Ö. Ólafsson, and E. Ö. Sveinbjörnsson: JAP 97.3 (2005), p. 034302.

- [2] V. V. Afanas'ev, A. Stesmans, F. Ciobanu, G. Pensl, K. Y. Cheong, and S. Dimitrijev: APL 82.4 (2003), pp. 568–570.

- [3] H. Yoshioka, T. Nakamura, and T. Kimoto: JAP 112.2 (2012), p. 024520.

- [4] G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, R. K. Chanana, R. A. Weller, S. T. Pantelides, L. C. Feldman, O. W. Holland, M. K. Das, and J. W. Palmour: IEEE EDL 22.4 (2001), pp. 176–178.

- [5] S. Dhar, L. C. Feldman, S. Wang, T. Isaacs-Smith, and J. R. Williams: JAP 98.1 (2005), p. 014902.

- [6] N. Soejima, T. Kimura, T. Ishikawa, and T. Sugiyama: Mater. Sci. Forum 740-742 (2013), pp. 723-726.

- [7] I. Pintilie, F. Moscatelli, R. Nipoti, A. Poggi, S. Solmi, L. S. Løvlie, and B. G. Svensson: Mater. Sci. Forum 679-680 (2011), pp. 346–349.

- [8] M. Krieger, S. Beljakowa, B. Zippelius, V. V. Afanas'ev, A. J. Bauer, Y. Nanen, T. Kimoto, and G. Pensl: Mater. Sci. Forum 645-648 (2010), pp. 463–468.

- [9] T. E. Rudenko, I. N. Osiyuk, I. P. Tyagulski, H.Ö. Ólafsson, and E.Ö. Sveinbjörnsson: Solid-State Electronics 49.4 (2005), pp. 545–553.

- [10] K. McDonald, L. C. Feldman, R. A. Weller, G. Y. Chung, C. C. Tin, and J. R. Williams: JAP 93.4 (2003), pp. 2257–2261.

- [11] P. T. Lai, J. P. Xu, C. L. Chan, and Y. C. Cheng: Electron Devices Meeting, Proceedings, 1999 Hong Kong (1999), pp. 46–49.

- [12] J. S. Uranwala, J. G. Simmons, and H. A. Mar: Solid-State Electronics 19 (1976), pp. 375–380.

- [13] G. Ghibaudo: IEEE Electronics Letters 24, No. 9 (1988), pp. 543–545.

- [14] V. V. Afanasev, M. Bassler, G. Pensl, and M. Schulz: physica status solidi (a) 162.1 (1997), pp. 321–337.

- [15] J. Berens. Cryogenic characterization of 4H-SiC high power MOSFET. Master Thesis. RWTH Aachen University, 2018.

- [16] G. Rescher, G. Pobegen, T. Aichinger, T. Grasser: Mater. Sci. Forum 897 (2017), pp. 143-146