# NBTI Degradation and Recovery in Analog Circuits: Accurate and Efficient Circuit-Level Modeling

K.-U. Giering<sup>®</sup>, K. Puschkarsky<sup>®</sup>, H. Reisinger, G. Rzepa, G. Rott<sup>®</sup>, R. Vollertsen, T. Grasser, and R. Jancke

Abstract—We investigate the negative-bias temperature instability (NBTI) degradation and recovery of pMOS-FETs under continuously varying analog-circuit stress voltages and thereby generalize existing digital-stress NBTI studies. Starting from our ultrafast NBTI measurements and an extensive TCAD analysis, we study two physics-based compact models for analog-stress NBTI including recovery. The high accuracy of both models is evidenced from single-FET analog-stress and circuit-level ring oscillator experiments. Their numerical efficiency allows direct coupling to circuit simulators and permits to accurately account for NBTI already during circuit design. Furthermore, one of the models calculates the time-dependent NBTI variability of single-FET and of circuit performance parameters. We demonstrate our NBTI models on a ring oscillator and calculate the mean drift and statistical distribution of its oscillation frequency.

Index Terms—Acceleration, aging, MOSFET circuits, MOSFETs, stress measurement, stress.

### I. INTRODUCTION

RECOVERY is a characteristic trait of the negative-bias temperature instability (NBTI) mechanism [1]–[3] and distinguishes it from many other transistor degradation mechanisms. However, modeling the (partial) decrease in NBTI degradation during phases of low stress is a considerable challenge. From a circuit designer perspective, investigating this feature in detail is desirable for several reasons. On the

Manuscript received November 26, 2018; revised January 25, 2019; accepted February 18, 2019. Date of publication March 11, 2019; date of current version March 2019. This work was supported by the European Union's Sev-Framework Programme for Research, Technological Development, and Demonstration (MoRV) under Grant 619234. The review of this paper was arranged by Editor A. J. Scholten. (Corresponding authors: K.-U. Giering; K. Puschkarsky.)

K.-U. Giering and R. Jancke are with the Fraunhofer Institute for Integrated Circuits, Division EAS, 01069 Dresden, Germany (e-mail: kay-uwe.giering@eas.iis.fraunhofer.de).

K. Puschkarsky is with Infineon Technologies AG, 85579 Neubiberg, Germany, and also with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria (e-mail: katja.puschkarsky@infineon.com).

H. Reisinger, G. Rott, and R. Vollertsen are with Infineon Technologies AG, 85579 Neubiberg, Germany.

G. Rzepa and T. Grasser are with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria (e-mail: grasser@iue.tuwien.ac.at).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2019.2901907

one hand, an accurate analog-stress NBTI model allows the controlled reduction of margins away from costly over-designs of analog circuits. Naturally, analog-stress models can also be used in digital design, as the digital signals can deviate from an idealized two-level shape, and features such as overshoots or finite signal edges can have an impact on the NBTI-induced drift of gate delay times and other gate characteristics.

On the other hand, an accurate NBTI model is essential in circuit topologies that rely on matching FETs. Imagine a differential pair circuit subject to NBTI-induced drifts  $\Delta_1$  and  $\Delta_2$  of its constituent FETs. Conservative degradation models can provide worst case bounds A and B such that  $0 \le \Delta_1 \le A$  and  $0 \le \Delta_2 \le B$ . The resulting estimate of the NBTI-induced mismatch  $|\Delta_1 - \Delta_2| \le \max\{A, B\}$  is usually prohibitively large, as designers expect the mismatch to be much smaller than single-FET drifts A, B. Notice that such models cannot bound the mismatch to |A - B|. One reason for the unattractive estimate is the lack of a lower bound on  $\Delta_1$ ,  $\Delta_2$  better than just 0. Such issues are resolved by NBTI models that fully account for recovery.

Worst case NBTI models traditionally consider timeindependent stress voltages [4]. Further empirical models, in parts proposed for hot carrier degradation (HCI) hot carrier degradation, still, neglect NBTI recovery but improve the degradation bound by accounting for time-dependent stress voltages [5]-[7]. Models including recovery were first proposed for digital stress voltages, such models use captureemission time (CET) maps [2], [8] or otherwise exploit the fact that the stress voltage takes on only two values [9]-[11]. In the CET map framework, periodic digital stress results in a closed-form solution [12]. Furthermore, it has been shown that stress patterns with a complicated periodic structure have an efficient numerical solution [13]. In analog circuits, the continuous stress voltage levels necessitate a more complex model of the defect dynamics: the differential equation of the Markov two-state NBTI model [2] has an efficient numerical solution for periodic analog stress voltages [14]-[16]. A complementary approach parametrizes the gate–source voltage  $(V_{\rm gs})$  dependence of CET maps [8] and traces an occupancy map during analog-stress [17].

Here, we discuss two accurate NBTI compact models including NBTI recovery for analog design [18], [19], and we compare their application focus. The present analog-stress

study combines the results of experiments, TCAD simulations and the compact modeling approaches. After summarizing our methods, we compare experimental and theoretical results on the NBTI aging of single transistors due to analog gate—source voltages. One of the analog-stress NBTI models was already validated against single-FET measurements, and its application to a differential pair (without a validation) was shown [18]. Here, we go several steps further and finally validate the models also against circuit-level (ring oscillator) experiments; moreover, we provide an error estimation of our NBTI predictions, and we give a detailed comparison of the defect-centric and the nondefect-centric NBTI models. We finally demonstrate how our model provides access to the NBTI variability of analog circuits.

## II. TECHNICAL APPROACH

## A. Experimental Setup

Both single-FET measurements and ring oscillator measurements were performed on production quality MOSFETs of a 130-nm technology with a 2.2-nm-thick plasma-nitrided gate oxide. Single-FET measurements on pMOSFETs with analog-stress patterns were performed using the ultrafast measure-stress—measure (MSM) technique [20] with a measurement delay of 1  $\mu$ s. Different analog-stress patterns (digital AC, sine, sawtooth, and inverse sawtooth) at a frequency of 0.5 and 2 kHz were applied at a stress temperature of  $T=125~{\rm ^{\circ}C}$  and maximum stress voltages of  $V_{\rm high}=-2.8{\rm V}$ .

Furthermore, we use two different ring oscillators (INV and NOR) to study the impact of NBTI on a circuit. The ring oscillators are placed between heater stripes to accelerate degradation with temperature and avoid the need for heating the chuck, which enables fast in-line measurements at the process control monitor. The experimental sequence includes frequency measurements before as well as after stress at operation voltage (room and stress temperature). After the temperature reaches the target temperature, the stress bias is applied and the frequency at stress voltage is measured *in situ* during stress without any introduced recovery. In addition, the frequency measurements at operation conditions before and after stress serve as a reference for the first frequency read-out at stress conditions.

# B. TCAD Modeling of NBTI

The extraction of defect properties and the simulation of defect kinetics with TCAD tools [21], [22] enable the parametrization and verification of the defect centric compact simulations presented in this paper. For the extraction of defect properties, we use extensive NBTI data measured on devices with large gate areas to obtain the mean degradation which holds information on a large ensemble of defects. The extended MSM (eMSM) scheme is usually applied here because the measurement cycles with stress phases followed by extended recovery phases for up to 100 ks comprise detailed information of both degradation and recovery [23]. Typically, two dominant degradation mechanisms are reported for such NBTI experiments: 1) charging and discharging of preexisting oxide defects, causing a recoverable shift which

Fig. 1. Two-state defects undergo transitions between a neutral state "1" and a positively charged state "2" with (mean) capture time  $\tau_c$  and emission time  $\tau_c$ . These defect-specific times sensitively depend on gate voltage and on temperature. Charging state "2" contributes to NBTI aging.

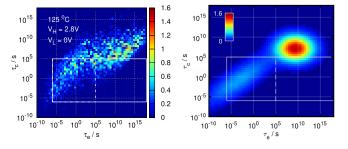

Fig. 2. Visualization of the CET maps in the NBTI DS model (left) and the approach of fitting to a CET map ansatz function (right). The dimension of the z-axis is mV. The white rectangles mark the windows of experimental characterization.

can be described by the four-state nonradiative multiphonon (NMP) model [2] and 2) a more permanent degradation which is probably due to hydrogen relocation in the near-interfacial region. Due to its complexity, the latter is modeled phenomenologically with a simple double-well (DW) model [24]. The distributions of the parameters of these two models are then optimized to obtain one set of defects which gives consistent results for all experiments with different stress times, temperatures, and voltages conducted on the technology of interest and is in line with physical values obtained from *ab initio* studies [25].

### C. Compact Modeling of NBTI

The NBTI two-state Markov model projects out metastable defect states and considers uncoupled oxide (NMP) and interface (DW) defects to cause NBTI aging (see [2]). Each defect occupies either an electrically neutral or a positively charged state, and transitions between the two states occur with characteristic capture and emission times that depend on  $V_{\rm gs}$ , temperature, and defect properties (Fig. 1). The threshold voltage shift  $\Delta V_{\rm th}$  results from a change of the oxide electric potential due to charged defects, and its (mean) value reads

$$\Delta V_{\text{th}}(t) = \sum_{k} \eta_k \times (w_k(t) - w_k(t_0)) \tag{1}$$

with  $w_k(t)$  the probability that defect k is charged at time t, and  $\eta_k$  its  $\Delta V_{\text{th}}$  contribution.

The properties of the contributing defects play an essential role. We account for their distribution by two distinct models: on the one hand, we employ a database with defect properties obtained in a TCAD analysis of experimental NBTI data (defect sampling model, DS). On the other hand, we model the "collective" defect behavior by a fit of experimentally obtained CET maps to an ansatz function (CET map-based model, CB). Both models calculate the mean  $\Delta V_{\rm th}$  independently but are calibrated to the same experimental data set.

### TABLE I

Comparison of the Defect Sampling and CET Map-Based NBTI Compact Models to the TCAD Reference. In the Simulation Effort Column, Example Time Corresponds to Calculating 100 ks of Sine Stress (100 MHz) on Single-Core Hardware. The Fast Parametrization of the CB Model Allows Its Application to a Large Number of Transistor Types. The Additional Experimental Effort for the Parametrization of the DS Model Enables the Calculation of NBTI Variability. Using Time-Dependent Defect Spectroscopy Information or Estimating Mean Defect Step Heights  $\eta$ , Prediction of NBTI Variability With the CB Model Is Currently Studied

| Model | base                       | defect<br>states | degrees of<br>freedom               | experimental<br>effort<br>[time / FET] | simulation<br>effort<br>[time / FET]      | feasible $V_{ m gs}$ patterns/ stress times | NBTI<br>varia-<br>bility | $V_{ m ds}$ dep. | freq.<br>dep. | advantage                                                  |

|-------|----------------------------|------------------|-------------------------------------|----------------------------------------|-------------------------------------------|---------------------------------------------|--------------------------|------------------|---------------|------------------------------------------------------------|

| TCAD  | 10 <sup>4</sup> individual | 2 and 4          | 24                                  | TDDS<br>+ eMSM                         | too high<br>for Spice                     | any / small                                 | yes                      | yes              | yes           | fundamental physical simulation                            |

| DS    | defects                    | ,                | 24 (via<br>10 <sup>4</sup> defects) | [1000h]                                | closed-form<br>for each<br>defect [10ms]  | periodic,<br>nested periods [13]<br>/ any   | yes                      | no               | no            | faster than TCAD,  NBTI variability, nested-periods stress |

| СВ    | $V_{ m gs}$ dep.           | 2                | 20                                  | TA-MSM<br>[50h]                        | closed-form<br>for each<br>CET bin [10ms] | periodic / any                              | in<br>dvp.               | no               | no            | faster than TCAD, fast parametrization                     |

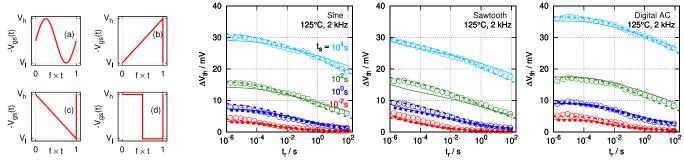

Fig. 3. Analog-stress MSM experiments periodically apply one of the four stress patterns: sine, sawtooth, inverse sawtooth, and digital AC (a to d, left). The stress voltage oscillates between the values  $V_l \le -V_{gs} \le V_h$ . Right (three plots): the MSM  $\Delta V_{th}$  recovery curves after four stress durations  $10^{-2}$ ,  $10^{0}$ ,  $10^{2}$ , and  $10^{4}$  s (bottom up in the plots) show a good agreement between experimental data (symbols), TCAD results (thick dashes), and compact model results (Solid: defect-sampling model. Dashed lines: CET-map based). The present setup uses a stress frequency of 2 kHz, a temperature of 125 °C, and stress voltages between  $V_l = 0.5$  V and  $V_h = 2.8$  V.

Both models assume a periodic  $V_{\rm gs}(t)$ . In applications, stress patterns can also feature multiple periodicities on different time scales, corresponding to, e.g., different IC power states, day–night cycles, and mission profile requirements; the DS model efficiently calculates also the effect of such patterns [13]. Table I compares both approaches to TCAD, Fig. 2 compares an exemplary CET map for the two models.

1) NBTI Compact Model Based on Defect Sampling: To be more specific, the DS model employs a TCAD-generated database that discretizes the dependence of the capture and emission time constants  $\tau_c$ ,  $\tau_e$  on  $V_{\rm gs}$  and temperature  $\vartheta$  for  $\sim 10^4$  technology-characteristic defects (see Section II-B). For each defect, we then solve the differential equation governing the time evolution of the occupation probability  $w_k$

$$\dot{w}(t) = a(t)w(t) + b(t)$$

$$w(t_0) = w_0$$

(2)

with  $a(t) = -\tau_{\rm e}^{-1}(t) - \tau_{\rm c}^{-1}(t)$  and  $b(t) = \tau_{\rm c}^{-1}(t)$ , using a numerically efficient algorithm [14]. Notice that the coefficients in the above-mentioned equation depend on the FET's stress signal  $t \mapsto V_{\rm gs}(t)$  and, therefore, are time dependent. The sum in (1) provides the time-dependent shifts  $\Delta V_{\rm th}(t)$  for each pFET in the investigated circuit.

2) NBTI Compact Model Based on CET Maps: The CB approach rewrites the sum in (1) in terms of CET maps [2], [8].

Measurements on wide FETs with a large number of defects allow a fast parametrization of these maps [17], replacing the single time constants of each individual defect by an analytical form of the capture and emission time map [see Fig. 2(b)] [8]. With the temperature-accelerated MSM (TA-MSM) technique, the temperature and stress voltage dependence of the CET maps can be obtained with very low measurement effort, and one activation energy map (AEM) is used to describe all dependencies [17]. The stress signal is approximated by a digital stress pattern for  $N_{\rm V}$  stress voltages, and the charging and discharging of the defects are described analogously to the charging function of a single RC element [12], eq. (2). Furthermore, the defect occupancy is described in a closed stress-time- and frequency-independent form [19]. The threshold voltage shift contributed from each N<sub>V</sub> differential AEMs is calculated as the integral of all defects being charged up to the stress time and not yet discharged at the recovery time. The total threshold voltage shift is then the sum over all threshold voltage shifts of the  $N_{\rm V}$  discrete stress voltages. A detailed description of the model can be found in [19].

### D. HCI Empirical Model

Furthermore, to estimate the full degradation in the ring oscillator experiments, the effect of hot carrier stress on carrier mobility is independently considered using the empirical

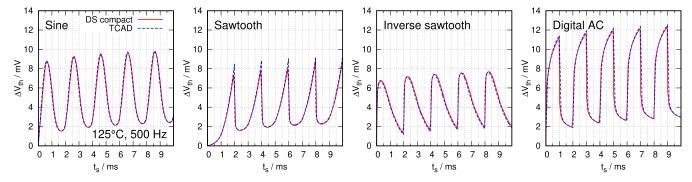

Fig. 4. Threshold voltage shift during analog stress. We compare the DS model results on  $\Delta V_{th}$  (solid line) to their TCAD reference (dashed line), for the first five periods of the stress phase. For all four stress patterns, both methods are in excellent agreement. The calculations use a stress frequency of 500 Hz, a temperature of 125 °C, and voltage values  $V_1 = 0.5$  V and  $V_h = 2.8$  V.

model proposed by Takeda and Suzuki [26] with a polynomial covering the gate-voltage dependence [27].

### III. EXPERIMENTAL MODEL VALIDATION

The NBTI compact models were calibrated to measurements at time-independent stress voltages, using a large number of combinations of  $V_{\rm gs}$  and temperature. We validate our model by comparing to additional NBTI measurement results: in a first step to single FETs under time-dependent stress voltages, in the second step to a whole ring oscillator circuit.

### A. Single FETs Under Analog Stress

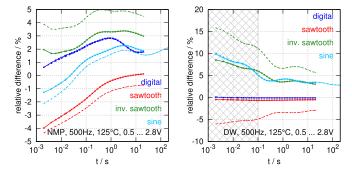

Our MSM experiments apply the analog  $V_{\rm gs}$  patterns of Fig. 3 (left), namely, a sine, sawtooth, inverse sawtooth, and digital pattern, during four different stress times ( $10^{-2}$  to  $10^4$ s) and then measure the NBTI relaxation. Fig. 3 (right) shows the good agreement between the measurement results (symbols) and the compact models (solid and dashed lines) as well as the TCAD simulation (thick dashes).

Although the degradation during the NBTI stress is experimentally inaccessible in the ultrafast measurement setup, we compare the predictions of the DS compact model to the more fundamental TCAD simulation. Fig. 4 shows the results for the first five stress periods and an excellent agreement. Fig. 5 displays in detail the relative  $\Delta V_{\text{th}}$  difference between TCAD and DS model simulations for the first 10<sup>4</sup> to 10<sup>5</sup> stress periods, separately for the fast NMP (left) and the slow DW defects (right). Increasing the time discretization of the stress pattern from  $\sim 100$  (dashes) to  $\sim 200$  points per period (solid lines) pushes the error to essentially below 5%. Presumably, the error is even much lower if the compact model and TCAD use exactly the same stress pattern discretization scheme (linear grid plus logarithmic grid near discontinuities of the stress pattern). The DW defects at small stress times (shaded region) show a larger deviation, but their  $\Delta V_{\rm th}$  contribution is very small then; their  $V_{\rm th}$  contributions larger than 1 mV have an error < 5% as well. The high accuracy of the DS model comes with the advantage of a few seconds versus several hours (TCAD) runtime for 10<sup>4</sup> stress periods.

Fig. 5. Threshold voltage shift for  $10^4$  and  $10^5$  analog-stress periods [patterns of Fig. 3 (left)]. The plots show the relative difference between the TCAD and the DS compact model results for the NMP defects (left) and the DW defects (right). Symbols mark the considered stress times. Whereas the time discretization of the stress pattern with  $\sim 100$  samples (dashes) has a larger error,  $\sim 200$  samples per period (solid lines) push the error to essentially below 5%. Besides high-accuracy relative to TCAD, the DS model furthermore has the advantage of a few seconds versus several hours (TCAD) runtime for  $10^4$  stress periods.

### B. Ring-Oscillator Aging

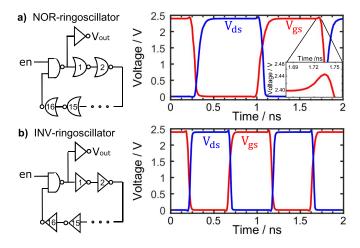

We further validate the NBTI models for the use in circuit simulators with ring oscillator frequency measurements at accelerated stress conditions. Simulations are performed with the previously described NBTI and HCS models integrated into the *Spectre* circuit simulator. To observe a measurable change in the ring oscillator frequency, we stress at a temperature of  $T = 175^{\circ}$ C and at  $V_{dd} = 2.4$  V, which is way above the use conditions of  $V_{\rm dd} \leq 1.5$  V. The resulting ring oscillator stress patterns are shown in Fig. 6(a) and (b). For each type of ring oscillator, eight fresh chips are measured and all measurement traces are shown in Fig. 7. Already after a short stress time (increase in  $V_{dd}$  to the stress voltage), the ring oscillator frequency during the first in situ readout decreases. Therefore, measurements and simulation at use condition before and after stress are used to determine the frequency f(t = 0) at  $V_{dd} = 2.4$  V for the unstressed ring oscillator, which is then used as a reference for the in situ frequency read-outs. The obtained initial ring oscillator mean frequencies and standard deviations at stress conditions are  $630 \pm 10$  MHz and  $990 \pm 15$  MHz for the NOR and INV ring oscillator, respectively. Note that ring oscillator frequencies

Fig. 6. Sketch of the schematic (left) and plot of the time-dependent pFET stress voltages  $V_{\rm gs}$ ,  $V_{\rm ds}$  (right) for the 17 stages (a) INV and (b) NOR ring-oscillator. Inset in the top-right plot: voltage overshoot in the oscillation pattern.

are very sensitive to FET variability. Variability of the initial frequencies is mainly due to different test chip positions on the wafer. Measurement uncertainty is 0.1 MHz.

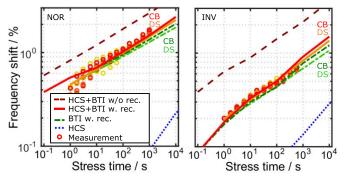

The relative frequency decrease for the *in situ* measurements (open circles) during stress at  $V_{dd} = 2.4 \text{ V}$  and  $T = 175 \text{ }^{\circ}\text{C}$ and the corresponding simulation results (lines) are shown in Fig. 7 on the left for the NOR and for the INV ring oscillator on the right. The frequency decrease due to the aging of the INV ring oscillator is clearly lower than that of the NOR ring oscillator for all stress times. This is due to the design of the two ring oscillators with the number and position of the aged transistors influencing the frequency: the NOR gate contains two stacked pMOS and two nMOS, whereas the INV gate consists only of one pMOS and one nMOS. After 1000 s of stress, the NOR and INV ring oscillator frequency decreased by  $1.65\% \pm 0.05\%$  and  $0.79\% \pm 0.03\%$ , average and sigma of all eight chips, respectively. In addition, the effect of the aged MOSFETs is even more enhanced switching back (switching time:  $\sim 1$  ms) to use conditions  $V_{\rm dd} = 1.5$  V (at T = 175 °C), showing a frequency shift of  $3.8 \pm 0.2\%$  and  $2.2 \pm 0.1\%$ , for the NOR and INV ring oscillator, respectively, in accordance with simulations. Both NOR ring oscillator and INV ring oscillator are sensitive to NBTI degradation, HCS is nearly negligible due to a low  $V_{gs}/V_{ds}$  crossing point for the NOR as well as the INV ring oscillator stress pattern (compare voltage intersections in Fig. 6(a) and (b). For the sake of completeness, even though HCS is nearly negligible for these circuits and stress conditions, we account for HCS (blue dashed lines). First findings indicate that the actual degradation is less than the addition of the single effects [28], but due to the low HCS component, this is not the focus of this paper.

We compare three NBTI simulations to the measurements: the DS and CB models (accounting for recovery, see Section II-C) and an empirical model without recovery ( $V_{\rm gs}$  and T dependent power law, measurement delay  $1\mu \rm s$ ). In addition, we simulate the frequency decrease due to HCS. As seen in Fig. 7, both recovery models, the CB (dashed

Fig. 7. Measurements of the relative frequency change over stress time in comparison with simulations for three different NBTI models for the NOR ring oscillator (left) and the INV ring oscillator (right). Measurements of eight chips are shown as open circles, lines correspond to simulation with the models. The simulated frequency shift solely due to NBTI is shown as dashed green lines (pure NBTI including recovery, CB dark green, DS bright green) and solid lines (NBTI and HCS with recovery: CB red, DS orange, and dashed dark red line corresponds to the empirical model disregarding recovery). The frequency shift solely due to HCS is indicated with blue dotted lines. Measurements and simulation with both NBTI recovery models show a very good agreement for all measured stress times.

dark green lines) and DS (dashed bright green lines) model, show a very good agreement with the measurement data. The dependence on stress time as well as the magnitude is perfectly covered by both NBTI recovery models and shows the applicability of single transistor aging models to circuit aging simulations. The differences between the two models are small: the NBTI induced frequency shift of the CB model (red line) lies slightly above the DS model (orange line) but with very similar dependence on the stress time. In contrast, the empirical model disregarding NBTI recovery (dashed dark red lines) overestimates the frequency shift by a factor of two for both ring oscillators (see Fig. 7). This demonstrates the necessity for an accurate recovery model. Hence, our NBTI models accounting for recovery strongly improve the accuracy of circuit aging simulations.

### IV. NBTI VARIABILITY AND RING-OSCILLATOR AGING

Our defect-sampling model allows to calculate the full distribution function [18] of the NBTI-induced ring oscillator frequency decrease, beyond the mean decrease calculated in the previous section. For simplicity, we focus on the NOR ring oscillator, and we neglect the small HCI contribution, parasitics, and additional load gates in the circuit.

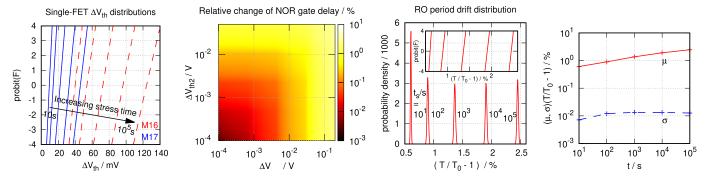

NBTI variability results from fluctuations in the density of NBTI-relevant defects as well as in the defect properties. We calculate the NBTI variability in a Monte Carlo (MC) simulation with Poisson distributed defect numbers and exponentially distributed step heights [29]–[31]. Each NOR gate in the oscillator comprises two pFETs, one of them (M16) is exposed to constant stress  $V_{\rm gs} = V_{\rm dd}$  and the other one (M17) to the oscillating pattern of Fig. 6. Fig. 8 (left) shows the  $\Delta V_{\rm th}$  distribution after different oscillator operation times in the range of 10 to  $10^5$ s (left to right). Employing  $10^5$  MC samples resolves the  $\Delta V_{\rm th}$  distributions up to four standard deviations away from the mean, and  $\Delta V_{\rm th}$  turns out to be normally

Fig. 8. Simulation of NBTI variability for the NOR ring oscillator at 170 °C and 2.4 V, using the DS model: NBTI variability leads to a *distribution* of threshold voltage shifts for the two pFETs M16 and M17 within each NOR gate, depending on operation time  $10^1$ ,  $10^2$ ,  $10^3$ ,  $10^4$ ,  $10^5$ s (from left to right in the leftmost plot). The  $V_{th}$  shifts cause an increase in the delay of each single NOR gate (second plot). This results in a distribution of the ring oscillator period T depending on operation time (third plot), which is well approximated by a normal distribution (inset plot). As calculated before, the distribution's mean  $\mu$  shifts to longer periods with increasing stress time, whereas its root-mean-square deviation  $\sigma$  levels off at large stress time (rightmost plot). While the broadening of the  $\Delta V_{th}$  distributions seems to be unbounded (left plot), the spread of the period durations T is bounded from above (right plot).

distributed in that range. A spice-level simulation provides the delay of a single NOR gate as a function of M16 and M17  $V_{\text{th}}$  shifts (second plot in Fig. 8). From that information, the distribution of the period T of the 17 stages ring oscillator is calculated, for operation times 10 to  $10^5$  s (third plot). The inset shows that the relative shift of T is essentially normally distributed in a wide range. Whereas the mean shift  $\mu$  of T increases with operation time, the broadening  $\sigma$  of the distribution levels off (right plot).

### V. CONCLUSION

We compared compact and TCAD models for NBTI including recovery. Even though the models have a simple parametrization from constant-stress MSM experiments, they correctly predict the analog-stress experimental results for single FETs and for entire circuits. From our analysis, we estimate that the DS model error for nonnegligible degradation is below 5%. The compact model complexity is linear in the number of pFETs and in the number of single-FET stressperiod time samples. However, in contrast to the TCAD reference, the compact model complexity is independent of the stress time such that lifetime studies (several years of stress time) can be simulated as fast and accurately as shorttime stress. The NBTI simulation runs equally fast as nominal Spice simulations and applies also to large analog circuits: the presently simulated circuits consist of  $\sim 300$  pFETs in the ring oscillator, additional load gates, and frequency dividers. The simulation with a model disregarding NBTI recovery overestimates the oscillator frequency reduction by a factor of two and emphasizes the significance of the presented compact models. Our future work on Spice-level NBTI models includes accounting for the metastable defect states [2], [32], [33] as well as for the NBTI  $V_{\rm ds}$  dependence.

### REFERENCES

V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," *Microelectron. Rel.*, vol. 46, no. 1, pp. 1–23, Jan. 2006. doi: 10.1016/j.microrel.2005.02.001.

- [2] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectron. Rel.*, vol. 52, no. 1, pp. 39–70, Jan. 2012. doi: 10.1016/j.microrel.2011.09. 002.

- [3] J. H. Stathis, S. Mahapatra, and T. Grasser, "Controversial issues in negative bias temperature instability," *Microelectron. Rel.*, vol. 81, pp. 244–251, Feb. 2018, doi: 10.1016/j.microrel.2017.12.035.

- [4] Failure Mechanisms and Models for Semiconductor Devices, document JEDEC JEP122G, 2010.

- [5] M. M. Kuo, K. Seki, P. M. Lee, J. Y. Choi, P. K. Ko, and C. Hu, "Simulation of MOSFET lifetime under AC hot-electron stress," *IEEE Trans. Electron Devices*, vol. 35, no. 7, pp. 1004–1011, Jul. 1988. doi: 10.1109/16.3358.

- [6] A. J. Scholten, D. Stephens, G. D. J. Smit, G. T. Sasse, and J. Bisschop, "The relation between degradation under DC and RF stress conditions," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2721–2728, Aug. 2011. doi: 10.1109/TED.2011.2153854.

- [7] A. Kerber, S. Krishnan, and E. Cartier, "Voltage ramp stress for bias temperature instability testing of metal-gate/high-k stacks," *IEEE Electron Device Lett.*, vol. 30, no. 12, pp. 1347–1349, Dec. 2009. doi: 10.1109/LED.2009.2032790.

- [8] T. Grasser et al., "Analytic modeling of the bias temperature instability using capture/emission time maps," in *IEDM Tech. Dig.*, Dec. 2011, pp. 27.4.1–27.4.4. doi: 10.1109/IEDM.2011.6131624.

- [9] G. Wirth, R. da Silva, and B. Kaczer, "Statistical model for MOSFET bias temperature instability component due to charge trapping," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2743–2751, Aug. 2011. doi: 10.1109/TED.2011.2157828.

- [10] G. Wirth, J. Franco, and B. Kaczer, "A unified model for AC bias temperature instability," in *Proc. IIRW*, Oct. 2013, pp. 84–87. doi: 10.1109/IIRW.2013.6804164.

- [11] X. Chen, Y. Wang, Y. Cao, and H. Yang, "Statistical analysis of random telegraph noise in digital circuits," in *Proc. ASP-DAC*, Jan. 2014, pp. 161–166. doi: 10.1109/ASPDAC.2014.6742883.

- [12] H. Reisinger, T. Grasser, K. Ermisch, H. Nielen, W. Gustin, and C. Schlünder, "Understanding and modeling AC NBTI," in *Proc. IRPS*, Apr. 2011, p. 6A.1.1. doi: 10.1109/IRPS.2011.5784542.

- [13] K. Giering, A. Lange, B. Kaczer, and R. Jancke, "NBTI variability of SRAM cells under periodically changing stress profiles," in *Proc. IIRW*, Oct. 2016, pp. 1–5. doi: 10.1109/IIRW.2016.7904888.

- [14] K.-U. Giering et al., "NBTI modeling in analog circuits and its application to long-term aging simulations," in *Proc. IIRW*, Oct. 2014, pp. 29–34. doi: 10.1109/IIRW.2014.7049501.

- [15] F. Alagi, M. Rossetti, R. Stella, and E. Viganó, "A reversible first-order dispersive model of parametric instability," *Microelectron. Rel.*, vol. 54, no. 3, pp. 561–569, 2014. doi: 10.1016/j.microrel.2013.10. 020

- [16] F. Alagi, M. Rossetti, R. Stella, E. Vigano, and P. Raynaud, "Compact model for parametric instability under arbitrary stress waveform," in *Proc. ESSDERC*, 2014, pp. 270–273. doi: 10.1109/ESS-DERC.2014.6948812.

- [17] K. Puschkarsky, H. Reisinger, C. Schlünder, W. Gustin, and T. Grasser, "Voltage-dependent activation energy maps for analytic lifetime modeling of NBTI without time extrapolation," *IEEE Trans. Electron Devices*, vol. 65, no. 11, pp. 4764–4771, Nov. 2018. doi: 10.1109/TED.2018.2870170.

- [18] K.-U. Giering et al., "Analog-circuit NBTI degradation and time-dependent NBTI variability: An efficient physics-based compact model," in Proc. IRPS, Apr. 2016. doi: 10.1109/IRPS.2016.7574540.

- [19] K. Puschkarsky, H. Reisinger, C. Schlünder, G. Rott, W. Gustin, and T. Grasser, "An efficient analog compact NBTI model for stress and recovery based on activation energy maps," to be published.

- [20] H. Reisinger, O. Blank, W. Heinrigs, A. Muhlhoff, W. Gustin, and C. Schlunder, "Analysis of NBTI degradation-and recovery-behavior based on ultra fast VT-measurements," in *Proc. IRPS*, Mar. 2006, pp. 448–453. doi: 10.1109/RELPHY.2006.251260.

- [21] T. Binder et al., "MINIMOS-NT user's guide," Inst. Mikroelektron., TU Wien, Vienna, Austria, Tech. Rep., 1998.

- [22] [Online]. Available: http://www.globaltcad.com

- [23] B. Kaczer et al., "Ubiquitous relaxation in NBTI stressing—New evaluation and insights," in Proc. IRPS, Apr. 2008, pp. 20–27. doi: 10.1109/RELPHY.2008.4558858.

- [24] G. Rzepa et al., "Comphy—A compact-physics framework for unified modeling of NBTI," Microelectron. Rel., vol. 85, pp. 49–65, Jun. 2018. doi: 10.1016/j.microrel.2018.04.002.

- [25] W. Goes et al., "Identification of oxide defects in semiconductor devices: A systematic approach linking DFT to rate equations and experimental evidence," *Microelectron. Rel.*, vol. 87, pp. 286–320, Aug. 2018. doi: 10.1016/j.microrel.2017.12.021.

- [26] E. Takeda and N. Suzuki, "An empirical model for device degradation due to hot-carrier injection," *IEEE Electron Device Lett.*, vol. 4, no. 4, pp. 111–113, Apr. 1983. doi: 10.1109/EDL.1983.25667.

- [27] G. A. Rott, H. Nielen, H. Reisinger, W. Gustin, S. Tyaginov, and T. Grasser, "Drift compensating effect during hot-carrier degradation of 130 nm technology dual gate oxide P-channel transistors," in *Proc.* IRPS, Oct. 2013, pp. 73–77. doi: 10.1109/IIRW.2013.6804162.

- [28] B. Ullmann et al., "Impact of mixed negative bias temperature instability and hot carrier stress on MOSFET characteristics—Part I: Experimental," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 232–240, Jan. 2019. doi: 10.1109/TED.2018.2873419.

- [29] B. Kaczer et al., "Origin of NBTI variability in deeply scaled pFETs," in Proc. IRPS, May 2010, pp. 26–32. doi: 10.1109/IRPS.2010. 5488856.

- [30] B. Kaczer, P. Roussel, T. Grasser, and G. Groeseneken, "Statistics of multiple trapped charges in the gate oxide of deeply scaled MOS-FET devices—Application to NBTI," *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 411–413, May 2010. doi: 10.1109/LED.2010. 2044014

- [31] D. Angot et al., "NBTI variability fundamental understandings and impact on digital logic by the use of extensive dataset," in *IEDM Tech. Dig.*, Dec. 2013, pp. 15.4.1–15.4.4. doi: 10.1109/IEDM.2013.6724636.

- [32] L. Heiß et al., "New methodology for on-chip RF reliability assessment," in Proc. IRPS, Apr. 2016, pp. 4C-4-4C-5C-5-7. doi: 10.1109/IRPS.2016.7574541.

- [33] X. Yu et al., "A fast V<sub>th</sub> measurement (FVM) technique for NBTI behavior characterization," *IEEE Electron Device Lett.*, vol. 39, no. 2, pp. 172–175, Feb. 2018. doi: 10.1109/LED.2017.2781243.