Ein nicht zu vernachlässigender Beitrag zum Gesamtwiderstand einer

Verbindungsleitung wird durch die Durchkontaktierungen (Vias) zwischen

den Metallisierungsebenen verursacht.

In diesem Beispiel wird deshalb der Widerstand von mehreren Vias

unterschiedlichen Querschnitts in

Kupfer-Dual-Damascene Architektur berechnet und gezeigt, wie er von der

Dicke der Barriereschicht abhängt.

Für Messungen von Via-Widerständen verwendet man

zwecks Verringerung des Messfehlers

üblicherweise eine Kette einiger hundert hintereinandergereihter Vias.

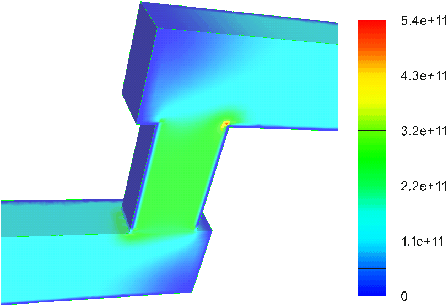

Abbildung 7.12 zeigt einen Teil einer solchen Kette

von Durchkontaktierungen mit einem Querschnitt von

![]()

![]() m.

m.

Das für die Simulationen dieser Struktur erzeugte Gitter hat 441945 Tetraederelemente mit quadratischem Ansatz und 604668 Knoten (Gesamtbereich für die elektro-thermische Simulation).

Die erwartet starke Abhängigkeit des Via-Widerstandes von der Dicke der schlecht leitenden Barriereschicht wurde durch die Simulation bestätigt. Die Ergebnisse sind in Abb. 7.14 dargestellt. Je kleiner der Querschnitt der Durchkontaktierung ist, desto stärker ist auch der Einfluss der Barriereschicht auf den Widerstand.

|

Ein Vergleich mit Messdaten [26] zeigt für den Fall einer [20]nm starken Barriereschicht einen um 30% höheren Widerstand als berechnet. Dieser erhöhte Messwert lässt vermuten, dass die Übergänge von Cu auf TiN einen zusätzlichen Widerstand bewirken. Bei Vias ohne einer TiN Barriere liegen die gemessenen und simulierten Werte nur wenige Prozent auseinander.

Abschließend wurde noch eine gekoppelt elektro-thermische Simulation

der Struktur mit [20]nm TiN-Barriere durchgeführt.

Dabei wurde ein Strom von [13.4]mA an den beiden Enden der Leitung

angelegt,

das bedeutet eine Stromdichte von etwa [8.5]MA/cm![]() im Zentrum des Vias.

Die Unterseite des Si-Substrates wurde dabei konstant auf

im Zentrum des Vias.

Die Unterseite des Si-Substrates wurde dabei konstant auf ![]() C

gehalten.

C

gehalten.

Abbildung 7.15 zeigt die Stromdichte auf der Oberfläche der simulierten Struktur. Der hohe Widerstand der TiN-Barriere bewirkt eine fast gleichmäßige Verteilung der Stromdichte am Übergang zwischen unterem Leiter und Via. Die höchste Stromdichte kann man an der rechten Ecke im oberen Bereich des Vias erkennen. Dieser Bereich ist deshalb am meisten elektromigrationsgefährdet, da hier gleichzeitig auch erhöhte Temperatur auftritt. Allerdings wird die Stromdichte an dieser Stelle durch die Simulation etwas überschätzt, da bei üblichen Herstellungprozessen anstatt der hier angenommenen scharfen Kante eine Abrundung entsteht.

|

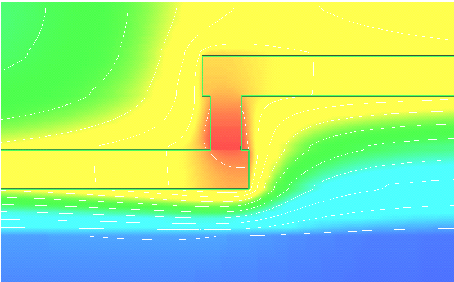

Die Temperaturverteilung am Querschnitt durch die Via-Struktur ist in

Abb. 7.16 dargestellt.

Das Temperaturmaximum von ![]() C wird auf der Unterseite des Vias

erreicht; dort hat auch die Verlustleistung aufgrund des hohen

Widerstandes der TiN-Schicht ein Maximum.

C wird auf der Unterseite des Vias

erreicht; dort hat auch die Verlustleistung aufgrund des hohen

Widerstandes der TiN-Schicht ein Maximum.

|