|

|

||||

BiographyPatrick Reisinger was born in Hollabrunn, Austria, in 1996. He studied at the TU Wien, receiving his BSc degree in Technical Physics in 2020 and Diplomingenieur in Physical Energy and Measurement Engineering in 2023. After completing his studies, he worked in the automotive industry for a year before moving to the IuE as a PhD student in August 2024 where he is investigating non-volatile memory technologies within in the Christian Doppler Laboratory for Single-Defect Spectroscopy. |

|||||

Defect and Noise Analysis in SiN-Based Memory Devices with a High-Precision DPI

To further enhance our capabilities in advanced device characterization, we have focused on improving and optimizing our custom-built Defect Probing Instrument (DPI). These efforts specifically target reduced noise and optimized bandwidth for high-precision voltage and current measurements. The resulting enhancements significantly improve the accuracy and temporal resolution of IDVG and transient measurements, critical for evaluating device reliability and charge trapping phenomena. Key improvements include refined shielding and grounding strategies, low-noise amplification, and advanced digital filtering, all contributing to a significantly improved signal-to-noise ratio.

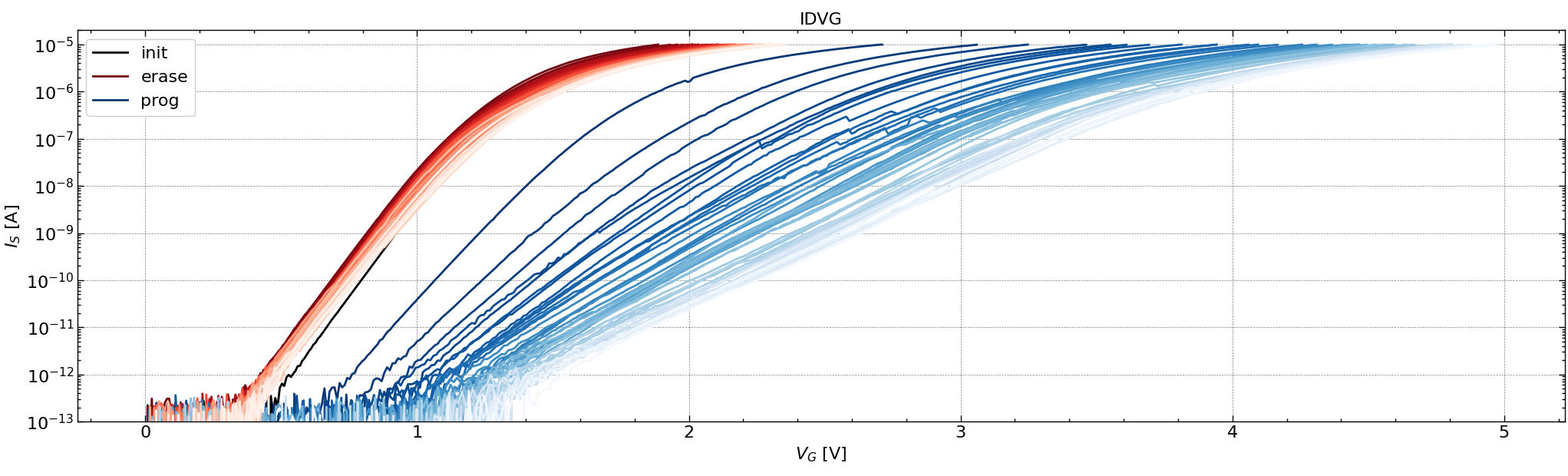

The DPI was recently employed to characterize a charge-trapping memory device, where memory states are encoded via threshold voltage shifts caused by charge trapping in silicon nitride (SiN). By monitoring ΔVg across multiple program/erase cycles, we captured clear evidence of device degradation. This degradation is reflected in the evolving IDVG characteristics, which show progressive shifts with repeated cycling (Fig. 1).

Additionally, the DPI supports frequency-domain analysis via noise spectroscopy. By measuring the power spectral density (PSD) of the current signal, we observed notable changes in the noise spectrum post-cycling and between states, including increases in 1/f noise and distinct features linked to trap dynamics. These results confirm the generation of cycling-induced defects and provide deeper insight into the physical mechanisms limiting memory endurance.

Fig. 1: Evolution of the IDVG characteristics over multiple program/erase cycles, showing progressive device degradation due to charge trapping.