# Two-Dimensional Transient Simulation of Charge-Coupled Devices Using MINIMOS NT

M. Rottinger, T. Simlinger, and S. Selberherr

Institute for Microelectronics, TU Vienna Gusshausstrasse 27–29, A-1040 Vienna, Austria

#### Abstract

This paper will provide information on the features of the new device simulator MINIMOS NT and demonstrate its efficiency in transient simulation of complex device structures. An example will indicate the feasibility of such simulations even on a workstation.

#### 1. Introduction

Charge-Coupled Devices (CCDs) have a broad field of application in optical imaging and analog signal processing. Since their invention in 1970 the performance of CCDs, such as noise reduction, photo-sensitivity, resolution and power consumption, has been improved continuously [1]. In contrast to this development simulation of CCDs, particular transient simulation, has not been practicable because of the high requirements on computational resources, hence only single CCD cells have been simulated [2] [3].

Using our simulator, MINIMOS NT, it is possible to simulate complex device structures with reasonable demands on computational resources. For instance, CCDs containing up to 60 gates have been simulated in two space dimensions on a workstation equipped with 128MB of main memory.

## 2. Description of the simulator

MINIMOS NT's software architecture is based upon up-to-date software engineering knowledge. The demands of numerous users of device simulation software were carefully evaluated over time in order to found the required features. For instance, discretization, Jacobian matrix assembly and linear system solution are linked with abstract protocolls. Thereby it is possible to account for fully different physical models in different, however, connected segments, e.g., in one segment a hydro-dynamic model can be used whereas in a neighbouring segment only a drift-diffusion model is considered. The same holds true for the various physical parameter models. Mixed numerical discretization schemes are also possible. This concept holds for two and three space dimensions. For transient integration a predictor-corrector method was evaluated to be most suitable for the semiconductor problem. Circuits containing different numerically treated semiconductor devices and the usual discrete components are also handled properly.

The Jacobian matrix is scaled fully automatically with an iterative algorithm [4]. The linear system is solved with a state-of-the-art BiCGStab algorithm where automatic switching to a Gauß-solver is performed if convergence of the iterative algorithm seems not attainable.

## 3. Time step estimation

The predictor used to estimate the size of the next time step is based upon a quadratic extrapolation of the potential-update norm. The ratio of the estimated step size and the previous step size is restricted to a maximum, the sectio aurea constant (1.618...), to limit the step size variations. With this restriction a quasi-uniform mesh is achieved, which gives a second order local function error. After calculation of each time step the potential update is checked. For this purpose the L2 norm and the infinity norm are calculated. If at least one of these norms exceeds a respective threshold, the step size is reduced by quadratic interpolation and the calculation is repeated.

In order to accurately follow the predefined contact signals it is necessary to calculate a time step at the instances used to specify the contact signals. This requires a reduction of the estimated step size to exactly match the instance and causes an increase in the total number of required time steps. Therefore the number of specified instances should be as small as possible to take full advantage of the quadratic time step estimation. To reduce the number of specified instances necessary for a sufficient representation of nonlinear contact signals a quadratic interpolation is used.

## 4. Transient simulation of a CCD

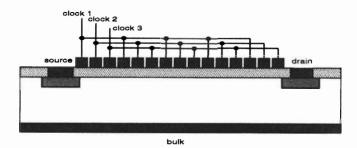

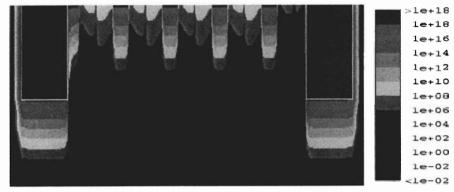

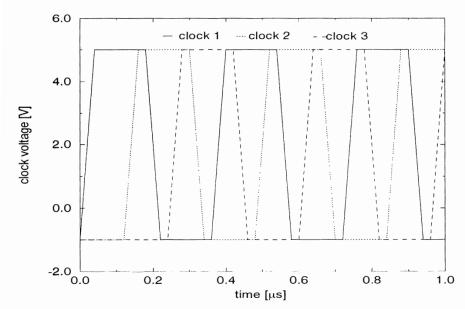

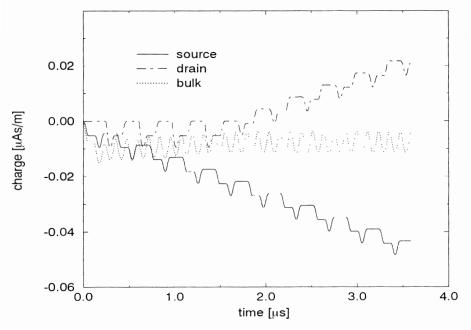

As an example a three-phase clock, n-channel CCD composed of fifteen gates – results of devices with more gates can hardly be visualized on paper – has been simulated in two space dimensions. Fig. 1 shows the structure of the device. The source and drain contacts were held constant at 0V, the bulk contact at -1V. The voltages applied to the gates varied between -1V and +5V (Fig. 3). The simulation over ten clock periods required 360 time steps. The adapted space grid consisted of approximately 10,000 points. A snapshot of the electron concentration in the channel region is shown in Fig. 3. One can nicely see the alternation of accumulation to strong inversion under the gates. As a further result of the simulation Fig. 4 shows the charge that has passed through the source, drain and bulk contact, respectively. Charge flowing into the device is counted positive.

### 5. Conclusion

The simulator is fully integrated into the VISTA framework. Therefore all features of the framework, e.g., coupling to the various process simulators, visualizers and animators, embedded optimizers, are readily available. The above example, which has been calculated on a DEC 3000/400, illustrates the ability of MINIMOS NT to perform transient simulations of complex device structures and demonstrates the feasibility of such simulations even on a workstation.

Figure 1: The structure of a 15-gate CCD.

Figure 2: Electron concentration  $[cm^{-3}]$  in the channel region at  $t = 3.36 \mu s$ .

#### Acknowledgement

This work is supported by Digital Equipment Corporation, Hudson, USA; Motorola, Austin, USA; Philips, Eindhoven, The Netherlands.

## References

- [1] R. Melen and D. Buss (eds.), Charge-Coupled Devices: Technology and Applications, IEEE Press, 1976.

- [2] N. Ula, G. A. Cooper, J. C. Davidson, S. P. Swierkowski and Ch. E. Hunt, "Optimization of Thin-Film Resistive-Gate and Capacitive-Gate GaAs Charge-Coupled Devices", IEEE Trans. Electron Devices, vol. 39(5), pp. 1032–1040, 1992.

- [3] Ch. R. Smith and S. G. Chamberlain, "Theory and Design Methodology for an Optimum Single-Phase CCD", *IEEE Trans. Electron Devices*, vol. 39(4), pp. 864–873, 1992.

- [4] C. Fischer and S. Selberherr, "Optimum Scaling of Non-Symmetric Jacobian Matrices for Threshold Pivoting Preconditioners", Proc. Int. Workshop on Numerical Modeling of Processes and Devices for Integrated Circuits, NUPAD V, pp. 123–126, 1994.

- [5] S. Halama et al., "The Viennese Integrated System for Technology CAD Applications", Technology CAD Systems, pp. 197-236, 1993.

Figure 3: Clock voltages during  $1\mu s$ .

Figure 4: Charge transferred through the contacts of a 15-gate CCD during 10 clock periods.