# **High Performance Computing Symposium**

(HPC 2015)

2015 Spring Simulation Multi-Conference (SpringSim'15)

**Simulation Series Volume 47 Number 4**

Alexandria, Virginia, USA 12 – 15 April 2015

# **Editors:**

Layne T. Watson Joseph Weinbub Masha Sosonkina William I. Thacker Karl Rupp

ISBN: 978-1-5108-0101-1

#### Printed from e-media with permission by:

Curran Associates, Inc. 57 Morehouse Lane Red Hook, NY 12571 www.proceedings.com

Some format issues inherent in the e-media version may also appear in this print version.

#### © 2015 SIMULATION COUNCILS, INC.

Responsibility for the accuracy of all statement in each paper rests solely with the author(s). Statements are not necessarily representative of, nor endorsed by, The Society for Modeling and Simulation International.

Printed by Curran Associates, Inc. (2015)

Permission is granted to photocopy portions of this publication for personal use and for the use of students provided credit is given to the conference and publication. Permission does not extend to other types of reproduction nor to copying for incorporation into commercial advertising nor for any other profit-making purpose. Other publications are encouraged to include 300- to 500-word abstracts or excerpts from any paper contained in this book, provided credits are given to the author and the conference. For permission to publish a complete paper write: The Society for Modeling and Simulation International (SCS), 2598 Fortune Way, Suite I, Vista, CA 92081, USA.

#### Additional copies of the Proceedings are available from:

Curran Associates, Inc. 57 Morehouse Lane Red Hook, NY 12571 curran@proceedings.com www.proceedings.com/0128.html

or

The Society for Modeling and Simulation International 2598 Fortune Way, Ste I Vista, CA 92081 USA www.scs.org

ISBN: 978-1-5108-0101-1 PRINTED IN THE UNITED STATES

# TABLE OF CONTENTS

| Towards a More Fault Resilient Multigrid Solver  J. Calhoun, L. Olson, M. Snir, W. Gropp                                                                                           | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Exploiting Computing Power of Xeon and Intel Xeon Phi for a Molecular Dynamics Application                                                                                         | 9   |

| Fast Parallel Conversion of Edge List to Adjacency List for Large-Scale Graphs  S. Arifuzzaman, M. Khan                                                                            | 17  |

| A Research Framework for Exascale Simulations of Distributed Virtual World Environments on                                                                                         |     |

| High Performance Computing (HPC) Clusters                                                                                                                                          | 25  |

| Fast Sparse Matrix Multiplication on GPU                                                                                                                                           | 33  |

| ExaShark: A Scalable Hybrid Array Kit for Exascale Simulation  I. Chakroun, T. Haber, T. Vander, R. Wuyts, B. Fraine, W. Demeuter                                                  | 41  |

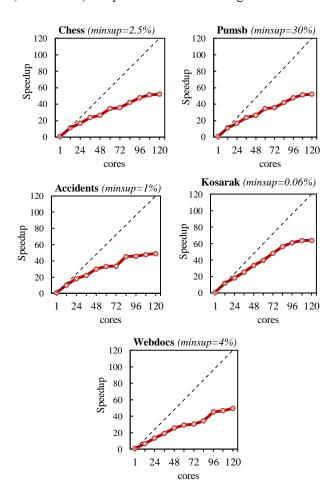

| A Load Balancing Parallel Method for Frequent Pattern Mining on Multi-core Cluster                                                                                                 | 49  |

| Efficient Scaling of a Hydrodynamics Simulation Using Compiler-based Accelerator Technology                                                                                        | 59  |

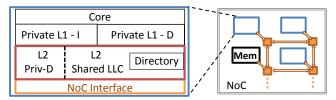

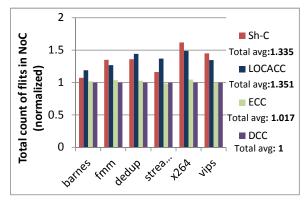

| Sharer Status-based Caching in Tiled Multiprocessor Systems-on-Chip  P. Damodaran, A. Zaib, S. Wallentowitz, T. Wild, A. Herkersdorf                                               | 67  |

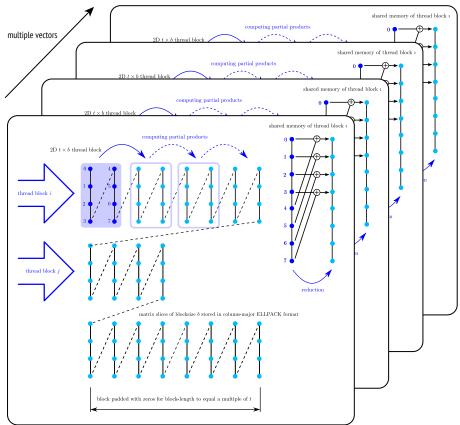

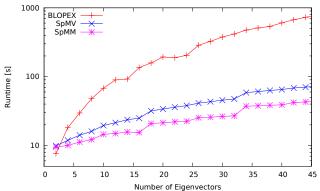

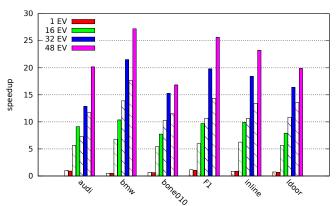

| Accelerating the LOBPCG method on GPUs using a Blocked Sparse Matrix Vector Product                                                                                                | 75  |

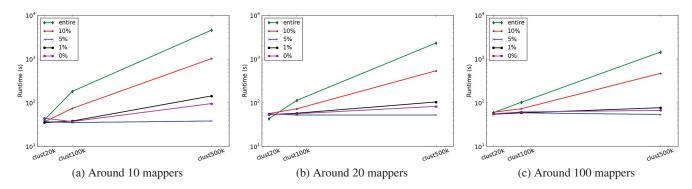

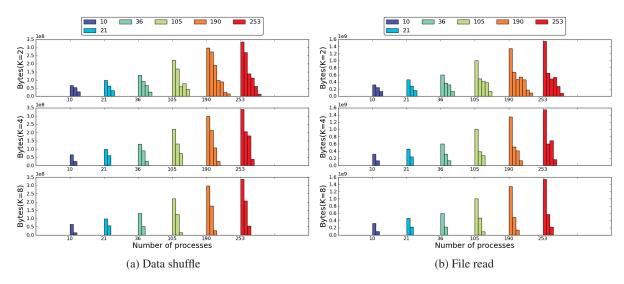

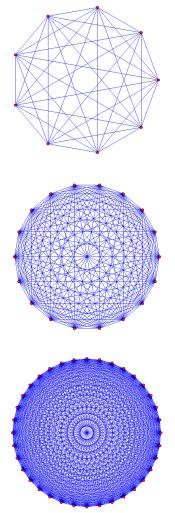

| Incremental, Distributed Single-Linkage Hierarchical Clustering Algorithm Using MapReduce                                                                                          | 83  |

| Throughput Studies on an InfiniBand Interconnect via All-to-All Communications  N. Mistry, J. Yanchuck, J. Ramsey, X. Huang, B. Wiley, M. Gobbert                                  | 93  |

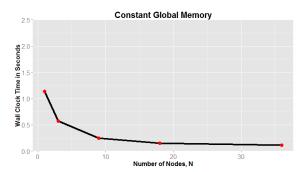

| Parallel Performance of Higher-Order Methods on GPU Hardware  T. Spilhaus, J. Buckley, G. Khanna                                                                                   | 100 |

| DOEE: Dynamic Optimization Framework for Better Energy Efficiency                                                                                                                  | 107 |

| Predicting Energy Consumption Relevant Indicators of Strong Scaling HPC Applications for Different Compute Resource Configurations                                                 | 115 |

| H. Shoukourian, T. Wilde, A. Auweter, A. Bode, D. Tafani  A Virtual Machine Model for Accelerating Relational Database Joins Using a General Purpose GPU  K. Angstadt, E. Harcourt | 127 |

| Performance Analysis and Design of a Hessenberg Reduction using Stabilized Blocked Elementary Transformations for New Architectures                                                | 135 |

| K. Kabir, A. Haidar, J. Dongarra, S. Tomov                                                                                                                                         |     |

| Efficient Algorithms for Improving the Performance of Read Operations in Distributed File System                                                                                   | 143 |

| Long-time Simulation of Calcium Induced Calcium Release in a Heart Cell using the Finite Element  Method on a Hybrid CPU/GPU Node                                                  | 150 |

| X. Huang, M. Gobbert  High Performance Kirchhoff Pre-Stack Depth Migration on Hadoop                                                                                               | 158 |

| Parallel QR Algorithm For The C-Method: Application To The Diffraction By Gratings And Rough                                                                                       |     |

| Surfaces                                                                                                                                                                           | 166 |

| A Study Of Manycore Shared Memory Architecture As A Way To Build SOC Applications                                                                                                  | 174 |

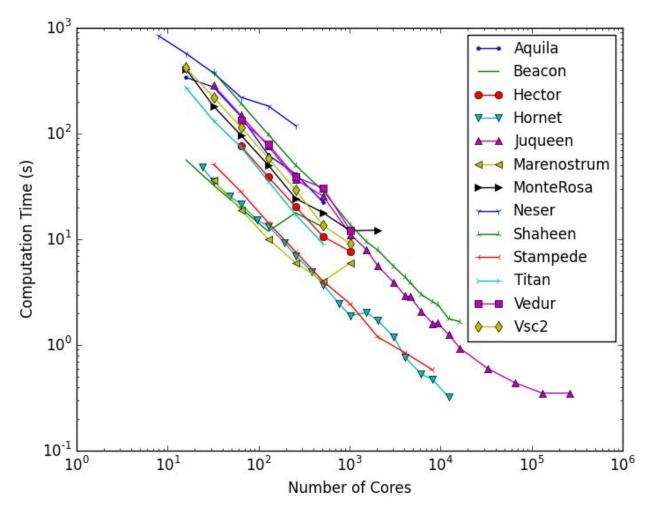

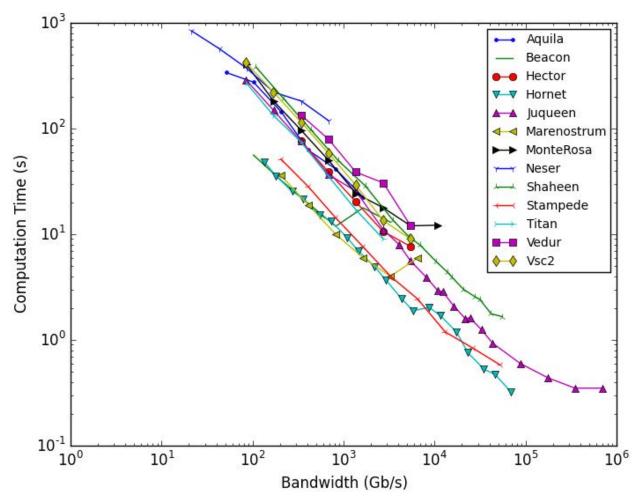

| Solving The Klein-Gordon Equation Using Fourier Spectral Methods: A Benchmark Test For                                                                                             |     |

| Computer Performance                                                                                                                                                               | 182 |

| S. Aseeri, B. Leu, B. Muite, M. Quell, R. Speck, O. Batrasev, A. Liu, E. Muller, H. Servat, M. Moer, M. Icardi, N. Li, B. Palen, P. Sheth, J. Vienne                               |     |

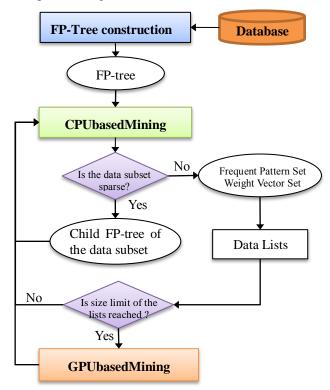

| A Self-Adaptive Method for Frequent Pattern Mining using a CPU-GPU Hybrid Model                                                                                                    | 192 |

| L. Vu, G. Alaghband  Computational Steering for High Performance Computing Applications on Blue Gene/Q System  B. Danani, B. D'Amora                                               | 202 |

| Strategies to Hide Communication for a Classical Molecular Dynamics Proxy Application  | 210 |

|----------------------------------------------------------------------------------------|-----|

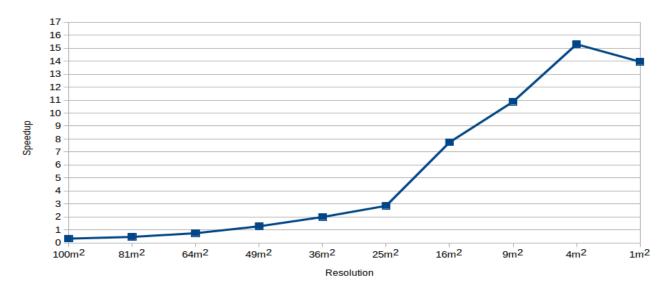

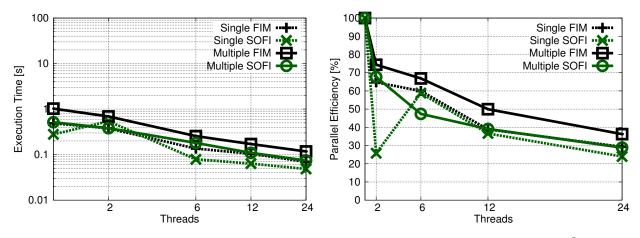

| Shared-Memory Parallelization of the Semi-Ordered Fast Iterative Method                | 217 |

| J. Weinbub, F. Dang, S. Selberherr, T. Gillberg                                        |     |

| PerDome: A Performance Model for Heterogeneous Computing Systems                       | 225 |

| L. Tang, X. Hu, R. Barrett                                                             |     |

| An Improved Probability-One Homotopy Map for Tracking Constrained Clustering Solutions | 233 |

| D. Easterling, L. Watson, N. Ramakrishnan                                              |     |

| Productive Parallel Programming with CHARM++                                           | 241 |

| P. Miller                                                                              |     |

| Author Index                                                                           |     |

#### **Welcome from the General Chair**

Dear Colleagues and friends,

On behalf of the Organizing Committee, I am delighted and honored to welcome you to the Spring Simulation Multi-Conference 2015 (SpringSim'15) in Alexandria, Virginia.

The Society for Modeling & Simulation International (SCS) which organizes Springsim is one of the oldest Modeling and Simulation organizations in the world. It endeavors to promote the advancement of Modeling and Simulation and connect Modeling and Simulation professionals worldwide. The SpringSim'15 program includes a world-class selection of peer-reviewed paper, presentations, distinguished keynote speeches and tutorials. In addition, SpingSim'15 offers 1) a poster track for students to showcase their work and receive feedback 2) a Ph.D. colloquium where students and established professionals can meet and exchange ideas and 3) for the first time a student mobile application competition where they can show how Modeling and Simulation can be meshed with new technologies. Great thanks to the organizations that have donated money, licenses and books to recognize the best submissions at this conference.

I would also like to thank our keynote speakers **Prof. Wesley Wildman, Prof. Sally Brailsford** and **Mr. Jesse Citizen** for graciously accepting to share their vast knowledge and experiences with us. My thanks also go to all members of the Organization Committee for their tireless efforts especially in working through the introduction of a new format and editing process. It was truly a team effort. The committee consists of:

Vice-General Chair Navonil Mustafee, Exeter University

Program Chair Saurabh Mittal, Dunip Technologies, LLC

Proceedings Chair Shafagh Jafer, Embry-Riddle Aeronautical University

Awards Chair Umut Durak, DLR

Tutorial Chair Jose Padilla, VMASC

Publicity Chair Gregory Zacharewicz, Université Bordeaux I

Sponsorship Chair Andreas Tolk, Simis, Inc.

As a Multi-Conference, our success depends heavily on the track organizers, reviewers and committee members. I am very grateful for the efforts of all of the volunteers that dedicated their time and effort to review and edit all of the submissions and thus make this gathering possible. I also express my gratitude to authors and tutorial presenters for their important contributions.

My sincere appreciation goes to the symposia chairs, whose invaluable efforts in their respective sections were key to the success of the overall multi-Conference. This year's symposia chairs are:

- Agent-Directed Simulation (ADS) Symposium, chaired by Levent Yilmaz and Tuncer Ören,

- Communications and Networking Symposium (CNS), chaired by Abolreza Abhari and Hala ElAarag

- High Performance Computing Symposium (HPC), chaired by Layne Watson and Josef Weinbub

- Symposium on Simulation for Architecture and Urban Design (SimAUD), chaired by Shajay Bhooshan and Holly Samuelson

- Theory of Modeling and Simulation (TMS/DEVS), chaired by Fernando Barros and Moon Ho Hwang

- Annual Simulation Symposium (ANSS), chaired by Andreas Tolk and Shafagh Jafer

- Modeling and Simulation in Medicine (MSM) chaired by Jerzy Rozenblit and Johannes Sametinger

- Tutorial and Vendor Track, chaired by Jose Padilla

- Posters session & Student Colloquium, chaired by Salim Chemlal and Mohamed Moallemi

- Work in Progress session chaired by Gregory Zacharewicz

Special thanks go to the SCS officers, **Oletha Darensburg**, **Aleah Hockridge** and the team for their high level of professionalism, and for the smooth running of all the events.

**Alexandria** is one of the oldest cities in the United States and has an historic *Old Town* with great dining and shopping. In addition, please feel free to sign up for our organized night tour to see the various monuments and cultural centers in Washington, D.C.

Welcome to Springsim'15

Saikou Diallo, Ph.D.

General Chair SpringSim 2015

Old Dominion University, Virginia, Modeling Analysis and Simulation Center

## HPC' 15 CHAIRS' MESSAGE

Welcome to the 2015 High Performance Computing Symposium! This is the 23rd special symposium devoted to the impact of high performance computing and communications on computer simulations. The symposium, part of the 2015 Spring Simulation Multi-conference, encompasses a wide variety of topics with a focus on tools and applications for the simulation of physical and engineering systems.

Advances in networking, high end computers, large data stores, special purpose hardware, parallel programming languages, and middleware capabilities are ushering in a new era of high performance parallel and distributed simulations. Along with these new capabilities come new challenges in computing and system modeling. The goal of HPC 2015 is to encourage innovation in high performance computing and communication technologies and to promote synergistic advances in modeling methodologies and simulation. It will promote the exchange of ideas and information between universities, industry, and national laboratories about new developments in system modeling, high performance computing and communication, and scientific computing and simulation. Topics of interest include large scale simulations, numerical methods, problem solving environments, visualization and data management, parallel algorithms for emerging architectures, software tools, and power-aware computing.

The 23rd High Performance Computing Symposium features 27 high quality full papers covering a very wide range of topics, as is evident from a glance at the index of papers, and a tutorial on the parallel programming system Charm++. HPC 2015 would have been impossible without the contributions from many individuals---the symposium organizers who planned and organized everything, the Steering Committee who provided valuable advice and support, and the Program Committee who rigorously reviewed the submissions and their revisions. We have been involved with this symposium since 2000, and this is the best collection of papers we have ever had, thanks to the hard work of the chairs and all the committee members, and the participation of the HPC community. The conference organizers, Steering Committee, and Program Committee hope that everyone enjoys this year's outstanding program, and the Alexandria venue.

Layne T. Watson, General ChairJosef Weinbub, Vice-general Chair Masha Sosonkina, Program Chair William I. Thacker, Vice-program Chair Karl Rupp, Publicity Chair

## SYMPOSIUM ORGANIZERS

#### **General Chair**

Layne T. Watson, Virginia Polytechnic Institute & State University

#### **General Vice-Chair**

Joseph Weinbub, Vienna University of Technology

## **Program Chair**

Masha Sosonkina, Ames Laboratory & Old Dominion University

## **Program Vice-Chair**

Will Thacker, Winthrop University

# **Steering Committee**

Marc Baboulin, Inria Saclay---Ile-de-France and Universite Paris-Sud Gary Howell, North Carolina State University Fang 'Cherry' Liu, Georgia Institute of Technology Niraj Srivastava, Raytheon Corporation

# **Program Committee**

Alex Aravind, University of Northern British Columbia Eric Aubanel, University of New Brunswick, Canada Sanjutka Bhowmick, University of Nebraska Brett Bode, Ames Laboratory

Ali Butt, Virginia Polytechnic Institute

Bruno Carpentieri, CERFACS, France

Haiyan Cheng, Willamette University

Jing-Ru C. "Ruth" Cheng, U.S. Army Research and Development Center

Jose C. Cunha, Universidade Nova de Lisboa

Matt Dixon, University of San Francisco

Nahid Emad, Universite' de Versailles Saint-Quentin-en-Yvelines, France

Samantha Foley, Oak Ridge National Laboratory Apala Guha, University of Chicago Azzam Haidar, ICL, University of Tennessee Phil Hammonds, RTSync Corporation Gary Howell, North Carolina State University Qi Hu, Facebook Joshua Hursey, Oak Ridge National Laboratory Jim Jones, Florida Tech

Piotr Luszczek, University of Tennessee, Knoxville

Asif Mahmood, University of Bridgeport

Michael Mascagni, Florida State University

Gabriel Mateescu, Leibniz-Rechenzentrum, Germany

Phil Moore, University of South Carolina

Thomas Rauber, University of Bayreuth, Germany

Jill Reese, Appalachian State University

Cal Ribbens, Virginia Polytechnic Institute

Gudula Ruenger, Technical University of Chemnitz, Germany

Fan Rui, Nanyang Technological University, Singapore

Yang Song, IBM Almaden Research Center

Steve Stevenson, Clemson University

Alan Stewart, Queen's University, Belfast, UK

Peter Tang, Intel Corporation

William A. Ward, CSC, NASA Greenbelt

Qin Xin, Universite' Catholique de Louvain, Belgium

Ping Yang, Pacific Northwest National Lab

Dongping Zhang, AMD Corporation

Yaxiong Zhao, Google

# Towards a More Fault Resilient Multigrid Solver

Jon Calhoun jccalho2@illinois.edu

Luke Olson lukeo@illinois.edu

Marc Snir snir@illinois.edu

William D. Gropp wgropp@illinois.edu

Department of Computer Science University of Illinois at Urbana-Champaign Urbana, Illinois 61801

#### **ABSTRACT**

The effectiveness of sparse, linear solvers is typically studied in terms of their convergence properties and computational complexity, while their ability to handle transient hardware errors, such as bit-flips that lead to silent data corruption (SDC), has received less attention. As supercomputers continue to add more cores to increase performance, they are also becoming more susceptible to SDC. Consequently, understanding the impact of SDC on algorithms and common applications is an important component of solver analysis. In this paper, we investigate algebraic multigrid (AMG) in an environment exposed to corruptions through bit-flips. We propose an algorithmic based detection and recovery scheme that maintains the numerical properties of AMG, while maintaining high convergence rates in this environment. We also introduce a performance model and numerical results in support of the methodology.

#### **Author Keywords**

Algebraic Multigrid, Silent Data Corruption, Fault Tolerance, Resilience

#### INTRODUCTION

Many scientific applications, from modeling blood flow to electromagnetics, depend on sparse matrix structures and linear algebra computations. These types of computations often consume a sizable percent of a high performance computing (HPC) workload. In particular, one crucial operation is the sparse, linear solve. Scalability and convergence of such methods are well studied, but their behavior in the presence of hardware faults is less developed. Current and emerging HPC architectures are expected to experience higher levels of faults than previous architectures and understanding the impact of fault(s) on the *algorithm* is an important component in fully utilizing their resources. Consequently, resiliency techniques need to be developed and analyzed to allow linear solvers the ability to remain efficient and scalable on emerging HPC architectures.

Modern scientific computing relies on solving large, sparse systems of linear equations. Sophisticated solvers are employed to take advantage of this sparsity, and as computing capabilities continue to progress so do the demands on the linear solver. One solver that has shown to be flexible across a range of different architectures is algebraic multigrid (AMG), due to its potential scalability, robustness, and efficiency as an  $\mathcal{O}(n)$  complexity method.

As machines are built using a higher number of cores the individual cores themselves are not becoming more reliable [3]. Therefore, as the number of cores in a system increases, the mean time between interruptions decreases. As a result, fault tolerance and resilience are receiving increased attention. Most of this attention is devoted to developing traditional checkpoint-restart libraries [13, 16]. Checkpointrestart is designed to correct fail-stop errors that do not allow the application to proceed once the error manifests. A main disadvantage of a typical checkpoint-restart scheme is the increase in time and energy to complete a run. Advanced approaches attempt to address these issues, but techniques at the algorithm level offer an opportunity to further enhance resilience. Some approaches use mathematical theory and numerical methods in-order to re-construct the missing data due to a fail-stop error [7, 1].

The increase in the number of circuits, coupled with the decrease in feature size, and the the use of low power techniques are also likely to increase the frequency of silent data corruption (SDC) and poses a major problem to the future of large scale scientific computing [5, 20]. General methods for SDC detection leverage redundancy [12], but algorithm based fault tolerance (ABFT) has the potential to reduce the overhead for handling SDC by leveraging algorithm dependent heuristics or invariants to detect and recover from SDC [8, 10]. Furthermore, the use of ABFT increases the resiliency of the application while at the same time lowering the time to solution in faulty environments.

The focus of this paper is on utilizing ABFT to improve resiliency of AMG. Understanding the level of resiliency that is provided by AMG on emerging architectures is important for AMG and other sparse, linear solvers.

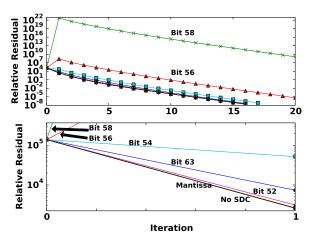

To motivate the need for silent data corruption (SDC) detection and recovery in the sparse, linear solve, in Figure 1 we consider the residual history for the solution of a diffusion problem in 2D (cf. Section 5). In this example, a single fault is injected into the residual calculation before restriction during the second iteration on the finest level. This fault is a single bit-flip in the first element of the residual vector, a IEEE 754 double precision floating point number, on process 0 of a 16 process job. The fault does not lead to a segmentation fault or *segfault*, and is thus potently silent, but influential in its impact on the algorithm. Depending on *which* bit is flipped, the number of extra iterations required to achieve the convergence tolerance of  $1e^{-7}$  ranges from 0 (bits in the mantissa) to double the original amount (bits in the exponent), thus motivating the need for SDC detection and recovery.

Figure 1. A single bit-flip in a IEEE 754 double precision floating point element in the residual vector's effect on the iterations needed to converge. In this location, a flipped bit in the exponent causes an increase in the iterations till convergence; while a flipped bit in the mantissa or the sign bit, bit 63, has no effect.

To this end, we improve and analyze the resilience of AMG in the presence of silent faults. In particular, in this paper we make the following contributions:

- low overhead algorithmic based recovery for AMG;

- low cost SDC detectors for iterative linear solvers; and

- AMG specific SDC detectors.

#### **BACKGROUND**

#### **Algebraic Multigrid**

Consider the sparse matrix problem  $A\mathbf{x} = \mathbf{b}$ . In a parallel setting, iterative solution techniques are preferred due to the memory and complexity requirements to solve. One such approach is algebraic multigrid (AMG) [18], which is often used as a preconditioner for a Krylov method such as conjugate gradient (CG) or generalized minimum residual (GM-RES).

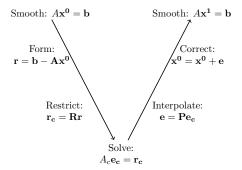

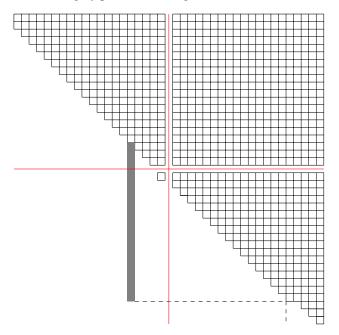

AMG constructs a hierarchy of successively coarser problems that are used to iteratively refine the error in the solution. Figure 2 outlines a *solve* cycle of AMG, where an initial guess  $x^0$  is refined using two compatible operations: relaxation, such as weighted Jacobi, and coarse-grid correction, which is a subspace projection method. Relaxation is responsible for reducing high energy error, while coarse grid correction targets *algebraically* smooth error, or error that is invariant to relaxation. The cycle proceeds by successively coarsening the error equations, Ae = r, until a coarse level problem is effectively solved in a few steps of relaxation or is efficiently processed with a direct method. Errors on coarse levels are then interpolated to correct solutions. Figure 2 represents the well-known V-cycle and is a common approach to traverse the AMG hierarchy in parallel.

#### Resilience

Resilience has been a challenge since the early days of computing. Vacuum tube based machines had a mean-time-between-failure (MTBF) of a few days. With the introduction

Figure 2. AMG V-cycle process used to solve Ax = b

of transistors and integrated circuits, the reliability of the underlying hardware increased, but width the small feature sizes and low-power environments in emerging architectures, fault awareness is making a resurgence [3].

All hardware components do not exhibit the same level of reliability. DRAM and SRAM are susceptible to bit-flips, which has led to error correction codes (ECC) and so-called *chipkill* that protect against bit-flips in memory [21]. These methods, at the cost of area and power on chip, seek to recover the data by stored parity information. In the case of chipkill, a multi-bit errors and in some cases the entire memory chip can be detected and repaired.

The traditional way to handle fail-stop errors is checkpoint-restart [5]. In this approach, the application executes for a given time and saves its state (in full or in part) to permanent storage. In the event of a detected failure, a checkpoint file is read, data structures are rebuilt, and computation is restarted. A variety of checkpoint-restart schemes have been designed, with varying levels of intervention required by the programmer, checkpoint sizes, and checkpoint frequencies considered [16, 13]. In addition, for certain fault considerations and applications, checkpointing is not required [7, 1].

Emerging architectures are demanding attention to silent data corruption (SDC). Extensive work has been done for SDC detection in numerical computations [14, 2, 11, 8], whereas general methods for detection and correction for SDC have also been proposed [19, 9, 12], but have yet to gain wide adoption.

#### **AMG Resilience**

The resiliency of AMG to SDC has been studied previously [15], where checksums are used to detect SDCs. The approach is limited to dense matrices, but is robust, incorporating checks for matrix-vector multiplications, relaxation, and interpolation.

More recent work [6] reports that AMG is resilient to SDC due to its iterative and multilevel nature. Provided that AMG does not segfault, a SDC with high probability emerges as an error in the solution vector. This error is subsequently removed at the cost of more work. Moreover, the error is reduced on a coarser level, where this error is more pronounced. The recovery scheme addresses a segfault by triplicating key pointers and ranks the three instances when accessed, accept-

ing the pointer with the most credibility. This is done for every access to the protected arrays, therefore yielding resiliency at a large overhead. Regardless, the approach decreases the number of segfaults for AMG in a faulty environment, yet the resiliency overhead is present even in the case when AMG is not exposed to faults.

In contrast, our recovery scheme induces less overhead, even when AMG does not suffer a segfault. In addition, our scheme provides checks that alert the AMG solver of the presence of SDC and attempts to avoid the impact of the fault instead of allowing AMG to remove the error through more iterations.

#### TRANSIENT ERROR DETECTION

We first discuss our error model and assumptions. For this method, we assume that memories are sufficiently protected with ECC and chipkill; as such, we do not model SDC arising in memory. Further, we assume that errors emerge during instruction execution in the solve phase of AMG and that corruptions manifest themselves as bit perturbations is the result of instructions. In addition, during the solve phase the operators A, P, and R on each level as well as the right hand side b are never written only read. As a result, these structures are not checkpointed for SDC recovery since they are only modified through errant stores. To protect these data structures from such writes, one approach is to use the system call mprotect to force the associated memory pages to be read-only. In the case of a write to a protected page, a segfault is raised triggering recovery. This function is used in some asynchronous checkpoint-restart approaches [17] to exploit copy on write capabilities when scheduling pages to be checkpointed.

#### **MultiLevel Recovery Scheme**

As faults occur inside AMG, we classify them as the following. A fault,

- decreases the convergence time;

- increases convergence time;

- leads to convergence to wrong solution; or

- unexpected program termination (crash).

In the case of divergence due to an unexpected termination — e.g., segfault — this is a clear indication that an error has occurred. The other possible results from faults lead to silent data corruption (SDC), but the algorithm still continues to function. SDC may also lead to longer runtimes, or to converging to the wrong solution. We rely on mathematical theory and heuristics of AMG to detect these errors as discussed below.

Checkpoint-restart is the defacto method to recover from failure by allowing the application to crash and restart from a checkpoint or beginning state. We utilize this idea in our recovery from detected errors. By observing the traversal of the AMG hierarchy, we consider each level an *implicit* checkpoint, since the data for that level is computed via the previous level in the hierarchy. It is possible to build a recovery scheme that takes advantage of this implicit checkpoint. In order to exploit this, we define a recovery function to to restart

AMG on the previous level, or if the error is deemed severe, restart the cycle. The code executed by our multilevel recovery scheme is found in Algorithm 1. If a fault is detected, we first determine its severity. Provided the fault is minor we recover from the previous level in the AMG hierarchy. Should a SDC be flagged in the same location again, or the residual check, discussed below, is triggered we rollback to our previous *explicit* checkpoint and restart the solve on the finest level.

#### Algorithm 1: Multilevel Restart

```

1 if retry-same-level or residual-check-failed then

restoreFromCheckpoint (x^k)

{in-memory, fine level}

restartLevel (lev_{

m finest})

4 if down-pass then

if lev \neq lev_{\textit{finest}} then

\lfloor restartLevel(lev-1)

7

if iteration > 0 then

up-pass ← TRUE

down-pass ← FALSE

restartLevel(lev + 1)

10

11

else

12

restartLevel(lev_{finest})

13 if up-pass then

if lev \neq lev_{\textit{coarsest}} then

14

| restartLevel(lev + 1)

15

16

else

up-pass \leftarrow FALSE

17

18

down-pass ← TRUE

restartLevel(lev - 1)

19

```

In order for our restart routine to execute correctly, we create global state information comprised of direction, level, and iteration, that the solver updates as it traverses the hierarchy. Saving and restarting at some point in the hierarchy utilizes the C-language functions sigsetjmp to mark level or cycle restart locations and siglongjmp to facilitate the jumps. These functions store and restore the register state of the program at the point of the call respectively. These functions can be thought of as a label and a non-local goto. In addition, the solution vector periodically creates an in-memory checkpoint at the end of the V-cycle to limit the amount of roll back required. These minor augmentations are designed to be generic to allow them to be added to any sequential or parallel AMG implementation with minimal effort.

#### **Silent Error Detectors**

Faults that do not lead to a unexpected termination become SDC and go unnoticed by the standard AMG algorithm. Here, we add simple augmentations to AMG that allow the detection of SDC. These augmentations vary in their overhead, applicability to other codes, coverage, and recovery cost, as we detail below.

#### Residual Check

The typical stopping criterion for AMG is verifying that the relative residual is less than a given tolerance. If SDC occurs during a cycle, its effect is shown in the residual calculated for that cycle and every cycle thereafter until the error is removed. This is illustrated in our motivating example, Figure 1. Unlike other iterative linear solvers, AMG

solvers do not guarantee that the residual or relative residual monotonically decreases from cycle to cycle. Heuristics show that for a large class of problems, the residual is expected to decrease *nearly* monotonically; therefore, we devise a low cost error check that examines the newly calculated residual and compares it to the previous residual. Due to the non-monotonically decreasing nature of the residual, we use a region of plausibility for the new residual. In this paper, we consider a single order of magnitude in difference; while this is subjective, it is important to note that we are attempting to save the solver from a total restart as we detail in the next section. In addition, the scaling factor in our residual check may be modified depending on the type of problem being solved to enhance its ability to detect SDC and to prevent infinite loops. We also note that this SDC detector extends to other iterative solvers and is not specific to only AMG.

#### Energy Check

AMG does not guarantee that the residual decreases monotonically at the end of every cycle. However, it does guarantee a decrease in the A-norm of the error every cycle. Although we are unable to measure the error directly, we use AMG's sense of energy to check for SDCs, termed the *energetic stability*,

$$E = \langle A\mathbf{x}, \, \mathbf{x} \rangle - 2\langle \mathbf{x}, \, \mathbf{b} \rangle \tag{1}$$

The energetic stability is valid on each level. That is, energy at level i in the down-pass of the V-cycle is greater than the energy calculated at level i in the down-pass in the next V-cycle. We utilize the energy check as a guarantee that the results calculated on a given level are correct before we continue to the next level. This allows recovery to proceed by the multilevel restart algorithm shown in, Algorithm 1.

In its current form, (1) is costly as it requires one sparse matrix-vector multiply (SpMV) and two inner products. The latter limits scalability at large core counts. On the down-pass and not on the coarsest level, the residual is formed. This operation provides us with  $A\mathbf{x}$  at no cost. On the up-pass, the computation is more expensive, but we rewrite (1) in the following form

$$E = \langle \mathbf{r}, \, \mathbf{b} \rangle - 2\langle \mathbf{x} - \mathbf{b}, \, \mathbf{b} \rangle. \tag{2}$$

If we preform the local operations for both inner products and issue a single reduce that operates on the two local inner products in the same call, issues with scalability are minimized.

#### **Segfault Recovery**

Unlike the results of the energy or residual check where there is a global view of the result of each check once the operation completes, segfaults are local to the process on which they occur. One approach to recovery is to elevate a local segfault to a global segfault, thus allowing recovery via Algorithm 1, however, such a scheme can cause high overheads and will increase the amount of work redone. A parallel application is considered as a decomposition into two phases: communication and computation. AMG is composed of basic linear algebra operations such as SpMV operations and vector operations. All of these operations have an idempotent form at the expense of a temporary vector. For example,

y = Ax produces the same result independent of the number of times the operation is executed. Due to there idempotent nature, recovery from a segfault is straightforward: restart the operation by the use of the same C functions required for Algorithm 1, but use new recovery points for the idempotent operations. The error is transient and does not manifest itself as a segfault again. If the segfault occurs during a non-idempotent operation such as communication, recovery by restart using Algorithm 1 is possible, but important state information, communication library, may be corrupted – e.g. redundantly sent messages. By message logging we are able to eliminate redundant messages, but still face possible corruption in the communication library. As the results in Section 5 show, segfaults in non-idempotent regions represent a small portion of segfaults (< 3%) for the results in Table 2 and Table 3; therefore, we do not add this extra overhead to our recovery scheme.

#### PERFORMANCE MODEL

In this section, we construct a performance model in order to highlight the scalability of our approach and the impact on computational complexity in the scheme. In particular, we develop this model for our algorithmic based detectors and multilevel recovery scheme in order to understand the impact on the convergence properties of the AMG solver and to see the potential benefits of the methodology. In Section 5.3, we present results from fault injection experiments on solves of AMG with various error rates and detectors enabled.

#### **Basic Model**

AMG is divided into two phases: setup and solve. These phases do not overlap leading to the basic performance model, for the runtime of the solution to Ax=b:

$$T_{\text{total}} = T_{\text{setup}} + T_{\text{solve}}$$

(3)

During the solve phase of AMG, there are several choices that influence the performance of the solver such as depth of the cycle, type of cycle, smoother, and etc. In response, our performance model below (see (4)) is designed to abstract many of these choices yielding a practical tool, while at the same time providing enough detail to draw firm conclusions.  $T_{\rm cycle}$  is the time for a single cycle (iteration) in AMG, and  $n_{\rm cycles}$  is the number of cycles until convergence. In our model,  $c_i$  and  $t_i$  are the number of visits and time on level i, respectively. Since we consider faults only in the solve phase, we introduce a term  $\beta$  that represents the percent increase in iteration count due to reduced convergence as result of a SDC.  $\beta$  is more accurately modeled by  $T_{\rm repeat}$ , where  $r_i$  is the number of times a level is repeated due to a SDC.

$$\begin{array}{lcl} T_{\rm solve} & = & T_{\rm cycle} n_{\rm cycle} \left(1+\beta\right) \\ & = & T_{cycle} n_{cycle} + T_{repeat} \\ & = & \sum_{i=0}^{n_{\rm level}} c_i t_i n_{\rm cycle} + \sum_{i=0}^{n_{\rm level}} r_i t_i \end{array} \tag{4}$$

The number of cycles (iterations) required for AMG to converge to d digits of accuracy is given by  $\frac{d}{-\log_{10}(\rho)}$ , where  $\rho$  is the convergence factor, the spectral radius of the iteration matrix used during the relaxation step. If faults occur during the solve phase, convergence *potentially* deteriorates to  $\hat{\rho} = \alpha \rho$

such that  $\rho < \hat{\rho} < 1$ . As convergence deteriorates, additional cycles are required to achieve convergence to the same accuracy. In some situations, the increase is dramatic as outlined in Figure 1. Our detection and recovery schemes limit the number of extra cycles required by maintaining the average convergence factor of the fault free problem in most cases, or a few more iterations if the average convergence factor is only slightly affected.

#### **Segfault Recovery**

To implement the segfault recovery outlined in Section 3.3, we need to issue calls to sigsetjmp and siglongjmp. These calls, along with subsequent retry of the regions after a segfault, add time not reflected in our model (4). To extend our model we modify  $T_{\rm cycle}$  in (4) with the addition of a  $T_{\rm resiliency}$  term that is the overhead of the added resiliency measures.

$$T_{\text{resiliency}} = T_{\text{seg}}$$

(5)

Here  $T_{\rm seg}$  is the overhead of segfault recovery. Recovery from a segfault has us restarting the local operation. This operation time is less than the level time. Our model provides an upper bound on the restart time by defining  $r_i$  as the sum of the maximum number of segfaults experienced on a single rank on level i during each cycle.

#### **Residual and Energy Check**

To add the residual and energy checks to our performance model in (6), we make an extension to (5), where  $T_{\rm checkpoint}$  is the time to checkpoint the solution vector on the fine level,  $T_{\rm residual}$  is the overhead of the residual calculation, and  $T_{\rm energyDown}$  and  $T_{\rm energyUp}$  are the overhead of doing the energy check on each level on the down and up-pass respectively. This yields

$$T_{\text{resiliency}} = T_{\text{seg}} + T_{\text{checkpoint}} + T_{\text{residual}} + T_{\text{energyDown}} + T_{\text{energyUp}}.$$

(6)

#### **Comparison of Time to Solution**

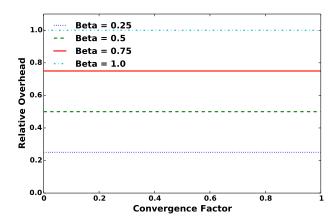

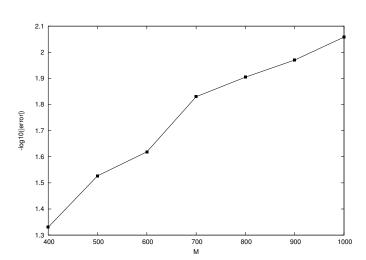

Faults that occur during the solve phase that require extra iterations to converge, increase the average convergence factor. As the average convergence factor approaches 1.0 the number of iterations required to converge grows exponentially. Ultimately, the same *asymptotic* convergence factor is likely achieved, yet the effective convergence factor for the run increases. In Figure 3, we see the relative overhead is equal to  $\beta$ . Each trend is associated with a different value for  $\beta$ , which represents the percent increase in iteration count over the fault free case. That is  $\beta = 1.0$  corresponds to taking twice as many iterations to solve the problem when compared to the fault free case, or a relative overhead of 1. The overhead due to a SDC is proportional to the amount of work that is redone. For example, if a problem's average convergence factor changes from 0.2 to 0.3, this is equivalent to  $\beta = 0.3$  or a 1.3x increase in the number of iterations of the original problem. This is only compounded as the average convergence factor approaches 1.0 where the number of iterations required grows exponentially. Our methods keep  $\beta$  small which limits extra computation.

Figure 3. Relative overhead in converging to a fixed tolerance for various values of  $\beta$ .

#### **EXPERIMENTAL RESULTS**

To better understand AMG in a faulty environment, we use the fault injector FlipIt [4] to perturb with a bit-flip the result of a single dynamic instruction during the solve phase of the AMG solver of Hypre<sup>1</sup>. In the following (except Section 5.1), 1000 fault injection trials are conducted on Blue Waters where we solve a 2D Laplacian with zero on the boundaries using 16 processes and 16,384 unknowns per process. Because of its rapid convergence and lightweight hierarchy, this problem highlights the overhead of our detectors and recovery scheme with more severity than a more difficult problem where the solver itself is more computationally heavy. Moreover, due to the rapid convergence for this model problem, the errors should be quickly removed by the efficient lightweight hierarchy. When a fault is injected it is classified by the fault injector in one of three main types: pointer refers to all calculations directly related to use of a pointers (loads, stores, and address calculation), control refers to all calculations of branching and control flow (comparisons for branches and modification of loop control variables), arithmetic refers to pure mathematical operations.

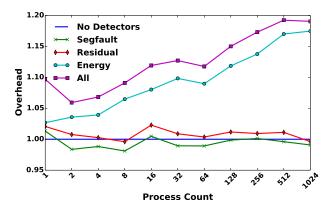

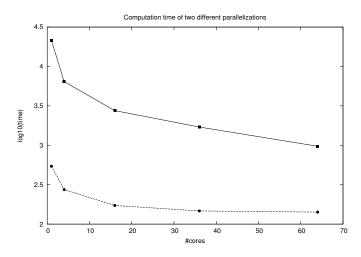

#### Overhead

By their nature, transient faults are infrequent events, which implies that any resiliency scheme should limit the overhead introduced in a fault free case. To determine the practicality of our detectors, it is critical to assess both the ability to detect as well as their cost (overhead). Figure 4 details the overhead with respect to solve phase execution time of each SDC detector used. We enable the multilevel recovery scheme for every configuration in which a detector is active. Because we are determining the overhead in a fault free case, the multilevel restart code is never executed; therefore, we do not include the time to restart the AMG solve in the reported times. We enable the energy check on every level to provide a worst case scenario. In addition, we in-memory checkpoint the solution vector at the end of every V-Cycle for the same reason.

https://computation-rnd.llnl.gov/linear\_solvers/

software.php

Figure 4. Overhead in solve time of fault detectors compared to the original AMG code.

We see that segfault (Segfault) recovery and the residual check (Residual) yield a lower overhead than a energy check (Energy). In fact, their runtimes are similar to the original code, differing by  $\pm 1\%$  regardless of process count. This is offset by the fact that the energy check is more powerful, able to check for SDCs at each level. Preforming the energy check on each level limits the amount of work that needs to be redone. Because of their relative low combined overhead (< 1.5%), segfault recovery and the residual check, we refer to both of them together as the Low Cost configuration. Even with all detectors and our recovery scheme enabled in a worst case scenario, we have an observed maximal overhead of < 20%. In practice, the frequency of a checkpoint, and on which levels the energy check is active would be modified to meet a more strict resiliency budget.

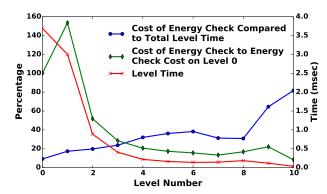

To better characterize the overhead of the energy check, in Figure 5 we see the percentage of level time consumed by the energy check. As we move from the finest level (0) to the coarsest level (10) the problem size decreases, but each level becomes more dense. As the density of the level increases, we see the energy check having a greater influence on level time. Although we have an increase in percentage of level time, the energy check is cheaper on the coarsest levels than on the finest level. The energy check is relatively more expensive on level 1 because although the number of unknowns in the problem is less on level 1, the number of non-zero entries is roughly the same leading to a denser matrix used in the check.

#### **Fault Characteristics**

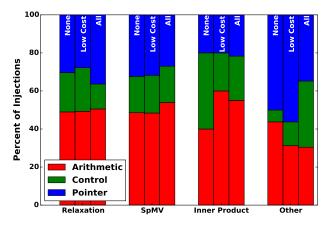

In order to devise effective resiliency schemes, we need to determine where faults are injected into the AMG solve phase. We again investigate the worst case scenarios for both the residual and energy check. Faults are injected randomly throughout the solve phase with each dynamic instruction having a uniform probability of  $1\mathrm{e}^{-8}$ . Seeding the fault injector differently for each trial yields injections in all iterations of the solve.

From Table 1 we see that most of the faults are injected into Relaxation and the SpMV routines, which includes A for the residual, P, and R. This is expected since most of time is spent in these routines. We classify Other routines as all other

Figure 5. Characterization of cost of the energy check compared to total time on each level and cost relative to the energy check on level 0. Total level time is the sum of original level time and time for the energy check on that level.

| Operation     | No Detectors | Low Cost | All  |

|---------------|--------------|----------|------|

| Relaxation    | 50.1         | 47.4     | 42.5 |

| SpMV          | 47           | 49.1     | 48.2 |

| Inner product | 1.1          | 1.7      | 6.7  |

| Other         | 1.8          | 1.8      | 2.6  |

Table 1. Percentage of injections in AMG components.

Figure 6. Breakdown of faults injected into AMG components based on the type of instruction executed.

functions used during the Hypre solve phase — e.g. cycling code, vector copy, and scaling routines. As we add the energy check that requires two inner products, we see a higher percentage of faults occurring in this routine.

Notably, in Figure 6, we see that a significant number of faults are injected into *pointer* and *arithmetic* instructions. The high degree of *pointer* injections is due to using sparse matrix data structures which uses indirection to access the data elements. A corrupted pointer often leads to a segfault, and corruption of *arithmetic* computation can produce results as shown in Figure 1, thus motivating the need for an efficient detection and recovery scheme.

Adding our SDC detectors increases resilience, but may also suffer from false positives. The comparisons for the residual and energy check represent a small portion of the dynamic instructions during the solve phase and are unlikely to experience a SDC. The computation to form the quantities for the comparisons are more likely candidates. Regardless of where SDC occurs, a false positive in the residual or energy check is handled as if it was a true positive.

#### **Convergence Analysis**

In the following convergence study, we use the same initial guess and right hand side to limit variability in the results. Moreover, since an injected fault may lead to an increase in the number of iteration, we set the maximum number of iterations at 20. This allows 4 more iterations to converge.

| Results          | No Detectors | Low Cost | All |

|------------------|--------------|----------|-----|

| Converge         | 73.5         | 98.6     | 99  |

| Did not converge | 1            | 0.4      | 0   |

| Crashed          | 25.5         | 1        | 1   |

Table 2. Percentage of trials that converge with a single injection.

In Table 2, we see that a single injection has a large impact on convergence, with 25.5% of all trials segfaulting before converging in the unmodified version of AMG. A high rate of segfaults is expected since one-third of injections are into instructions classified as *pointer*. In configurations where segfault recovery is enabled, our approach successfully recovers, thus allowing the solve to continue. With the aid of our SDC detectors we intercept 12% of injections. If uncaught, these injections would lead to extra iterations.

| Results          | No Detectors | Low Cost | All  |

|------------------|--------------|----------|------|

| Converge         | 0            | 86.2     | 84.8 |

| Did not converge | 0            | 2.8      | 0.2  |

| Crashed          | 100          | 11       | 15   |

Table 3. Percentage of trials that converge with multiple injections. Average of 14 injections per trial for  $Low\ Cost$  and All. Average of 4 injections per trial for  $No\ Detectors$ .

With multiple injections, Table 3 shows a large deterioration in convergence for the unmodified AMG implementation with all trials crashing due to segfaults. However, our augmented versions of AMG remains convergent even in the presence of a high number of faults. Enabling the energy check increases sensitivity to SDC allowing us to detect more of them, but the check also incurs a cost. The energy check flags SDC at a rate that is 1.5x that of the residual check, but recovering from the SDC is more expensive than letting the AMG naturally iterate through the error. Some SDC that just triggers the energy check only slightly increases the energy from the previous iteration triggering the check, but not enough to have a high impact on convergence. In addition, the energy check also increases the parallel communication in routines where idempotent segfault recovery is not possible. Consequently, as the number of faults encountered per solve increases, the energy check becomes less useful.

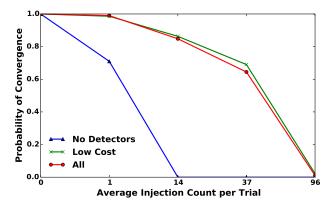

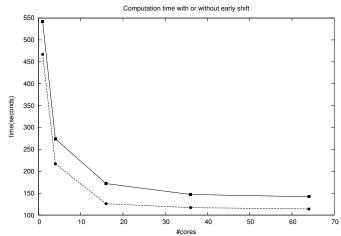

We now look at how convergence is affected by the number of injections in both the *Low Cost* and *All* configurations. In Figure 7, we increase the average number of injections in each

trial until the probability of convergence drops below 0.5. We compute the probability of convergence by dividing the number of trials that converge by the number of trials.

Figure 7. Convergence of AMG with multilevel recovery scheme.

Even with an average of 37 faults injected during each trial, our resilient version of AMG converges in over 69% of trials for Low Cost and in over 62% of trials for All. Again we see the duality of the energy check. It is able to detect more SDC, even those that do not significantly affect convergence. However, after this point in the testing the probability of convergence decreases dramatically. This is because the solver is making little progress due to high amounts of recovery and because the segfaults are emerging in non-idempotent routines. Indeed, 54% of trials of the *Low Cost* configuration and 75% of the All trials terminate due to segfaults in nonidempotent regions. This suggests that if the code were restructured with more idempotent regions, convergence rates would improve. For the remaining faults, when a SDC is detected we attempt to recover, but as we are in the recovery process we suffer more faults that require a restart allowing almost no forward progress.

#### **CONCLUSIONS**

Through the use of a combination of application specific detectors we are able to detect SDC that significantly impact convergence. With SDC detected our proposed multilevel recovery scheme is able to recover and converge with a high probability even for a high number of faults. Going forward, fault consideration is going to become a driving factor in design of long running and large scale software. With the AMG augmentations presented and evaluated in this paper, AMG has shown it is capable of being used in faulty environments. Moreover, the residual check and the local segfault recovery scheme are general and likely to be valuable in other numerical libraries.

#### **ACKNOWLEDGMENTS**

This work is sponsored by the United States Air Force Office of Scientific Research under grant FA9550–12–1–0478. This work is supported by the Office of Science, Office of Advanced Scientific Computing Research, of the U.S. Department of Energy under Contract DE–AC02–06CH11307. This research is part of the Blue Waters sustained-petascale

computing project, which is supported by the National Science Foundation (awards OCI–0725070 and ACI–1238993) and the state of Illinois. Blue Waters is a joint effort of the University of Illinois at Urbana-Champaign and its National Center for Supercomputing Applications.

#### **REFERENCES**

- Agullo, E., Giraud, L., Guermouche, A., Roman, J., and Zounon, M. Towards resilient parallel linear Krylov solvers: recover-restart strategies. Rapport de recherche RR-8324, INRIA, July 2013.

- 2. Anfinson, C. J., and Luk, F. T. A linear algebraic model of algorithm-based fault tolerance. *IEEE Trans. Computers 37*, 12 (1988), 1599–1604.

- 3. Borkar, S. Designing reliable systems from unreliable components: The challenges of transistor variability and degradation. *IEEE Micro* 25, 6 (Nov. 2005), 10–16.

- 4. Calhoun, J., Olson, L., and Snir, M. FlipIt: An LLVM based fault injector for HPC. In *Proceedings of the 20th International Euro-Par Conference on Parallel Processing (Euro-Par '14)* (2014).

- Cappello, F., Geist, A., Gropp, W. D., Kale, S., Kramer, B., and Snir, M. Toward exascale resilience: 2014 update. Supercomputing Frontiers and Innovations 1 (2014), 1–28.

- Casas, M., de Supinski, B. R., Bronevetsky, G., and Schulz, M. Fault resilience of the algebraic multi-grid solver. In *Proceedings of the 26th ACM international* conference on Supercomputing, ICS '12, ACM (New York, NY, USA, 2012), 91–100.

- 7. Chen, Z. Algorithm-based recovery for iterative methods without checkpointing. In *Proceedings of the 20th international symposium on High performance distributed computing*, HPDC '11, ACM (New York, NY, USA, 2011), 73–84.

- 8. Chen, Z. Online-abft: An online algorithm based fault tolerance scheme for soft error detection in iterative methods. In *Proceedings of the 18th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*, PPoPP '13, ACM (New York, NY, USA, 2013), 167–176.

- 9. de Kruijf, M., Nomura, S., and Sankaralingam, K. Relax: An architectural framework for software recovery of hardware faults. In *Proceedings of the 37th International Symposium on Computer Architecture (ISCA)* (2010).

- Elliott, J., Hoemmen, M., and Mueller, F. Evaluating the impact of SDC on the GMRES iterative solver. In *Proceedings of the 2014 IEEE 28th International Parallel and Distributed Processing Symposium*, IPDPS '14, IEEE Computer Society (Washington, DC, USA, 2014), 1193–1202.

- 11. Elliott, J., Mueller, F., Stoyanov, M., and Webster, C. Quantifying the impact of single bit flips on floating point arithmetic. Tech. rep., Oak Ridge National Laboratory, August 2013.

- 12. Fiala, D., Mueller, F., Engelmann, C., Riesen, R., Ferreira, K., and Brightwell, R. Detection and correction of silent data corruption for large-scale high-performance computing. In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, SC '12, IEEE Computer Society Press (Los Alamitos, CA, USA, 2012), 78:1–78:12.

- 13. Hargrove, P. H., and Duell, J. C. Berkeley lab checkpoint/restart (BLCR) for linux clusters. *Journal of Physics: Conference Series* 46, 1 (2006), 494.

- 14. Huang, K.-H., and Abraham, J. A. Algorithm-based fault tolerance for matrix operations. *IEEE Trans. Comput.* 33, 6 (June 1984), 518–528.

- 15. Mishra, A., and Banerjee, P. An algorithm-based error detection scheme for the multigrid method. *IEEE Trans. Comput.* 52, 9 (Sept. 2003), 1089–1099.

- 16. Moody, A., Bronevetsky, G., Mohror, K., and Supinski, B. R. d. Design, modeling, and evaluation of a scalable multi-level checkpointing system. In *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*, SC '10, IEEE Computer Society (Washington, DC, USA, 2010), 1–11.

- 17. Nicolae, B., and Cappello, F. AI-Ckpt: Leveraging memory access patterns for adaptive asynchronous incremental checkpointing. In *Proceedings of the 22nd International Symposium on High-performance Parallel and Distributed Computing*, HPDC '13, ACM (New York, NY, USA, 2013), 155–166.

- 18. Ruge, J. W., and Stüben, K. Algebraic multigrid. In *Multigrid methods*, vol. 3 of *Frontiers in Applied Mathematics*. SIAM, Philadelphia, PA, 1987, 73–130.

- Sastry Hari, S. K., Li, M.-L., Ramachandran, P., Choi, B., and Adve, S. V. mSWAT: Low-cost hardware fault detection and diagnosis for multicore systems. In Proceedings of the 42nd Annual IEEE/ACM International Symposium on Microarchitecture, MICRO 42, ACM (New York, NY, USA, 2009), 122–132.

- 20. Snir, M., Wisniewski, R. W., Abraham, J. A., Adve, S. V., Bagchi, S., Balaji, P., Belak, J., Bose, P., Cappello, F., Carlson, B., Chien, A. A., Coteus, P., DeBardeleben, N. A., Diniz, P. C., Engelmann, C., Erez, M., Fazzari, S., Geist, A., Gupta, R., Johnson, F., Krishnamoorthy, S., Leyffer, S., Liberty, D., Mitra, S., Munson, T., Schreiber, R., Stearley, J., and Hensbergen, E. V. Addressing failures in exascale computing. *International Journal of High Performance Computing Applications* 28, 2 (May 2014), 127–171.

- 21. Sridharan, V., and Liberty, D. A study of dram failures in the field. In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, SC '12, IEEE Computer Society Press (Los Alamitos, CA, USA, 2012), 76:1–76:11.

# Exploiting computing power of Xeon and Intel Xeon Phi for a Molecular Dynamics Application

Benny Mathew, Nitin Rai, Apaar Gupta and Amit Harode

Tata Consultancy Services Quadra II, Hadapar, Pune, India 411028 {benny1.m, rai.nitin, apaar.gupta, amit.harode}@tcs.com

#### **ABSTRACT**

Molecular Dynamics (MD) is a computational technique with applicability in fields as diverse as material science, biomolecules and chemical physics. Assisted Model Building with Energy Refinement (AMBER) is an MD package and it uses Message Passing Interface (MPI) to scale in multi-core and cluster environments.

In our earlier work [1], we modified one of AMBER's algorithms called Generalized Born (GB) algorithm to run optimally on the Xeon Phi co-processor. This improved performance by 277% on the co-processor. The same changes improved performance on the host server by 80%.

In this paper, we extend our earlier work and implement a symmetric solution using both the host server and the coprocessor. Since the calculations in GB algorithm involve interactions between all possible atom combinations, it has been very difficult to scale GB algorithm in distributed memory. We evaluate various alternate techniques using combination of MPI and Open Multi-Processing (OpenMP) to get a scalable solution that utilizes the computing power of both the host server as well as the co-processor.

#### **Author Keywords**

molecular dynamics; AMBER; HPC; performance; Intel Xeon Phi; nucleosome; generalized Born; parallel programming, OpenMP, MPI

**ACM Classification Keywords** C.4 PERFORMANCE OF SYSTEMS

#### INTRODUCTION

Molecular mechanics models consist of spherical atoms connected by springs that represent bonds [2]. The internal forces experienced in the model are described using simple

HPC 2015, April 12 - 15, 2015, Alexandria, VA, USA

© 2015 Society for Modeling & Simulation International (SCS).

mathematical functions. Hooke's law is commonly used to describe bonded interactions, and the non-bonded atoms might be treated as inelastic hard spheres or may interact according to a Lennard-Jones potential. Using these simple models, an MD simulation numerically solves Newton's equations of motion. This allows the structural changes to be observed with respect to time.

MD is used to obtain information on the time evolution of conformations of proteins and other biological macromolecules. MD is used to obtain kinetic and thermodynamic information. Simulations can provide fine detail concerning the motions of individual particles as a function of time. They can be utilized to quantify the properties of a system at a precision and on a time scale that is otherwise inaccessible.

As molecular systems consist of large number of particles with complex interaction mechanisms, it is impossible to ascertain useful properties analytically. MD simulation circumvents this problem by using numerical methods. Precise MD simulations of biological processes are computationally expensive. This is because biological processes take place in aqueous solvents and hence the solute processes as well as solvent interactions need to be simulated. The GB algorithm is an implicit solvent framework that replaces the aqueous solvent by an infinite continuum medium with electrostatic properties of solvent.

Intel's Xeon Phi coprocessor is a symmetric multiprocessor in the form factor of a PCI express device. Each coprocessor has more than 50 cores clocked at 1 GHz or more, supporting 64-bit x86 instructions. The exact number of cores depends on the model and the generation of the product. Cores of Xeon Phi coprocessors are interconnected by a high-speed bidirectional ring, which unites L2 caches of the cores into a large coherent aggregate-cache of over 25 MB in size. The coprocessor also has 6 GB to 16 GB of onboard GDDR5 memory. The speed and energy efficiency of Xeon Phi coprocessors comes from its vector units. Each core contains a vector arithmetic unit with 512-bit SIMD vectors supporting a new instruction set that includes fused multiply-add, reciprocal, square root, power and exponent operations, commonly used in physical modeling and statistical analysis. In order to completely exploit the Xeon Phi coprocessors and its host server, applications must

utilize several levels of parallelism [3]. The levels of parallelism are as follows:

- Data parallelism to employ the 512-bit vector units (vectorization)

- Task parallelism in shared memory to utilize more than 200 logical cores.

- Task parallelism in distributed memory to scale an application across multiple coprocessors or multiple compute nodes.

#### **RELATED WORK**

In this study, we work to optimize GB model implemented as part of AMBER [4] [5] simulation program to fully exploit the combined computational power of Intel Xeon host server and Xeon Phi co-processor. AMBER is a collective name for a suite of programs to carry out MD simulation.

NAMD (NAnoscale Molecular Dynamics program), GROMACS (GROningen MAchine Chemical Simulations), CHARMM (Chemistry at **HARvard** Macromolecular Mechanics) and miniMD are popular MD packages apart from AMBER. There has been significant effort to speed up MD simulation. One set of effort revolves around changing the algorithm to improve performance and the second set revolves around changes that exploit the latest available hardware.

In MD simulations, considerable time is consumed in calculating atomic interactions. One way of reducing the interactions is by ignoring remote atom interactions. This is done by constructing a list of interacting atoms within a given cut-off distance called the neighbor list. By carrying out computations for an atom with only its neighbors, the time for energy and force computations reduces without sacrificing accuracy [6].

Pennycook et al. [7] reports five times improvement in single precision Sandia's miniMD benchmark than original scalar code running on Intel Xeon Processor, using code level and algorithmic modifications. Also, addition of a single Intel Xeon Phi co-processor gives additional two times performance enhancement by using effective SIMD utilization. In their work, they use platform-specific intrinsic for force computations and building of neighbor list.

The GB algorithm's relaxation of the dielectric shielding provided by an implicit solvent model and the use of cut-off distance helps it to get better performance as compared to explicit solvent simulations. However, the performance gain is limited due to more complex functional forms and the two extra interaction stages necessary to calculate Born radii and the derivative chain rule terms contributing to the force [8]. To overcome these limitations, NAMD divides

calculations into many small work units using a three-tier decomposition scheme, assigns a balanced load of work units to processors, and schedules work units on each processor to maximize efficiency [9]. Larsson and Lindahl [8] used a rescaling transformation to make the standard GB expression a function of a single variable. This enabled an efficient tabulated solution and when this solution was implemented in GROMACS, the throughput doubled for their test cases.

Goetz et al. [10] implemented GB molecular dynamics of AMBER package on NVIDIA's graphics processing units (GPUs) by rewriting the original Fortran code into NVidia's proprietary language CUDA. Through use of unique tiled workload distribution as well by use of mixed precision model, they were able to get excellent performance at a slight cost in accuracy. Goetz's solution for AMBER offloads almost all the computation to the GPU while the host remains idle. Tanner et al. [11] implemented a solution for NAMD where there is overlap of computations on both CPU and GPU. The GB computations are carried out on the GPU and the surface area computations are carried out on the CPU.

We have optimized GB mainly for Intel Xeon Phi architecture. We use shared memory parallelism, sharing of neighbor lists and modification of loop structures to reduce communication overheads between threads. The computations retain double precision variables to preserve the accuracy of results. After optimizing the application for Xeon Phi, we implement a solution to efficiently use the computing power of both the host as well as co-processor concurrently.

#### **GENERALIZED BORN ALGORITHM**

In MD simulation, the most important quantity calculated is total energy of molecular system. From the atomic coordinates of molecules and energy, we can calculate the forces between atoms. From these forces, velocity can be calculated for each atom and using these velocities, new positions of atoms can be calculated. This flow is repeated for a number of times as required. The repetitions are usually of the order of tens of thousands. Typical biomolecules like proteins and nucleic acids hundreds to tens of thousands of atoms. In order to get meaningful results this biomolecule (solute) is immersed in an aqueous medium (solvent). Consequently, number of atoms for MD simulations increases intensely, making simulation computationally costlier. However, in bio-molecular simulations, the behavior of solute is more of interest than that of the solvent. GB is an implicit solvent model that replaces solvent medium by infinite continuum environment with similar dielectric properties of solvent, therefore eliminating calculations for aqueous medium. This approach helps to run MD simulation of large molecules for long simulation times and generate more useful result.

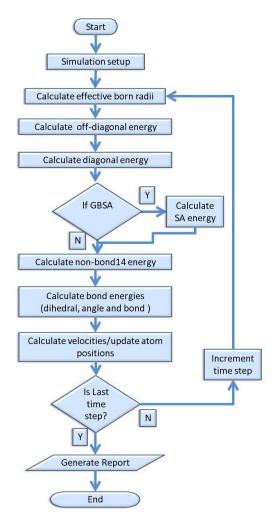

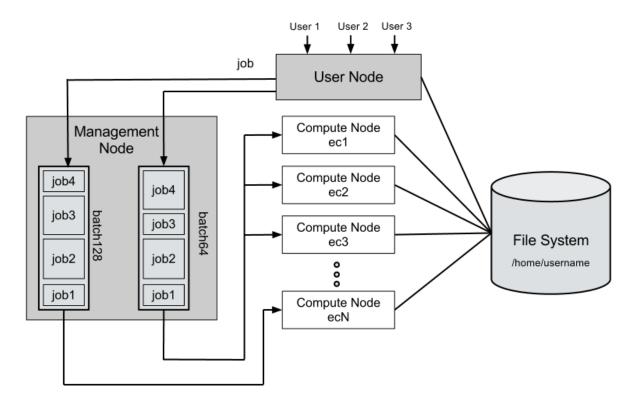

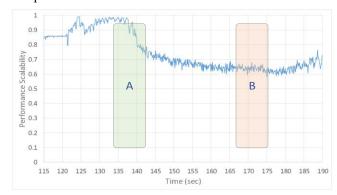

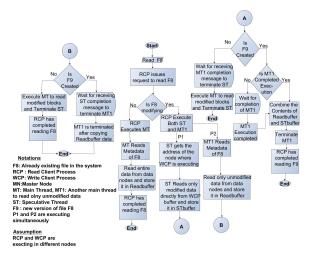

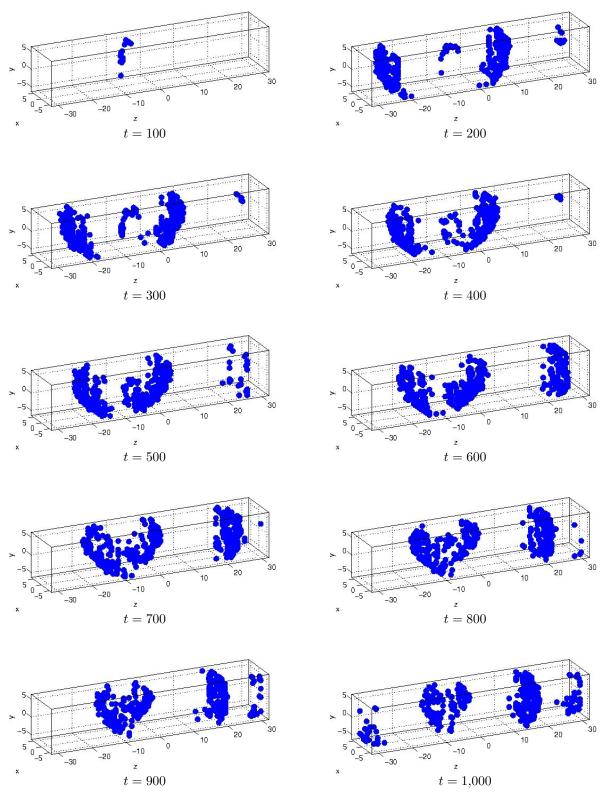

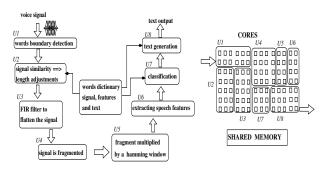

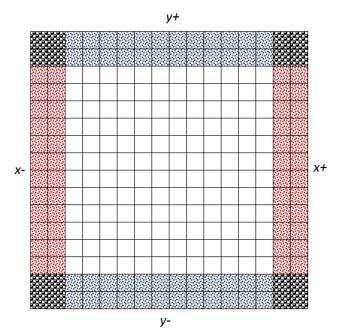

Figure 1: Generalized Born Algorithm Flow

The flow of GB simulation is shown in Figure 1. Out of the steps shown in the diagram, three steps take bulk of the simulation time and these three steps are explained in the following section.

#### **Effective Born Radii Calculation**

The effective Born radius of an atom is the degree of its burial inside the large solute molecule. The effective Born radius is calculated using relative positions of surrounding atoms. To save on computations, only atoms that are within a distance threshold from another atom are considered for calculation. However, to come up with the neighbor list, a full pass of all atoms combinations is required. Since the atoms move at the end of each time-step, neighbor list needs to be built at each time-step.

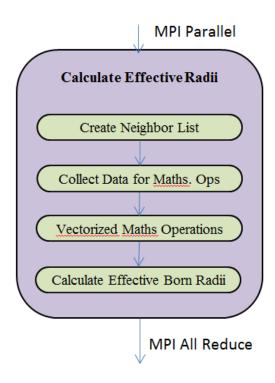

In the original GB code, each MPI [12] rank is assigned a set of atoms and Figure 2 shows some of the steps to calculate effective Born radius of each atom. There are essentially four loops in the calculation. The first loop

Figure 2: Effective Radii Computation

creates the neighbor list. This loop is triangular. This means that the loop starts from the atom that is next to current atom and ends with the last atom. The subsequent loops iterate only for atoms in a neighbor list. The second loop iterates to collect data on which complex mathematical operations need to be performed. By collecting the data, one can perform the operations in SIMD (Single instruction, multiple data) fashion, thereby improving performance. These mathematical operations are performed in the third loop. The mathematical operations include calculation of inverse, square root and exponents. The last loop is where effective Born radius is calculated. At the end of this loop, each node would have partial effective Born radius of several atoms. The mpi allreduce call here consolidates these from each node and combines them to get final effective Born radius for each atom.

#### **Non-diagonal Energy Calculation**

The non-diagonal energy calculation has a flow similar to effective Born radius calculation. In the fourth loop instead of effective Born radii, various non-diagonal energies and forces between atoms are calculated. By looping over all pairs of atoms, it computes the gas-phase electrostatic energies, the Lennard-Jones (LJ) terms and the off-diagonal GB terms. In addition, it updates forces with derivatives of GB energy and gas-phase terms. Further, it accumulates the derivate of off-diagonal terms with respect to inverse effective radii. The threshold distance to calculate neighbor list is typically set larger than the threshold set for radii

calculation, as smaller cut off will lead to less accurate results.

#### **Diagonal Energy Calculation**

In this section of the code, the diagonal or self-energy terms of GB model is computed. It updates force vectors by taking derivatives of GB terms (including the diagonal terms) with respect to the effective radii. This calculation follows similar flow and cut-offs for neighbor list is same as that of the effective Born radii calculation. One difference in loop structure of diagonal energy calculation is that the first loop iterates through all atoms. This is unlike radii and off-diagonal calculation, where first loop is triangular.

#### **OPTIMIZATIONS FOR INTEL XEON PHI**

We use Nucleosome workload to test AMBER-GB performance on Intel Xeon Phi. Nucleosome is a compact molecular structure with 25095 atoms that acts as a basic packing unit of a usually very long DNA molecule in a living cell with nucleus. It is wound around a core of proteins, such as a thread wound on a spool. The simulation uses SHAKE algorithm with a 2-femtosecond time step and no cut-off for the non-bond terms. The cut-off used for calculation of effective Born radii is 15 Angstroms.

The performance of any MD application is measured in nanoseconds per day (ns/day). This stands for the number

of nanoseconds that the MD application will simulate if the application is run for 24 hours.

The host server used for the tests features two Intel CPUs e5-2697 with 64 GB memory. Each CPU has 12 physical cores running at 2.7 GHz. The coprocessor used is Intel Xeon Phi 7120. It has 61 cores, each running at 1.23 GHz and has 16 GB memory. The original MPI code was compiled and linked to Intel MPI library version 5 (update 2).

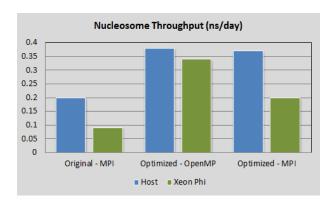

With the nucleosome workload, the original GB code gave throughput of 0.20 ns/day on the host. On the Xeon Phi, the throughput was 0.09 ns/day. Throughput using both host and Xeon Phi together was slower than just the host as the original code did not have any mechanism to distribute work across asymmetric nodes.

First we optimized GB to run only on Intel Xeon Phi in native mode and then optimized it to use the both the host server as well as the Xeon Phi co-processor. These optimizations are discussed as follows:

#### **Data and Task Parallelism in Shared Memory**

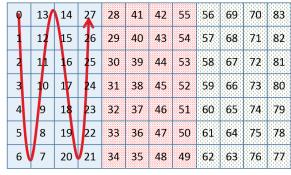

Various optimizations were carried out first on Xeon Phi (native mode). Only a summary of these optimizations are given here. These are explained in more detail in Harode et. al. [1].

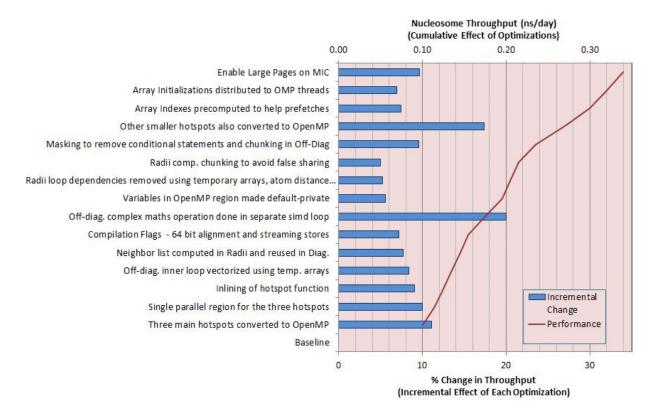

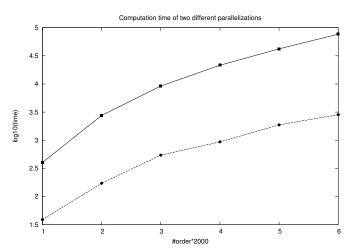

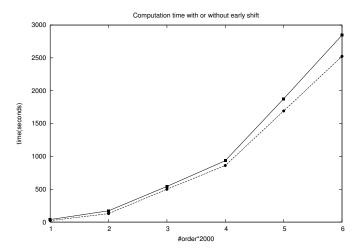

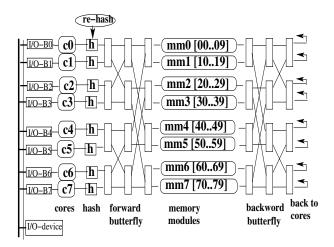

Figure 3: Native Optimizations

Figure 4: Performance after Native Optimizations

Though all the optimizations were manually carried out, tools like Intel's vec-report [13] and vTune helped to identify the bottlenecks. Adding vec-report flag to Intel compiler gives detailed diagnostics about whether the loops in the code were optimized. Vec-report also gives possible strategies to get a loop to vectorize. VTune is a profiling software that gives useful information like vectorization intensity of loops, data access latencies and CPU utilization at line level as well as at function level of code.

Figure 3 shows the list of optimizations that were carried out. The line in the graphs shows the performance in ns/day as each change is combined together over the baseline. The bars show the incremental performance improvement by each optimization.

The optimizations include application of vectorization techniques like masking, latency reducing techniques like pre-computing of indexes and batching. We also employed techniques to avoid reduction and false sharing. Some of the optimizations, such as reuse of neighbor list and deferred computations to improve SIMD, required extensive code modifications.

The same set of optimizations was carried out on the original MPI code as well as on the modified one using OpenMP [14]. The version of OpenMP library used was 3.0 and it significantly improved throughput of GB algorithm on Xeon Phi. From a baseline of 0.09 ns/day on the Xeon Phi, and with the same set of optimizations, the throughput improved to 0.20 ns/day on the MPI code and to 0.34 ns/day on the OpenMP code [Figure 4]. These optimizations helped improve the throughput on the host too, though the quantum of improvement was not of the same order as observed on Xeon Phi. On the host server, for both the MPI as well as OpenMP code, the performance improved from 0.20 ns/day to 0.36 ns/day.

#### **Task Parallelism in Distributed Memory**

Now that the performance improved on both host as well as on Xeon Phi, the next step was to combine the computing power of both. The first step was to arrive at an optimal distribution of the atoms between the host and Xeon Phi. The effective Born radii and diagonal energy computations are relatively easier to distribute. Since both effective Born radii and diagonal energy computations involve iterating through atom neighbors, the computation for each atom is more or less balanced. In addition, given that both host and Xeon Phi have the same compute power, the atoms can be equally distributed to the host and co-processor.

Diagonal energy computations are triangular, which means that more computations are required for the atoms at the start while the atoms at the end require fewer computations. Hence, the atoms cannot be equally distributed to host and Xeon Phi. Calculations proved that 70% of the atoms towards the end had the same number of computations as the 30% at the start. Hence, for diagonal energy, the computations for 70% of the atoms at the end are carried out on the Xeon Phi. Sending the atoms at the end has the added advantage that only the data of these 70% atoms need to be sent to Xeon Phi.

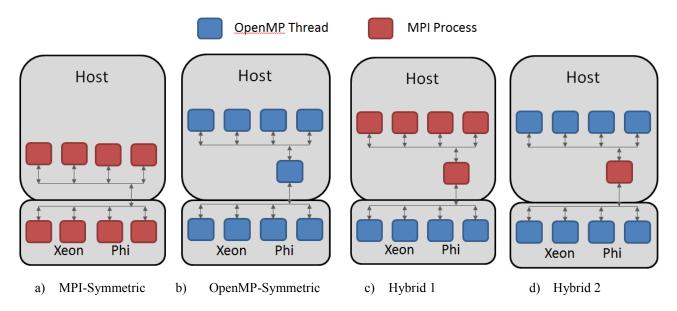

The next step was to choose which parallel programming technique to use on the host and Xeon Phi. To arrive at the decision, we tried the following approaches:

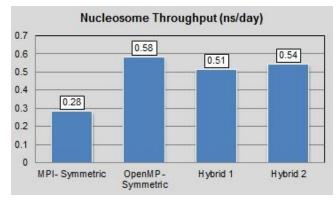

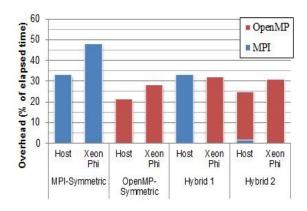

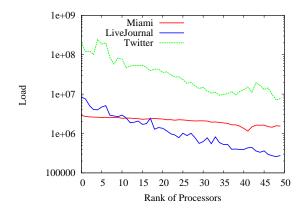

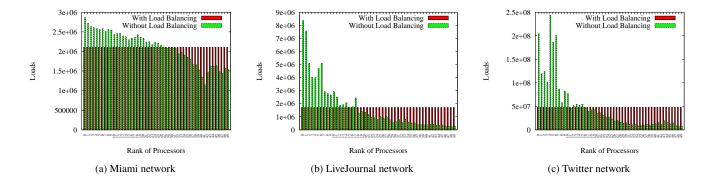

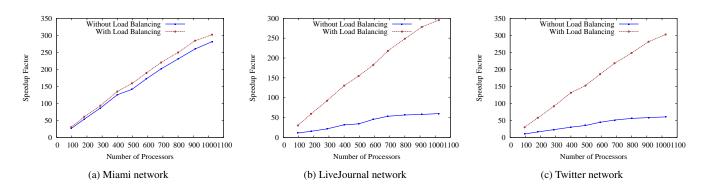

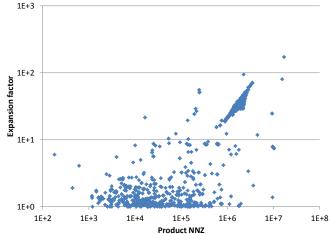

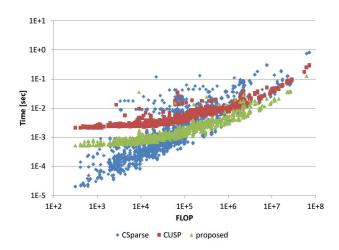

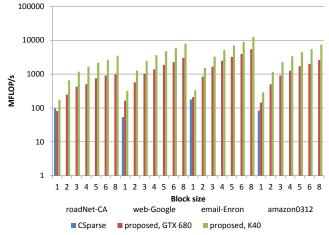

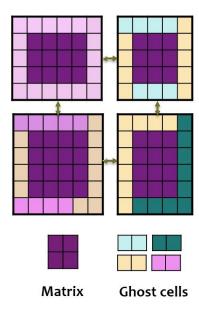

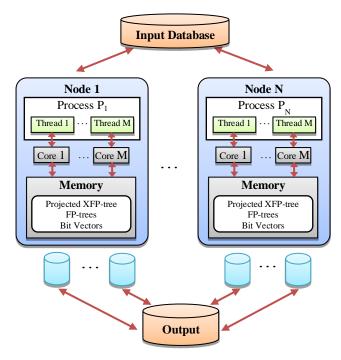

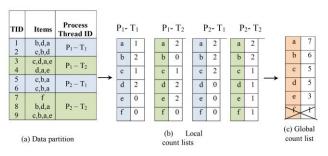

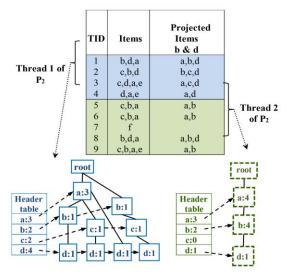

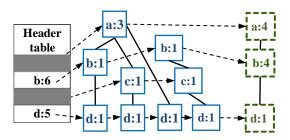

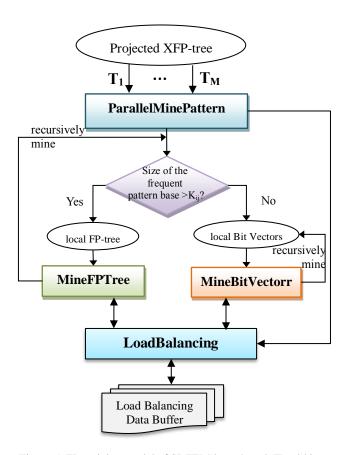

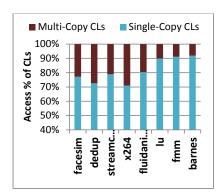

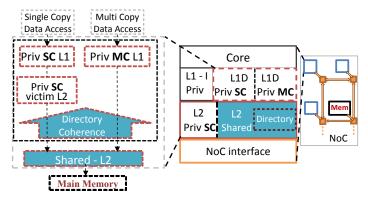

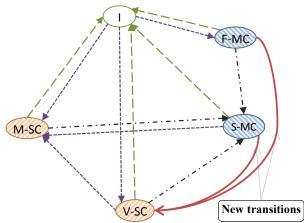

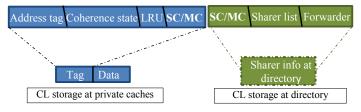

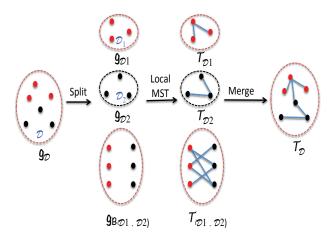

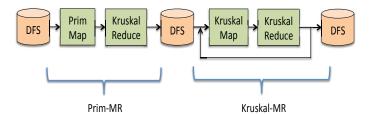

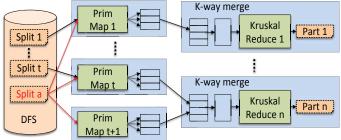

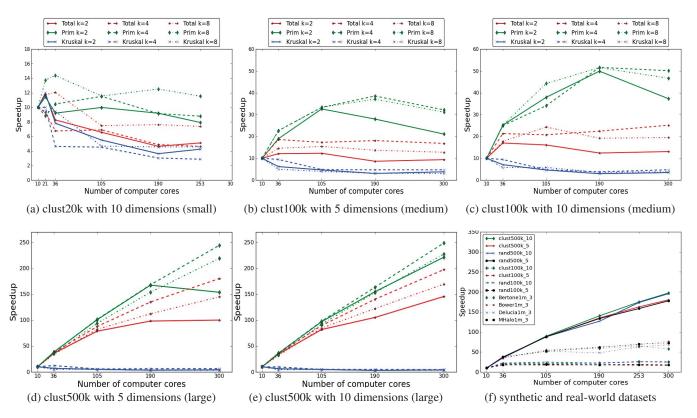

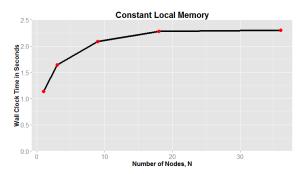

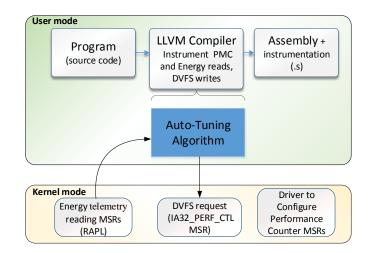

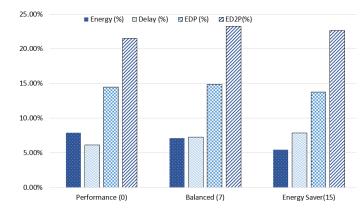

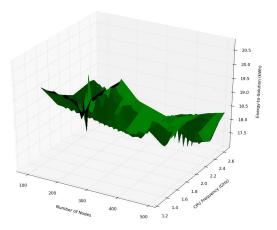

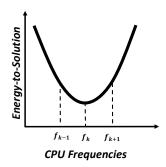

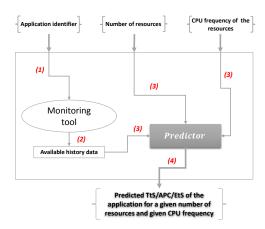

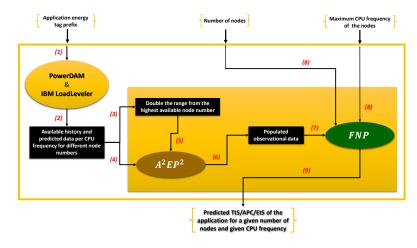

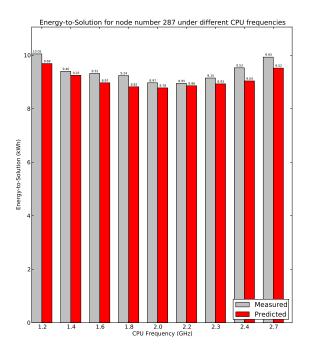

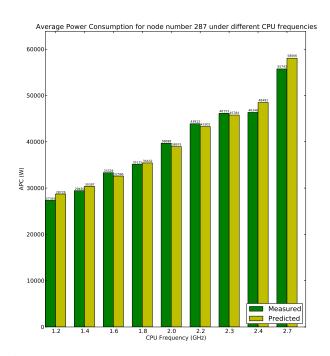

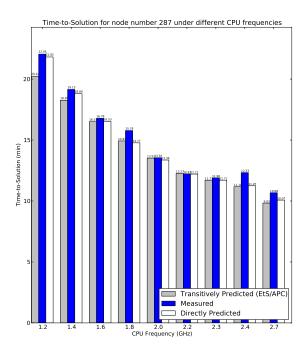

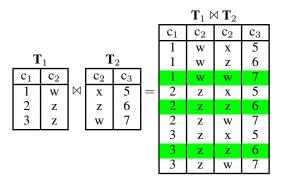

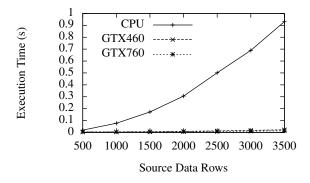

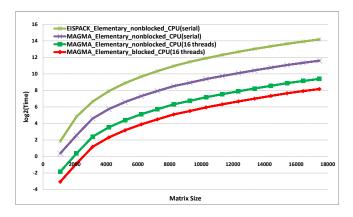

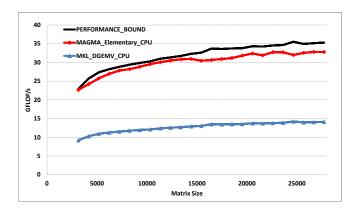

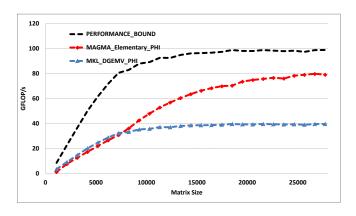

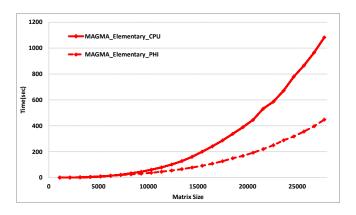

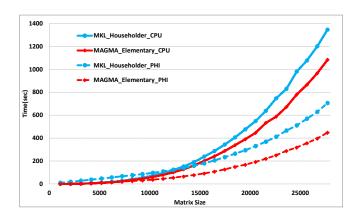

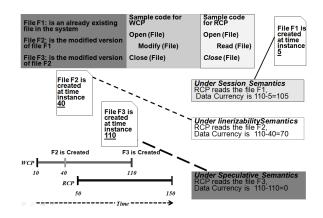

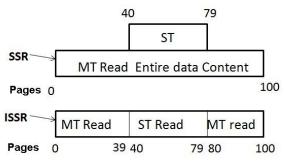

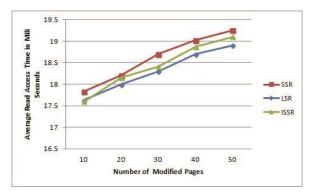

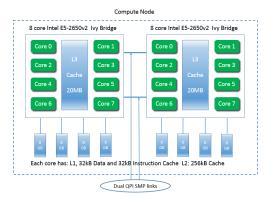

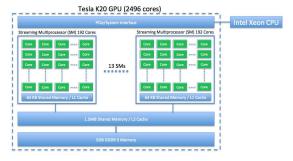

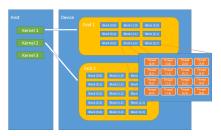

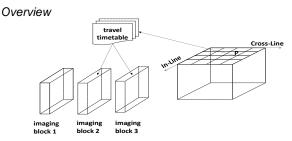

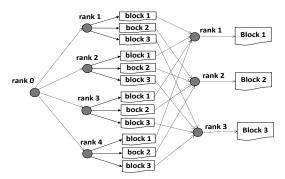

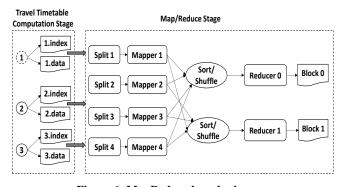

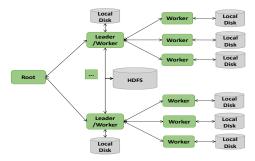

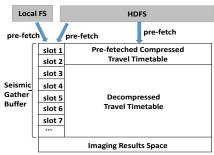

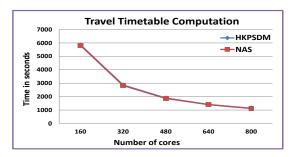

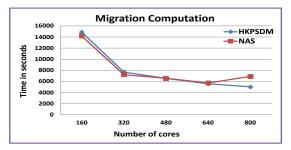

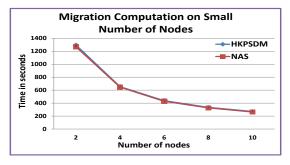

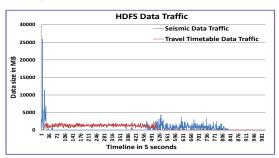

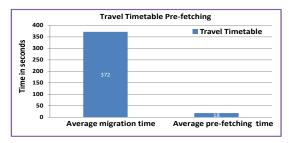

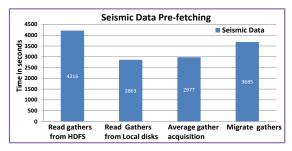

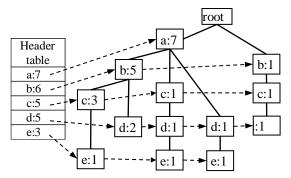

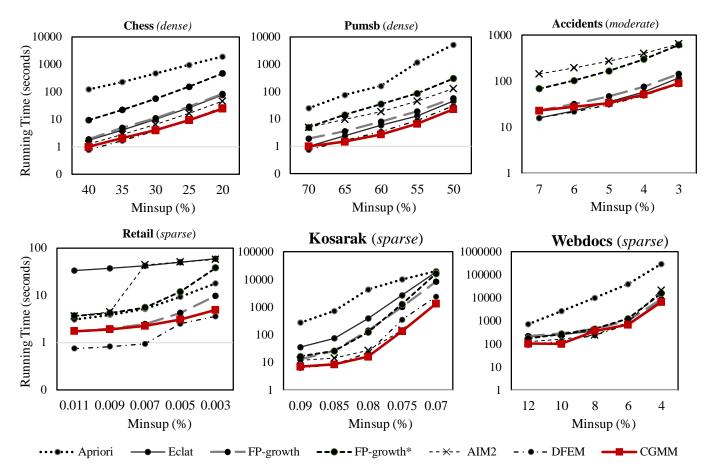

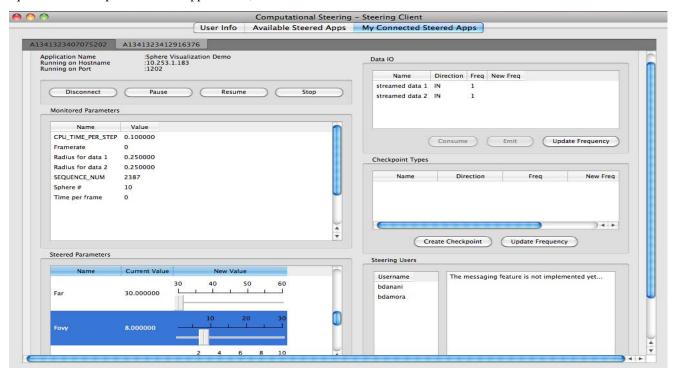

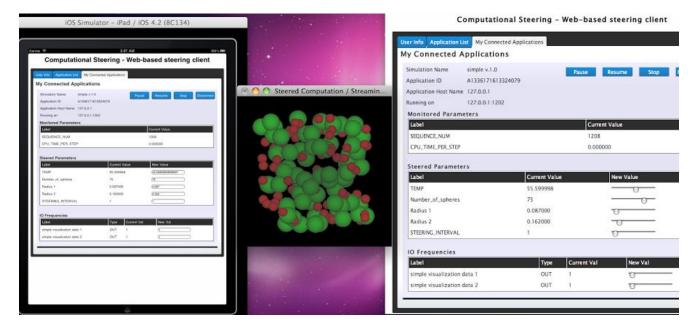

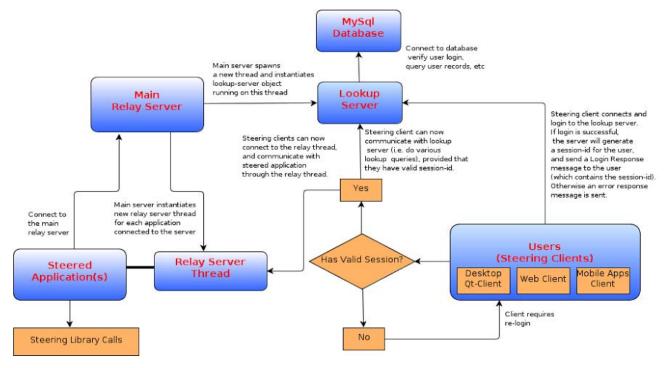

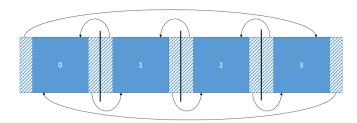

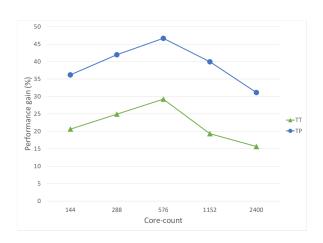

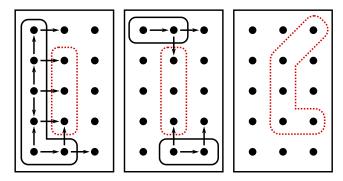

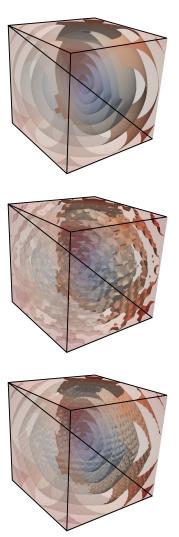

#### MPI - Symmetric