# Physical Modeling of Charge Trapping in 4H-SiC DMOSFET Technologies

Christian Schleich<sup>®</sup>, Dominic Waldhoer<sup>®</sup>, Katja Waschneck<sup>®</sup>, *Member, IEEE*, Maximilian W. Feil<sup>®</sup>, Hans Reisinger<sup>®</sup>, Tibor Grasser<sup>®</sup>, *Fellow, IEEE*, and Michael Waltl<sup>®</sup>, *Member, IEEE*

Abstract—Silicon carbide (SiC) MOSFETs still exhibit higher drifts of the threshold voltage than comparable silicon devices due to charge trapping, especially regarding small time scales. Understanding this behavior and the consequences in application relevant conditions is therefore of high research interest. Since charge trapping at different defects close to the SiC/SiO<sub>2</sub> interface and in the bulk oxide is strong bias and temperature-dependent, the phenomenon is referred to as bias temperature instability (BTI). It has been shown that drifts caused by BTI vary both in transient shape and magnitude for commercially available devices. These differences arise from defect densities and properties in the respective technologies. A physical model together with defect parameters that explain the charge transfer reactions at the defects is essential to understand all peculiarities of the transient degradation. In this work, we use a novel method to semiautomatically extract defect parameters within a two-state nonradiative multiphonon model framework. Our work reveals properties of defects responsible for shifts of the threshold voltage for both short-term ac and long-term dc stress conditions which are accurately reproduced for three different DMOS technologies. Our calibrated simulation framework is further used to extrapolate device degradation at operation relevant ac bias conditions to typical device lifetimes.

Index Terms—4H-SiC MOSFET, bias temperature instability (BTI), charge trapping, defects in SiC/SiO<sub>2</sub>, power switch.

## I. INTRODUCTION

THE continuous improvement of the SiC/SiO<sub>2</sub> interface has enabled the development of power MOSFETs which exploit the superior material properties of SiC as substrate

Manuscript received March 31, 2021; revised May 25, 2021; accepted June 20, 2021. Date of publication July 9, 2021; date of current version July 23, 2021. The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development and the Christian Doppler Research Association is gratefully acknowledged. The review of this article was arranged by Editor S.-M. Hong. (Corresponding author: Christian Schleich.)

Christian Schleich, Dominic Waldhoer, and Michael Waltl are with the Christian Doppler Laboratory for Single Defect Spectroscopy, Institute for Microelectronics, TU Wien, 1040 Vienna, Austria (e-mail: schleich@iue.tuwien.ac.at).

Katja Waschneck, Maximilian W. Feil, and Hans Reisinger are with Infineon Technologies AG, 85579 Neubiberg, Germany.

Tibor Grasser is with the Institute for Microelectronics, TU Wien, 1040 Vienna, Austria.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3092295.

Digital Object Identifier 10.1109/TED.2021.3092295

have led to the wide availability of commercial SiC power devices. A keystone for this progress has been the optimization of the post oxidation annealing (POA) processing step after oxide deposition, which has reduced the amount of electrically active defects in the vicinity of the conducting channel [1], [2]. Despite this improvement, SiC/SiO<sub>2</sub> MOSFETs still often exhibit increased shifts of the threshold voltage  $\Delta V_{\rm th}$  as compared to Si-based devices. Such  $V_{\rm th}$  drifts are due to charge trapping in the SiC/SiO<sub>2</sub> interfacial region and can be observed both on short and long time-scales in SiC MOSFETs [3], [4]. Since the amount of trapped charge leading to these instabilities strongly depends on bias and temperature, it is commonly referred to as bias temperature instability (BTI). Contrary to mature Si/SiO<sub>2</sub> MOSFET technologies, the resulting  $V_{th}$ shifts vary widely for SiC devices manufactured by different vendors as well as between consecutive device generations [5], [6]. The extraction of the temporal evolution of the  $\Delta V_{\text{th}}$  is typically performed at dc bias stress conditions at elevated temperatures, however, operation-relevant ac bias conditions can severely affect the degradation both in magnitude and transient shape of  $\Delta V_{\text{th}}$  [7], [8]. For device understanding and modeling, e.g., reproduction of the transfer characteristics, detailed knowledge of defect parameters and distributions is obligatory to account for and reproduce the transient charge capture and emission events. Typically, defects are accounted for by introducing normally distributed interface state densities  $D_{it}$ , which are dynamically occupied using the Shockley–Read–Hall (SRH) model or simple elastic tunneling models [9]. However, such a modeling approach does not account for structural transformations of the defect site upon the charge transfer reaction. A correct derivation of the charge transition times requires to account for this effect, as has been demonstrated extensively in Si technologies [10]. Recently the degradation of  $V_{\rm th}$  in SiC MOSFETs at dc bias temperature stress has been explained in detail by charge capture and emission in preexisting structural defects [11] employing a two-state nonradiative multiphonon (NMP) defect model [10], which does take structural relaxation of the defect site into account. This physical modeling approach has been shown to reproduce the  $\Delta V_{\text{th}}$  recovery peculiarities in large-area transistors over many decades in time. In this work, we extend this modeling approach to explain short-term ac stress and long-term dc stress consistently for three different DMOS technologies. To determine our defect distributions, we employ a recently developed Effective Single Defect Decomposition (ESiD) method [12], which allows us to extract physical defect parameters, as schematically shown in Fig. 1, efficiently and

material. Subsequent recent advances over a few generations

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

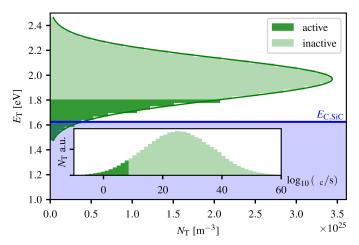

Fig. 1. For defect extraction based on an ESiD algorithm only defects that contribute to the  $\Delta \textit{V}_{th}$  response at the applied gate bias and temperature and fully reproduce the experimental observation in the simulation are considered. As shown schematically, this leads to a significant reduction of the total number of defects used in the simulation compared to the typically assumed Gaussian distributions. Only defects with reasonable capture and emission times  $\tau_{\text{C}},\tau_{\text{E}}$  (inset) are considered. The application of this method results in smaller effective defect densities and more physical trap levels  $\textit{E}_{\text{T}}$  and relaxation energies  $\textit{E}_{\text{R}}$ .

in a semiautomated manner to reproduce the experimental observation. We further compare the differences and similarities of the extracted defect parameters for the devices under test. In particular, the extracted defect parameters can be compared to such derived from *ab initio* studies of potential defect candidates. Our calibrated simulation framework is then used to extrapolate static bipolar ac stress to typical device lifetimes, which clearly reveals the superposition of electron and hole trapping at operation relevant bipolar bias conditions in SiC-based MOS technologies.

# II. EXPERIMENTAL

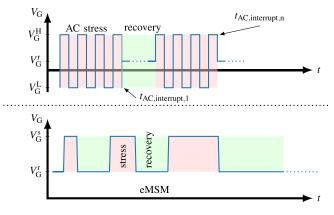

We compare three different planar DMOSFET technologies, two of which are subsequent generations of the same vendor (T1/G2, T1/G3) and the third (T2/G1) is the first generation of a different manufacturer. These Si-face channel SiC/SiO<sub>2</sub> DMOSFETs have similar nominal oxide thicknesses within a few nm, thus the applied stress voltages result in comparable oxide fields. In order to extract the long-term behavior of  $\Delta V_{th}$ at elevated stress gate biases and temperatures, typically constant voltage measure-stress-measure (MSM) sequences [14] are used as illustrated in Fig. 2. Our experiments cover stress times  $t_{\rm str}$  in the range of 100 ns to 10 ks at stress gate voltages up to 25 V. To calibrate short-term degradation at operating  $V_{\rm G}$ , we use data recorded by employing an adapted bipolar ac stress measurement [13], [15]. In this scheme, a short ac stress signal is applied for  $t_{\rm str} = 100 \, \rm ms$  repeatedly. Within the last ac cycle of the stress signal, the stress is interrupted at  $t_{\text{ac,interrupt}}$  and a  $\Delta V_{\text{th}}$  recovery trace is recorded for  $t_{\text{rec}} =$ 10 ms by forcing a fixed  $I_D = 1$  mA through the channel. The constant recovery current is achieved by employing a feedback loop of an operational amplifier circuit [16], which controls the gate voltage  $V_{\rm G}$  at fixed  $V_{\rm D}$ . A minimal measurement delay of  $t^{\text{read}} = 1.4 \,\mu\text{s}$  for recording  $V_{\text{G}}$  after stress can be reached with this setup. The measured  $V_G$  is compared to the initial value of the pristine device for the calculation of  $\Delta V_{th}$ . The interruption point within the ac cycle is altered after each stress phase to obtain short-term stress and recovery at multiple points of the

Fig. 2. Applied schemes to extract short-term ac  $\Delta V_{th}$  (top) and long-term dc PBTI degradation (bottom) are shown. Note that the short ac stress is repeatedly interrupted at different points of the ac cycle during the high/low ( $V_G^H/V_G^L$ ) phase, as indicated in the scheme. The shift of  $V_{th}$  is recorded during the recovery phase by enforcing a fixed  $I_D=1$  mA through the channel via controlling  $V_G$  with a feedback loop [13].

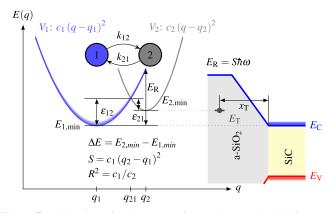

Fig. 3. Transition times for charge transfer reactions at single defects are calculated by employing the NMP model. The configuration coordinate diagram shows the harmonic approximation of the PES of the two defect states. In order to change the defect state, an energetic barrier  $\varepsilon_{12}$ ,  $\varepsilon_{21}$  has to be overcome. These barriers are computed from the intersection point of the two harmonic oscillators which change their relative position with gate bias.

ac stress signal. To capture the temperature activation of the charge trapping process all measurements have been conducted at temperatures  $T=25~^{\circ}\text{C}$  and 175  $^{\circ}\text{C}$ .

#### III. MODELING AND SIMULATION

Our 1-D BTI simulator Comphy [17], which employs a two-state defect model based on NMP theory [10], is calibrated to derive the surface potential from a given gate voltage  $V_{\rm G}$  from the doping concentration in the channel, the oxide thickness and the work-function difference of an ideal device. Subsequently it is used to calculate charge capture and emission events at preexisting defects in order to explain the observed transient  $\Delta V_{\rm th}$ . The charge transition times are given by [10]

$$\tau_{\rm c/e}^{-1} = n v_{\rm th} \vartheta_{\rm WKB} \sigma \exp\left(-\frac{\varepsilon_{12/21}}{k_{\rm B}T}\right) \tag{1}$$

with the electron concentration in the channel n, the thermal carrier velocity  $v_{\rm th}$ , a tunneling factor calculated by a Wentzel-Kramers-Brillouin (WKB) approximation  $\vartheta_{\rm WKB}$ , and a capture cross section  $\sigma$ , which was chosen constant

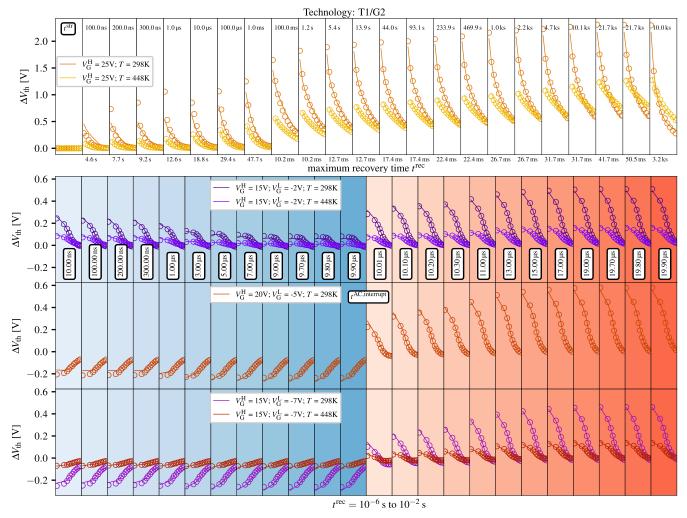

Fig. 4. Comparison of simulation (lines) and experimental  $V_{\text{th}}$  recovery (circles) of T1/G2 at long-term dc stress bias (top) with stress times  $t_{\text{str}} = 100$  ns to 10 ks and recovery times after each stress phase from  $t_{\text{rec}} = 1$   $\mu$ s up to maximum values shown in the horizontal axis. A detailed time resolution of dc traces is shown in Fig. 6. Bottom three figures show recovery traces for short-term ac stress (f = 50 kHz,  $t_{\text{str}} = 100$  ms) for different interruption times  $t_{\text{ac,interrupt}}$  during the ac cycle for different  $V_{\text{G}}^{\text{L}}$ ,  $V_{\text{G}}^{\text{H}}$ , and T. The simulations can accurately explain the recovery behavior for all applied stress conditions. The leftmost trace of the dc MSM sequence shows an initial readout phase of the pristine device with no stress applied. Note that a higher degradation at *lower* T, an effect unknown in Si technologies is observed in all three technologies and is shown in detail in Fig. 6.

at  $10^{-15}$  cm<sup>2</sup>. The capture- and emission barriers  $\varepsilon_{12}$  and  $\varepsilon_{21}$ are computed from the intersection points of two harmonic oscillators that approximate the potential energy surface (PES) of the two respective defect states, as shown in the configuration coordinate diagram in Fig. 3. Contrary to the frequently used SRH-like models, which are only suitable for describing interface defects without considerable structural relaxation of the defect site, this model accounts for the inelastic tunneling process arising from thermal relaxations due to coupling of the defect to a heat bath. Using this framework, it has been demonstrated for SiC MOSFETs that charge capture and emission at electron traps (conventional MSM) and hole traps (negative pulse MSM) can be accurately explained [11]. Typically, the experimental data are reproduced in the simulation by placing energetically normal and spatially uniform distributed defect bands with the parameters  $\langle E_{\rm T} \rangle$ ,  $\sigma_{E_{\rm T}}$ ,  $\langle E_{\rm R} \rangle$ ,  $\sigma_{E_{\rm R}}$ ,  $x_{\rm T}$ , and  $N_{\rm T}$ . These parameters have to be adapted and optimized by a minimization scheme for each defect band to match the measurement data. As mentioned, extraction of these defect parameter distributions is time-consuming, especially in the SiC/SiO<sub>2</sub> system with many potential defect bands present, and

a good initial guess for the defect parameters is required for this optimization method. To mitigate these challenges, in this work, we employ a novel Effective Single Defect Decomposition (ESiD) approach as presented in [12] to extract physical defect parameters in a semiautomated manner. In this method, the measurement signal is compared to the calculated response of defects within the gate insulator that are sampled across a predefined parameter grid. The measured  $\Delta V_{\text{th}}$  is therefore reproduced as the superposition of the linear response of the defect grid points with the coefficients proportional to the respective defect density  $N_{\rm T}$ . The least-square algorithm is applied to find the optimum weights,  $N_{\rm T}$ , respectively. Defect parameters which produce artificial high  $N_{\rm T}$  are further filtered out, until a maximum error criterion for the simulation signal deflection from the measurement signal is achieved. This optimization problem is further regularized with a Tikhonov scheme [18] in order to avoid artificial high defect densities as well as to ensure a smooth density distribution function. The decisive advantage of this method is that barely any assumption about the defect distribution has to be made, and so the calculation of defects with unrealistic high tran-

TABLE I GRID PARAMETERS

| Layer     | E <sub>T</sub> range  | $\Delta E_{\mathrm{T}}$ | E <sub>R</sub> range | $\Delta E_{ m R}$ | x <sub>T</sub> range | $\Delta x_{\rm T}$ |

|-----------|-----------------------|-------------------------|----------------------|-------------------|----------------------|--------------------|

| oxide     | -3-3 eV               | 50 meV                  | 0.1–5 eV             | 70 meV            | 0.6–3 nm             | 0.1 nm             |

| interface | $-2.2-2.2\mathrm{eV}$ | 34 meV                  | 0.1-3 eV             | 70 meV            | 0.0–0.5 nm           | 0.1 nm             |

The grid parameters have been chosen to account for different distributions of defect parameters in the vicinity of the interface and for bulk oxide.

TABLE II

FIXED OXIDE CHARGE

| Symbo            | ol   Quantity | T1/G2              | T1/G3                | T2/G1 | Unit               |

|------------------|---------------|--------------------|----------------------|-------|--------------------|

| $Q_{\mathrm{f}}$ | fixed Charge  | $2 \times 10^{11}$ | $1.4 \times 10^{12}$ | 0     | C cm <sup>-2</sup> |

Fixed oxide charge used for the individual technologies to model the device electrostatics at threshold voltage.

sition times is avoided, as schematically shown in Fig. 1. To further ensure physically meaningful defect distributions, different grid parameter spaces have been used as presented in Table I. The twofold parameter constraints represent two layers, one in the vicinity of the interface and one deeper in the oxide. This selection allows us to account for higher defect densities, as well as different defect parameters in the interface layer, which can be justified due to the different stoichiometric composition in the material transition region. Defect densities are uniformly distributed in spatial dimension  $(x_{\rm T})$  within the respective layers. Another major advantage of the ESiD method is that defect distributions can be extracted automatically from recorded  $V_{\rm th}$  shifts with little manual effort, which allows us to calibrate our model to a comprehensive input dataset in order to compare different technologies. To extrapolate  $\Delta V_{th}$  at bipolar ac bias conditions to typical device lifetimes of  $t = 1 \times 10^8 \,\mathrm{s}$  ( $\approx 10$  years) at given operating conditions, an analytical expression [19], [20] is used. As proposed by Ito et al. [21], a fixed charge  $Q_f$  has been placed at the interface to rebuild the pristine electrostatics, as shown in Table II. The introduction of fixed positive charges at the SiC/SiO<sub>2</sub> interface during device manufacturing is discussed in [22]. However, this charge is not accessible within our experimental T and  $V_G$  range.

#### IV. RESULTS AND DISCUSSION

## A. Simulation Results

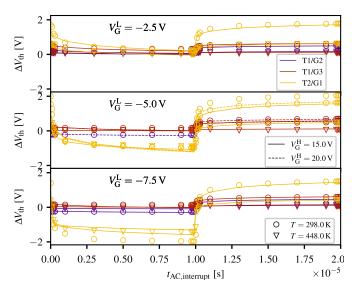

Our simulation framework has been calibrated simultaneously to both dc and short-term ac data for all three technologies. It accurately replicates the data considering a large variety of stress/recovery times and bias combinations at the two studied temperatures as is exemplary shown for T1/G2 in Fig. 4. Fig. 5 shows the first points of each recovery trace of the short-term ac stress measurement data compared with the simulation for all technologies. Note that T2/G1 shows the largest degradation for the applied stress conditions when the ac cycle is interrupted during the  $V_G^L$  and  $V_G^H$  phase and for long-term positive BTI (PBTI) stress, respectively. While T1/G2 shows more negative  $\Delta V_{\rm th}$  at more negative  $V_{\rm G}^{\rm L}$ , this behavior cannot be observed for T1/G3, which does not exhibit noticeable negative  $\Delta V_{\rm th}$  for any  $V_{\rm G}^{\rm L}$ . The observed maximum positive  $\Delta V_{\rm th}$  is comparable for both technologies. Quite interestingly, at 448 K a lower  $\Delta V_{\rm th}$  at recovery times smaller than 1 ms can be observed for all three technologies, which can be explained by the faster emission of captured negative charge during the recovery phase, while the degradation of

Fig. 5. First points of the measured **(symbols)** and simulated **(lines)** recovery trace after interruption of a short-term ac stress (duty cycle = 0.5, f = 50 kHz,  $t_{\rm str} = 100$  ms) at  $t_{\rm ac,interrupt}$  after start of an ac cycle are shown for varying  $V_{\rm G}^{\rm L}$  and  $V_{\rm G}^{\rm H}$ . The simulation can accurately reproduce all recovery  $\Delta V_{\rm th}$  for the shown stress conditions. The technology comparison reveals large  $\Delta V_{\rm th}$  for T2/G1 at both polarities, while T1/G3 exhibits no negative  $\Delta V_{\rm th}$  at more negative  $V_{\rm G}^{\rm L}$ .

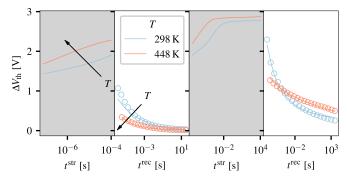

Fig. 6. Stress/recovery simulation is shown for T1/G2 after  $t_{\rm str}=100~\mu \rm s$  and  $t_{\rm str}=10~\rm ks$  together with the recovery measurement data. It can be seen that more defects can capture a charge at the higher T resulting in larger positive  $\Delta$   $V_{\rm th}$ , but at the same time most defects emit faster at elevated T, resulting in lower visible degradation during the recovery measurement. In the last recovery phase a turnover after  $t_{\rm rec}\approx 1~\rm ms$  is observed, in which the measured  $\Delta$   $V_{\rm th}$  becomes larger at the higher T.

$\Delta V_{\text{th}}$  during the stress phase is larger than at 298 K, compare Fig. 6.

## B. Defect Parameters

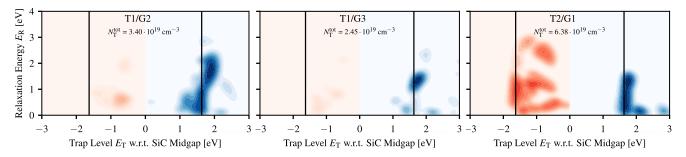

As shown in Fig. 7 by comparison of the relevant defect parameters ( $E_T$ , $E_R$ ), acceptor-like defects are necessary to describe the PBTI behavior which reside in the upper half of  $E_G$  in T1/G3. Additionally, donor-like defects in the lower half of the SiC bandgap are prevalent in T1/G2 and T2/G1 leading to visible negative BTI (NBTI) degradation. Also T2/G1 shows defect distributions with larger defect densities  $N_T$  in both halves of  $E_G$  and the donor-like defects are spread more widely in the energetic dimensions  $E_R$  and  $E_T$ , thereby exhibiting several peaks. Particularly noteworthy is that the relaxation energies  $E_R$  of the defects extracted for all three device generations are significantly lower compared to [11], which is a result of setting the curvature ratio between the two

Fig. 7. Extracted defect distributions for the different technologies are shown. While electrically active defects are present in T1/G2 in the lower half of the bandgap (left), their concentration is significantly lower for T1/G3 (center). T2/G1 (right) shows larger defect densities for both electron traps close to  $E_{\rm C}$  and hole traps spread widely over the lower half of  $E_{\rm G}$ . The relaxation energies show small values for both trap types, similarities are especially observed for acceptor-like defects close to  $E_{\rm C}$  across all technologies. The densities  $N_{\rm T}$  are normalized to the maximum total density of the respective technology and have been scaled by  $\log_{10}(1 + \kappa N_{\rm T}/N_{\rm T}^{\rm max})/\log_{10}(1 + \kappa)$  with  $\kappa = 10$  to visualize defects with smaller densities.

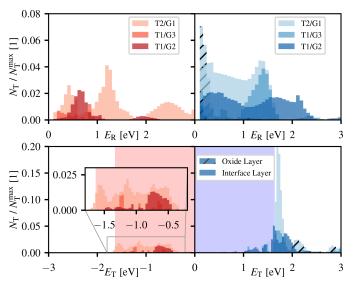

Fig. 8. Comparison of the extracted defects is shown. The distributions are normalized to  $N_{\rm T}=6.38\times10^{19}~{\rm cm}^{-3}$ , i.e., the largest extracted defect density for T2/G1. All technologies show a peak of  $N_{\rm T}$  close to  $E_{\rm C}$  (bottom, right). The majority of defects show low relaxation energies  $E_{\rm R}$  (top) and are located within 0.5 nm distance to the channel (hashed bars) and therefore assigned to the interface'. T1/G3 shows a negligible amount of defects in the lower half of the bandgap (bottom, left).

defect states R = 1. This selection is supported by ab initio calculations considering defect candidates in a-SiO<sub>2</sub> [23]. Note that a large fraction of the defects in all technologies show relatively low  $E_R$  values, which is not typically observed in Si technologies for oxide defects [12] but does apply for interface defects, such as P<sub>b</sub>-centers [24]. The majority of defects are spatially located within a small distance from the SiC/SiO<sub>2</sub> interface, which is confirmed by our simulations for all three cases, see Fig. 8 and in line with previous investigations [11]. Both observations support the hypothesis that the vast majority of structural defects is due to the  $SiO_xC_y$  transition layer between SiC and SiO<sub>2</sub> due to a stepped (off-axis cutting) interface [25], e.g., dangling bonds [26] with potentially low relaxation energies. Consistent among the studied technologies are acceptor-like defects with  $E_{\rm T}$  close to  $E_{\rm C}$  of SiC that lead to positive  $\Delta V_{\text{th}}$  when charged. The highest density among these defects is found in T2/G1, by a factor of two compared to T1/G2. A possible explanation could be that those defects a related to an enhanced density of N complexed defects, as suggested by electrically detected magnetic resonance (EDMR) measurements [27]. Also, a larger amount of N deposited at the

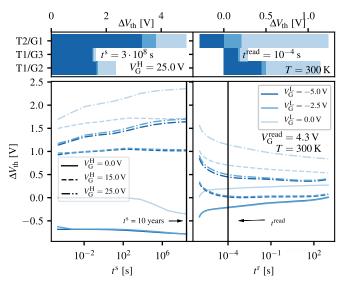

Fig. 9. (left) Extrapolation of bipolar ac stress by analytic calculation for T1/G2 is shown (bottom, left). At a device lifetime of  $t=3\times10^8$  s (10 years)  $\Delta V_{\text{th}}\approx 2$  V is reached for the applied operating conditions (duty cycle = 0.5, f=50 kHz). Simulated recovery traces (bottom, right) at constant initial  $V_{\text{th}}$  show the strong dependence of  $\Delta V_{\text{th}}$  measurements on the readout time. A comparison of the degradation of all three technologies after  $t_{\text{str}}=3\times10^8$  s and  $t^{\text{read}}=10^{-4}$  s is shown (top).

interface during POA employing N containing precursors has been correlated with a higher number of electron traps [28]. In all technologies also trap levels are extracted in the range of  $E_{\rm T}$  with respect to midgap of 2 to 3 eV with comparably low  $N_{\rm T}$ , which can most probably be assigned to bulk oxide defects [29]. The distributions of donor-like defects can be tentatively assigned to C complexed structures [30], which exhibit charge transition levels in the same energetic range based on ab-initio calculations.

# C. Extrapolation

The extrapolation of digital ac stress up to a maximum lifetime of 10 years as presented in Fig. 9 shows the strong dependence of the observed degradation on the bias combination  $(V_G^L, V_G^H)$  and on the readout time  $t^{\text{read}}$  of  $\Delta V_{\text{th}}$ . While comparable degradation can be observed for T1/G2 and T1/G3 during stress, the latter recovers faster and shows lower  $\Delta V_{\text{th}}$  at  $t^{\text{read}}$ . T1/G3 also shows the lowest variation in  $\Delta V_{\text{th}}$  both during stress and recovery for all bias combinations and is therefore extrapolated as the most stable device. T2/G1 shows a pronounced overall degradation, but comparably low readout

values for more negative  $V_{\rm G}^{\rm L}$  at the selected  $t^{\rm read}=100\,\mu{\rm s}$ , which is a result of the interplay of electron and hole trapping. All technologies show a decreased positive  $\Delta V_{\rm th}$  at a readout voltage of  $V_{\rm G}\approx V_{\rm th}$  for the most negative  $V_{\rm G}^{\rm L}$ , which is both due to hole capture in donor-like defects that compensate negative charge at the interface and pronounced electron emission in acceptor-like defects close to  $E_{\rm C}$ .

#### V. CONCLUSION

A wide range in  $V_{th}$  drifts can be observed for different SiC DMOSFET technologies and described with defect distributions that vary in both the energetic and spatial dimension, as well as their respective defect densities. The majority of the electrically active defects in these devices is located within a small distance to the interface and in the vicinity of  $E_{\rm C}$  and  $E_{\rm V}$  of SiC, respectively, which is clearly revealed by our simulations. Elimination of one defect component (e.g., donor-like traps) leads to unipolar degradation of  $V_{th}$  for bipolar stress as observed in T1/G3, and higher stability of  $V_{th}$  when extrapolating the device degradation. The diverse degradation behavior in all technologies and its peculiarities can be fully explained by charge trapping at oxide defects employing an NMP model. The wide range of defect distributions is presumably a result of the different interface quality. To identify the impact of process parameters (e.g., POA ambient), characterization and simulation after each manufacturing process step can be conducted with our approach. Finally, our lifetime extrapolation appears to be dominated by superposition of charge transitions in both acceptor- and donor-like defects at bipolar operating conditions, demonstrating that both electron and hole trapping has to be considered to consistently explain  $V_{th}$  shifts in SiC-based MOSFETs.

#### REFERENCES

- G. Y. Chung et al., "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 176–178, Apr. 2001, doi: 10.1109/55.915604.

- [2] J. Senzaki, T. Suzuki, A. Shimozato, K. Fukuda, K. Arai, and H. Okumura, "Significant improvement in reliability of thermal oxide on 4H-SiC (0001) face using ammonia post-oxidation annealing," *Mater. Sci. Forum*, vols. 645–648, pp. 685–688, Apr. 2010, doi: 10.4028/www.scientific.net/MSF.645-648.685.

- [3] A. J. Lelis, R. Green, D. B. Habersat, and M. El, "Basic mechanisms of threshold-voltage instability and implications for reliability testing of Sic MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 316–323, Feb. 2015, doi: 10.1109/TED.2014.2356172.

- [4] A. Ghosh et al., "Studies of bias temperature instabilities in 4H-SiC DMOSFETs," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2020, pp. 1–4, doi: 10.1109/IRPS45951.2020.9128318.

- [5] R. Green, A. Lelis, and D. Habersat, "Threshold-voltage bias-temperature instability in commercially-available Sic MOSFETs," *Jpn. J. Appl. Phys.*, vol. 55, no. 4S, Apr. 2016, Art. no. 04EA03, doi: 10.7567/jjap.55.04ea03.

- [6] T. Aichinger, G. Rescher, and G. Pobegen, "Threshold voltage peculiarities and bias temperature instabilities of Sic MOSFETs," *Microelectron. Rel.*, vol. 80, pp. 68–78, Jan. 2018, doi: 10.1016/j.microrel.2017.11.020.

- [7] M. Sometani et al., "Accurate evaluation of fast threshold voltage shift for SiC MOS devices under various gate bias stress conditions," *Jpn. J. Appl. Phys.*, vol. 57, no. 4S, 2018, Art. no. 04FA07, doi: 10.7567/jjap.57.04fa07.

- [8] H. Jiang, X. Zhong, G. Qiu, L. Tang, X. Qi, and L. Ran, "Dynamic gate stress induced threshold voltage drift of silicon carbide MOSFET," *IEEE Electron Device Lett.*, vol. 41, no. 9, pp. 1284–1287, Sep. 2020, doi: 10.1109/LED.2020.3007626.

- [9] A. J. Lelis, D. B. Habersat, R. Green, and N. Goldsman, "Two-way tunneling model of oxide trap charging and discharging in Sic MOSFETs," *Mater. Sci. Forum*, vols. 717–720, pp. 465–468, May 2012, doi: 10.4028/www.scientific.net/MSF.717-720.465.

- [10] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectron. Rel.*, vol. 52, no. 1, pp. 39–70, Jan. 2012, doi: 10.1016/j. microrel.2011.09.002.

- [11] C. Schleich et al., "Physical modeling of bias temperature instabilities in SiC MOSFETs," in *IEDM Tech. Dig.*, Dec. 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993446.

- [12] D. Waldhoer et al., "Towards automated defect extraction from bias temperature instability measurements (under submission)," IEEE Trans. Electron Devices, vol. 68, no. 8, 2021, doi: 10.1109/TED.2021.3091966.

- [13] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Understanding and modeling transient threshold voltage instabilities in Sic MOSFETs," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2018, pp. 1–10, doi: 10.1109/IRPS.2018.8353560.

[14] B. Kaczer *et al.*, "Ubiquitous relaxation in BTI stressing—New eval-

- [14] B. Kaczer et al., "Ubiquitous relaxation in BTI stressing—New evaluation and insights," in Proc. IEEE Int. Rel. Phys. Symp., Apr. 2008, pp. 20–27., doi: 10.1109/RELPHY.2008.4558858.

- [15] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Review on Sic MOSFETs high-voltage device reliability focusing on threshold voltage instability," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4604–4616, Nov. 2019, doi: 10.1109/TED.2019.2938262.

- [16] H. Reisinger, O. Blank, W. Heinrigs, A. Muhlhoff, W. Gustin, and C. Schlunder, "Analysis of NBTI degradation— and recovery-behavior based on ultra fast VT-measurements," in *Proc. IEEE Int. Rel. Phys.* Symp., Mar. 2006, pp. 448–453, doi: 10.1109/RELPHY.2006.251260.

- Symp., Mar. 2006, pp. 448–453, doi: 10.1109/RELPHY.2006.251260.

[17] G. Rzepa et al., "Comphy—A compact-physics framework for unified modeling of BTI," Microelectron. Rel., vol. 85, pp. 49–65, Jun. 2018, doi: 10.1016/j.microrel.2018.04.002.

- [18] A. N. Tikhonov, Numerical Methods for the Solution of Ill-Posed Problems. Dordrecht, The Netherlands: Springer, 1995, doi: 10.1007/978-94-015-8480-7.

- [19] K. Giering, C. Sohrmann, G. Rzepa, L. Heiss, T. Grasser, and R. Jancke, "NBTI modeling in analog circuits and its application to long-term aging simulations," in *Proc. IEEE Int. Integr. Rel. Workshop Final Rep. (IIRW)*, Oct. 2014, pp. 29–34., doi: 10.1109/IIRW.2014.7049501.

- Oct. 2014, pp. 29–34., doi: 10.1109/IIRW.2014.7049501.

[20] G. Rzepa, "Efficient physical modeling of bias temperature instability," Ph.D. dissertation, Inst. Microelectron., TU Wien, Vienna, Austria, 2018, p. E360. [Online] Available: http://www.ine.tuwien.ac.at/phd/rzepa/

- p. E360. [Online]. Available: http://www.iue.tuwien.ac.at/phd/rzepa/

[21] K. Ito, T. Kobayashi, and T. Kimoto, "Effect of quantum confinement on the defect-induced localized levels in 4H-SiC(0001)/SiO<sub>2</sub> systems," J. Appl. Phys., vol. 128, no. 9, Sep. 2020, Art. no. 095702, doi: 10.1063/5.0013240

- [22] G. Rescher, "Behavior of SiC-MOSFETs under temperature and voltage stress," Ph.D. dissertation, Inst. Microelectron., TU Wien, Vienna, Austria, 2018, p. E360. [Online]. Available: http://www.iue.tuwien.ac.at/phd/rescher/

- [23] W. Goes et al., "Identification of oxide defects in semiconductor devices: A systematic approach linking DFT to rate equations and experimental evidence," Microelectron. Rel., vol. 87, pp. 286–320, Aug. 2018, doi: 10.1016/j.microrel.2017.12.021.

- [24] B. Ruch, M. Jech, G. Pobegen, and T. Grasser, "Applicability of Shockley–Read–Hall theory for interface states," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 2092–2097, Apr. 2021, doi: 10.1109/TED.2021.3049760.

- [25] J. Woerle et al., "Two-dimensional defect mapping of the SiO<sub>2</sub>/4H SiC interface," Phys. Rev. Mater., vol. 3, no. 8, Aug. 2019, Art. no. 084602, doi: 10.1103/PhysRevMaterials.3.084602.

- [26] J. Cottom, G. Gruber, G. Pobegen, T. Aichinger, and A. L. Shluger, "Recombination defects at the 4H-SiC/SiO<sub>2</sub> interface investigated with electrically detected magnetic resonance and *ab initio* calculations," *J. Appl. Phys.*, vol. 124, no. 4, Jul. 2018, Art. no. 045302, doi: 10.1063/1.5024608.

- [27] E. Higa, M. Sometani, H. Hirai, H. Yano, S. Harada, and T. Umeda, "Electrically detected magnetic resonance study on interface defects at nitrided Si-face, a-face, and m-face 4H-SiC/SiO<sub>2</sub> interfaces," Appl. Phys. Lett., vol. 116, no. 17, Apr. 2020, Art. no. 171602, doi: 10.1063/5.0002944.

- [28] H. Yoshioka, T. Nakamura, and T. Kimoto, "Generation of very fast states by nitridation of the SiO<sub>2</sub>/SiC interface," J. Appl. Phys., vol. 112, no. 2, Jul. 2012, Art. no. 024520, doi: 10.1063/1.4740068.

- no. 2, Jul. 2012, Art. no. 024520, doi: 10.1063/1.4740068.

[29] A.-M. El-Sayed, M. B. Watkins, V. V. Afanas'ev, and A. L. Shluger, "Nature of intrinsic and extrinsic electron trapping in SiO<sub>2</sub>," *Phys. Rev. B, Condens. Matter*, vol. 89, no. 12, Mar. 2014, Art. no. 125201, doi: 10.1103/PhysRevB.89.125201.

- [30] F. Devynck, A. Alkauskas, P. Broqvist, and A. Pasquarello, "Charge transition levels of carbon-, oxygen-, and hydrogen-related defects at the SiC/SiO<sub>2</sub> interface through hybrid functionals," *Phys. Rev. B, Condens. Matter*, vol. 84, no. 23, Dec. 2011, Art. no. 235320, doi: 10.1103/PhysRevB.84.235320.