\$ SUPER

Contents lists available at ScienceDirect

# Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Crystalline insulators for scalable 2D nanoelectronics

Y.Y. Illarionov<sup>a,b</sup>, T. Knobloch<sup>a</sup>, T. Grasser<sup>a,\*</sup>

- <sup>a</sup> Institute for Microelectronics (TU Wien), Guβhausstraβe 27-29/E360, 1040 Vienna, Austria

- <sup>b</sup> Ioffe Institute, Polytechnicheskaya 26, 194021 St-Petersburg, Russia

#### ARTICLE INFO

The review of this paper was arranged by "Felice Crupi"

Keywords: 2D materials Crystalline insulators Transistors Miniaturization Fluorides Native oxides

#### ABSTRACT

Despite the breathtaking progress already achieved for electronic devices built from 2D materials, they are still far from exploiting their full theoretical performance potential. Many of these problems are due to the lack of suitable insulators which would go along with 2D materials as nicely as SiO<sub>2</sub> goes with Si. For instance, amorphous oxides known from Si technologies contain numerous defects which degrade the device performance and stability, and hBN is not suitable for nanoscale devices due to limited dielectric properties. Thus, we suggest that an intensive search of beyond-hBN layered 2D insulators and other crystalline insulators such as CaF<sub>2</sub>, other fluorides and native oxides is required for the further development of next-generation 2D nanoelectronics.

### 1. Introduction

For more than half a century, microelectronics has been driven by Moore's law, which predicts a doubling of the integration density every 18 months and thus exponential growth, which is highly beneficial for economical and performance reasons. Despite many premature claims that Moore's law is at an end, according to the IRDS [1] scaling will continue during the next decade. However, numerous challenges will have to be surmounted, many of them related to the fact that material scaling has reached atomic dimensions, particularly in the vertical direction. For instance, the mobility of silicon starts to deteriorate below 5 nm [2], which can be expected for other 3D materials. Thus, the IRDS lists layered 2D semiconductors as a promising option for ultra-scaled FETs and memory devices after 2028. In line with these requirements, several groups have reported FETs with graphene [3], silicene [4], black phosphorus [5] and transition metal dichalcogenides [6,7] exhibiting excellent transistor characteristics. Research efforts have been mostly focused on finding the best channel materials with the highest mobilities and decent bandgaps. Also, some attempts on circuit integration of MoS2 FETs have been undertaken [8].

However, 2D FETs also need suitable insulators to separate the controlling gate from the channel, which should be scalable and ideally go along with 2D semiconductors as nicely as SiO<sub>2</sub> goes with silicon. The lack of these insulators makes it complicated to fully exploit the predicted performance potential of 2D electronic devices, even despite the

breathtaking progress already achieved in this field. As a result, there is still no commercially competitive 2D transistor technology available today.

# 2. Results and discussion

The selection of suitable insulators for 2D nanoelectronics represents an enormous challenge. However, this problem is of key importance, since scaling of 2D semiconductors towards sub-10 nm channel lengths is only possible with gate insulators scalable down to sub-1 nm equivalent oxide thicknesses (EOT). In order to achieve competitive device performance, these insulators need to meet stringent requirements regarding (i) low gate leakage currents, (ii) low density of interface traps, (iii) low density of border insulator traps and (iv) high dielectric strength [9]. Thus, careful selection requires the analysis of available insulators with respect to these four criteria, which are valid for scalable FETs with 2D channels. As for other devices such as optoelectronics and sensors which do not require aggressive scaling, only the requirements on clean interfaces and low densities of border insulator defects are of key importance. This is because high mobility and stable operation under applied gate bias stress are still required for these devices.

Most widely used insulators for 2D electronic devices are amorphous 3D oxides known from Si technologies (SiO<sub>2</sub>, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>), while native 2D oxides (MO<sub>3</sub>, WO<sub>3</sub> and Bi<sub>2</sub>SeO<sub>5</sub>), layered 2D crystals (hBN, mica) and ionic 3D crystals (CaF<sub>2</sub> and other fluorides like SrF<sub>2</sub>, MgF<sub>2</sub>) have been

E-mail address: grasser@iue.tuwien.ac.at (T. Grasser).

https://doi.org/10.1016/j.sse.2021.108043

<sup>\*</sup> Corresponding author.

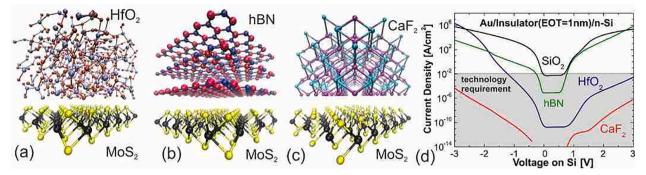

Fig. 1. Schematic structure of  $MoS_2/HFO_2(a)$ ,  $MoS_2/hBN$  (b) and  $MoS_2/CaF_2$  (c) interfaces. (d) Theoretical leakage currents through these insulators for EOT = 1 nm simulated using a simple WKB tunneling model [10].

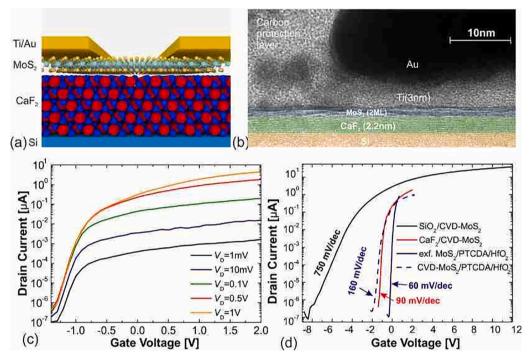

Fig. 2. (a) Schematic cross-section of the van der Waals interface of CaF<sub>2</sub>(111) and an MoS<sub>2</sub> channel in our FETs. (b) TEM image confirming the device structure. (c) Typical gate transfer characteristics of MoS<sub>2</sub> FETs with CaF<sub>2</sub> [18] and comparison with other MoS<sub>2</sub> FETs [19,20] (d).

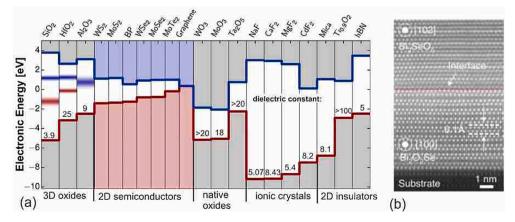

Fig. 3. (a) Band diagrams showing energetic alignments of different insulators relatively to most frequently used 2D semiconductors. For amorphous oxides defect bands are shown. (b) Atomically sharp interface between the 2D semiconductor Bi<sub>2</sub>O<sub>2</sub>Se and its native oxide Bi<sub>2</sub>SeO<sub>5</sub> [13].

also used or considered as promising candidates. However, 3D oxides form poor quality interfaces with 2D semiconductors (Fig. 1a), especially when grown in thin layers, and contain border traps which severely perturb stable device operation [11]. The latter is also valid for some native oxides such as MO<sub>3</sub> and WO<sub>3</sub>, which are non-stoichiometric [12]. As a result, they have a limited dielectric stability which makes it hard to use them in real devices. Nevertheless, other native oxides such as crystalline Bi<sub>2</sub>SeO<sub>5</sub> appear to be more promising and have been already applied in FETs [13], though still require an in-depth analysis of their dielectric properties. The layered 2D insulator hBN, on the other hand, forms excellent van der Waals interfaces with 2D semiconductors (Fig. 1b), but has mediocre dielectric properties ( $E_G = 6 \text{ eV}, \varepsilon < 5$ ) [14] which result in excessive leakage currents for sub-1 nm EOT. The potential of other 2D insulators is currently unclear, in part due to the absence of scalable growth techniques. For instance, only exfoliated flakes of mica have been used in FETs so far [15].

Thus, we suggest that for now the most promising insulators for 2D electronics are 3D ionic crystals like CaF2 which form well-defined interfaces (Fig. 1c). In contrast to hBN, fluorides have good dielectric properties (e.g.  $E_G = 12.1$  eV,  $\varepsilon = 8.43$  for CaF<sub>2</sub> [16]) and thus exhibit low gate leakage currents (Fig. 1d). Also, these insulators have excellent dielectric strength [17] and low density of border traps [18]. Furthermore, fluorides can be epitaxially grown on large-area wafers, thereby enabling fully integrated nanoelectronic devices. Also, careful preparation of Si substrates and the growth temperature of 250 °C lead to very homogeneous CaF<sub>2</sub> films [10,18]. Owing to this, excellent performance of MoS<sub>2</sub> FETs with record thin epitaxial CaF<sub>2</sub> of only 2 nm (0.9 nm EOT) [18] has been achieved recently (Fig. 2a,b), which is barely possible with any other insulator discussed above. Even though these are bare channel back-gated prototypes, they exhibit promising performance (Fig. 2c) such as on/off current ratio up to 10<sup>7</sup> and SS down to 90 mV/ dec while outperforming more mature MoS2 FETs with SiO2 [19] and top-gated devices with PTCDA/HfO2 [20] (Fig. 2d). Thus, further research on these insulators appears a very promising pathway for the development of scalable 2D FETs and other 2D devices with similar structure such as photodetectors and sensors.

We also note that despite all the open challenges, an interesting solution could be still offered by native oxides of 2D materials assuming that they are crystalline. However, it is important to consider that some of them have very narrow bandgaps as compared to conventional oxides and fluorides (Fig. 3a). Nevertheless, recently demonstrated crystalline Bi<sub>2</sub>SeO<sub>5</sub> [13] already offers top-gate integration, while forming an atomically sharp interface with its semiconductor Bi<sub>2</sub>O<sub>2</sub>Se (Fig. 3b).

While the estimated key dielectric parameters of this insulator are  $E_G$ = 3.9 eV and  $\varepsilon$  = 21, further research is required to understand if this narrow bandgap can enable reasonable band offsets with the channel to maintain low gate leakage currents for sub-1 nm EOT. Also, the potential of other insulators of this type should be explored in more detail.

### 3. Conclusions

In summary, 3D oxide insulators appear barely suitable for integration into 2D devices while hBN is not suitable for nanoscale FETs. Thus, an intensive search of beyond-hBN layered 2D insulators and further development of 2D devices with crystalline fluorides and native oxides appears promising for next-generation 2D nanoelectronics.

# **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

# Acknowledgements

The authors acknowledge the financial support through FWF grant

numbers I2606-N30, I4123-N30 and P29119-N35 and the FFG project no. 867414 (Take-Off program). Y.Y.I. also acknowledges the support by the Ministry of Science and Higher Education of the Russian Federation (project number 075-15-2020-790).

#### References

- [1] IEEE IRDS (Executive Summary), 2020.

- Schmidt M, et al. Solid-State Electron 2009;53:1246.

- [3] Guerriero E, et al. Sci Rep 2017;7:2419.

- [4] Tao L, et al. Nat Nanotechnol 2015;10:227.

- [5] Li L, et al. Nat Nanotechnol 2014;9:372.

- [6] Illarionov Y, et al. IEEE Electron Device Lett 2017;38:1763.

- [7] Cho Y, et al. Adv Funct Mater 2018;28:1801204.

- [8] Wachter S, et al. Nat Commun 2017;8:14948.

- [9] Illarionov Y, et al. Nat Commun 2020;11:3385.

- [10] Illarionov Y, et al. Tech Phys Lett 2010;36:404.

- [11] Illarionov Y, et al. 2D Mater 2016;3.

- [12] Yamamoto M, et al. Nano Lett 2015;15:2067.

- [13] Li T, et al. Nat Electron 2020;3:473.

- [14] Cassabois G, et al. Nat Photonics 2016;10:262.

- [15] Zou X, et al. Nanotechnology 2019;30.

- [16] Avouris P, et al. Appl Phys Lett 1989;55:1074.

- [17] Wen C, et al. Adv Mater 2020;32:2002525.

- [18] Illarionov Y, et al. Nat Electron 2019;2:230.

- [19] Illarionov Y, et al. IEEE Electron Device Lett 2017;38:1763.

- [20] Li W, et al. Nat Electron 2019;2:563.

Yury Illarionov was born in Leningrad (now St. Petersburg) in 1988. He received the B.Sc. and M.Sc. degrees from Peter the Great St. Petersburg Polytechnic University (Russia) in 2009 and 2011, respectively. In 2010 he was awarded with Erasmus Mundus scholarship and in 2012 he received a double M.Sc. from Grenoble INP (France) and University of Augsburg (Germany). In 2015 he received the Ph.D. degree from Ioffe Institute (Russia) and Dr.techn. degree from TU Wien (Austria). Currently Dr. Illarionov is a postdoc researcher at the Institute for Microelectronics (TU Wien) doing pioneering research on fully scalable 2D FETs. His most recent achievement is demonstration of MoS<sub>2</sub> FETs with record thin 2nm crystalline CaF2 insulators. He contributed to more than 75 research

works, including papers in Nature Electronics, Nature Communications, ACS Nano and Advanced Functional Materials among others. He also served as a committee member at IEEE IRPS 2020 and as a reviewer in numerous journals, including Nature Electronics, Advanced Functional Materials and 2D Materials

Theresia Knobloch was born in Vienna (Austria) in 1992. She received her BSc degree in Technical Physics and the degree of Diplomingenieur in Microelectronics from the Technische Universität Wien in 2014 and 2016, respectively. She joined the Institute for Microelectronics in April 2016, where she is currently working on her doctoral degree. Her current research topic are novel devices based on 2D materials. Recently she has published a paper in Nature Electronics and got Best Student Paper Award at the IEEE Device Research Conference (DRC).

Tibor Grasser is a professor of microelectronics reliability and an IEEE Fellow. He has been the head of the Institute for Microelectronics since 2016. He has edited various books, e.g. on advanced device modeling (World Scientific), the bias temperature instability (Springer) and hot carrier degradation (Springer), is a distinguished lecturer of the IEEE EDS, is a recipient of the Best and Outstanding Paper Awards at IRPS (2008, 2010, 2012, and 2014), IPFA (2013 and 2014), ESREF (2008) and the IEEE EDS Paul Rappaport Award (2011). He currently serves as an Associate Editor for the IEEE Transactions on Electron Devices following his assignment as Associate Editor for Microelectronics Reliability (Elsevier) and has been involved in various outstanding conferences such as

IEDM, IRPS, SISPAD, ESSDERC, and IIRW. Prof. Grasser's current research interests include theoretical modeling of performance aspects of 2D and 3D devices (charge trapping, reliability), starting from the ab initio level over more efficient quantum-mechanical descriptions up to TCAD modeling. The models developed in his group have been made available in the most important commercial TCAD environments.