Received 16 October 2020; revised 12 March 2021; accepted 12 March 2021. Date of publication 17 March 2021; date of current version 26 April 2021.

The review of this article was arranged by Editor A. Escobosa.

Digital Object Identifier 10.1109/JEDS.2021.3066679

# **Emerging CMOS Compatible Magnetic Memories and Logic**

JOHANNES ENDER<sup>®</sup> 1, SIMONE FIORENTINI<sup>®</sup> 1, ROBERTO L. DE ORIO<sup>®</sup> 2, WOLFGANG GOES<sup>3</sup>, VIKTOR SVERDLOV<sup>®</sup> 1, AND SIEGFRIED SELBERHERR<sup>®</sup> 2 (LIFE FELLOW, IEEE)

1 Christian Doppler Laboratory for Nonvolatile Magnetoresistive Memory and Logic, Institute for Microelectronics, TU Wien, 1040 Wien, Austria

2 Institute for Microelectronics, TU Wien, 1040 Wien, Austria

3 Silvaco Europe Ltd., Cambridge PE27 5JL, U.K.

CORRESPONDING AUTHOR: J. ENDER (e-mail: ender@iue.tuwien.ac.at)

This work was supported in part by Austrian Federal Ministry for Digital and Economic Affairs; in part by National Foundation for Research, Technology and Development; and in part by TU Wien Library through its Open Access Funding Program.

ABSTRACT As scaling of the feature size - the main driving force behind an outstanding increase of the performance of modern electronic circuits - displays signs of saturation, the main focus of engineering research in microelectronics shifts towards finding new paradigms. Any future solution must be scalable and energy efficient while delivering high performance, superior to that of CMOS-based circuits. In order to benefit from the outstanding potential of highly advanced silicon processing technology, any new solution must be CMOS compatible. Emerging nonvolatile memories, including magnetoresistive memories, satisfy the necessary requirements: purely electrical addressability, simple structure, high endurance and fast operation. In this work we present the recent developments in the research of spin-transfer torque and spin-orbit torque random access memories and give a brief overview of spin-based logic. Here, the advantages and challenges of these two main contenders in the magnetic memory field are described and the current technological trends are noted. Areas facing computational challenges due to the long-range interaction of the demagnetizing field are highlighted and an existing solution is presented. The use of reinforcement learning to optimize handling of a purely electrically controllable spin-orbit torque memory cell is introduced and first results showing the switching reliability of an optimized switching pulse sequence under thermal fluctuations are reported.

**INDEX TERMS** Digital spintronics, spin-transfer torque (STT), spin-orbit torque (SOT), magnetoresistive random access memory (MRAM), in-memory computing, reinforcement learning (RL).

### I. INTRODUCTION

The continuous miniaturization of metal-oxide-semiconductor field effect transistors is slowing down. Even though single devices with a gate length of a few nanometers were demonstrated [1], their control, reliability, fabrication costs, and the integration of several tens of billions of these devices results in an almost unbearable hurdle. In addition, a growing consumption of stand-by power due to increased leakages and dynamic power due to slow  $V_{\rm DD}$  scaling result in rapidly increasing heat generation.

An attractive path to mitigate the undesired trend of increasing power dissipation, especially at the stand-by mode, is to introduce nonvolatility in the circuits.

Nonvolatility is the ability to retain the data, when the power supply is turned off. Introduction of nonvolatility enables standby power-free integrated circuits. Apart from stand-alone applications as well as critical program and data storage devices, nonvolatility is particularly promising for use in the main computer memory as it eliminates the need for data refreshment cycles in conventional CMOS-based dynamic random-access memory (DRAM) [2]. In addition, if the memory is embedded on chip, it removes one of the bottlenecks of the Von Neumann computing architecture, namely the lengthy and energy consuming procedure of data exchange between memory and CPU. However, in order to compete with traditional memory circuits, including nonvolatile flash memory,

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

emerging nonvolatile memory circuits must offer fast switching time, high integration density supported by good scalability, long retention time, high endurance, and low power consumption. The circuits must also possess a simple structure to reduce fabrication costs. An important requirement is that emerging memories must be compatible with CMOS technology to benefit from the advantages provided by the well-developed CMOS fabrication technology.

CMOS operation is intrinsically based on the electron charge. As the downscaling of charge-based CMOS is saturating, another intrinsic characteristic of the electron, the electron spin, attracts attention as a possible candidate for complementing or even replacing the charge degree of freedom in future microelectronic devices [3], [4], [5]. The electron spin is characterized by the two possible spin projections on a reference axis and therefore possesses the property necessary for digital information. Indeed, magnetic hard disk drives (HDD) employ the electron spin or, to be more precise, the magnetization orientation to store the data. However, HDDs require magnetic fields created in magnetic heads in order to read and write the information. As they are not operated by electric currents, they are not CMOS compatible. In order to create a purely electrically manipulated magnetic memory, an efficient coupling between the electric current or field and the magnetization must be achieved. The discovery of the giant magnetoresistance (GMR) effect facilitated a reliable, purely electrical read operation of the information encoded in the magnetization orientation [6], [7]. The emerging generation of storage devices with even higher density is based on the unique properties of magnetic tunnel junctions (MTJs), sandwiches of two ferromagnetic layers separated by a thin tunnel barrier. The tunneling current through the MTJ structure strongly depends on the relative orientation of the magnetization in the ferromagnetic contacts. The difference in the MTJ resistivity reaches a factor of seven [8] in structures with in-plane magnetization and a factor of three [9] in MTJs with the magnetizations perpendicular to the layers, at room temperature. An efficient way of converting the magnetization orientation into an electrical resistance allows using MTJs for data storage. As the typical resistance of an MTJ is similar to the one of a MOSFET, no extra amplifiers are required for the converted signal. Thus, MTJ-based magnetoresistive random access memory (MRAM) is compatible with CMOS circuits.

In the following sections, an overview of the developments in research on spin-transfer torque MRAM as well as spin-orbit torque MRAM is given. Additionally, current research findings in the respective areas are presented and the topic of spin-based logic are discussed. This work is an extension to what was previously published in [10].

# II. SPIN-TRANSFER TORQUE MRAM

Although a very fast magnetization switching induced by magnetic fields has been achieved, MRAM writing induced by a magnetic field is not fully compatible with scaling. The magnetic field is generated by an electric current passing through write lines next to the cell. For downscaling, the wires' cross sections must be reduced, which makes higher current densities necessary to achieve the same field [11]. Therefore, a purely electrical way of MRAM information writing without magnetic field must be implemented.

The spin-transfer torque (STT) effect [12], [13] has been proven to be perfectly suited for purely electrical data writing. By passing a current through an MTJ, electrons become spin-polarized along the magnetization of the fixed layer. When they enter the free layer (FL), they become aligned with its magnetization almost immediately. Since the total angular momentum is conserved, the change in the electron spin is transferred to the magnetization, which results in a torque acting on the FL magnetization. If the current is strong enough to overcome the damping, this torque causes magnetization switching. STT-MRAM is considered a perfect candidate for future universal memory applications. It is fast (5ns), possesses high endurance (10<sup>12</sup>), and has a simple structure. It is compatible with CMOS technology and can be straightforwardly embedded in circuits [11]. It is particularly promising for stand-alone as well as for embedded applications as a replacement of conventional volatile CMOS-based and nonvolatile flash memory in Systems on Chip (SoC). For embedded applications, a successful implementation of 8Mb 1T-1MTJ STT-MRAM on a 28nm CMOS logic platform [14] was demonstrated. An embedded MRAM solution compatible with 22FFL FinFET Intel's technology is available [15].

Spin-transfer torque magnetoresistive random access memory (STT-MRAM) combines high speed, excellent endurance, and low costs. Recently, 1Gb stand-alone [15] and embedded STT-MRAM solutions [16] were reported. STT-MRAM is promising for applications ranging from Internet-of-Things to automotive applications [17], [18] and last level caches [19], [20], [21].

One critical aspect of the presently used STT-MRAM technology is a quite high switching current density, due to the fact that one has to overcome the energy barrier separating the two stable memory states. The barrier must be large - at least sixty times the thermal energy - to negate the errors due to undesired thermally agitated magnetization switching in big (1Gb) memory arrays at long (10 years) retention time. It turns out that in-plane magnetized structures the barrier which must be overcome at STT switching is higher than the thermal barrier. After the current is applied, the magnetization starts precessing around the magnetic easy axis. At the same time, while precessing, the magnetization deviates from one of its stable states further and further due to the STT. Therefore, during the switching process the magnetization gets out-of-plane. This demagnetization energy has to be expended in addition to the thermal barrier energy. As the system must be pushed over this large barrier by STT, the reduction of the switching current and the current density is challenging.

Several plausible approaches to address these issues are currently pursued. They include the use of composite free recording layers [23], decoupling the write and read current paths as discussed later, controlling magnetization by voltage, and employing new materials with improved properties and characteristics. However, replacement of the in-plane magnetization orientation in MTJs with perpendicular magnetization is the path adopted by industry.

In perpendicular MTJs (p-MTJ), the magnetization is already out-of-plane. The large demagnetizing energy penalty one has to pay while writing an in-plane structure does not exist for switching perpendicular structures. p-MTJs with the thermal barrier equal to the switching barrier allow to reduce the switching current. In addition, p-MTJs are better suited for high-density memory. A critical technological step was the discovery of an interface-induced perpendicular anisotropy at the CoFeB/MgO interface [23] with thin perpendicularly magnetized CoFeB layers.

In order to further reduce the switching current density and, at the same time, to preserve the large thermal barrier, one has to reduce the Gilbert damping and increase the spin current polarization. An interface-induced p-MTJ structure with a composite MgO/CoFeB/Ta/CoFeB/MgO free layer with two MgO interfaces [25] allows boosting the thermal barrier, while reducing the Gilbert damping. To scale the diameter of the MTJ below 10nm, the use of shape anisotropy was suggested [26]. It has been shown that the thermal stability can be increased for small diameters without sacrificing the tunneling magnetoresistance (TMR) and without any need for new materials, as FeB for the ferromagnetic free layer and MgO for the tunnel barrier were used.

A large TMR ratio is required for fast reliable reading in MRAM. In addition, the middle reference resistance to which the low and high resistance MTJ states are compared must be well separated from either of them. However, with downscaling it becomes increasingly difficult to control the bit-to-bit resistance. Resistance variation results in sacrificing the read error margin. Therefore, obtaining a large TMR is required to continue scaling the devices down.

Micromagnetic simulations can be used to investigate the influence of different materials or novel structures on the switching performance of the memory cells. The Landau-Lifshitz-Gilbert (LLG) equation is the central equation in micromagnetics, describing the magnetization dynamics in switching processes of MRAM devices [27], [28].

In case a finite element method (FEM) discretization is used, especially the computation of the demagnetizing field describing the long-range interaction poses a challenge which requires a careful computational treatment. A hybrid approach presented in [29] combines the FEM with the boundary element method (BEM) and thus enables a more efficient computation of the demagnetizing field. The demagnetizing field  $H_d$  is commonly described by the introduction of a scalar magnetic potential u:

$$\mathbf{H}_d = -\nabla u \tag{1}$$

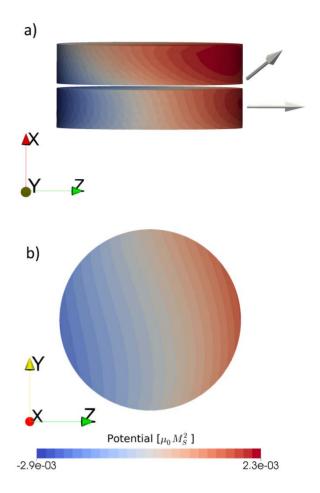

FIGURE 1. Magnetic potential in a two-layered, cylindrical structure showing interaction between layers due to the demagnetizing field. The structure is shown from the side (a) and from the top (b).

In the hybrid FEM-BEM approach, the basic ansatz is a splitting of this potential u in two parts  $u_1$  and  $u_2$  satisfying a Poisson and a Laplace equation with appropriate boundary conditions. The relation

$$u_2 = \int_{\partial\Omega} u_1 \frac{\partial}{\partial \mathbf{n}} \frac{1}{|\mathbf{x} - \mathbf{x}'|} d^2 \mathbf{x}$$

(2)

of the two partial potentials  $u_1$  and  $u_2$  in its discretized form results in the matrix-vector multiplication

$$u_2 = \mathbf{B} \cdot u_1 \tag{3}$$

which is used for evaluating  $u_2$  at the boundary. These values are used as Dirichlet boundary conditions for the Laplace equation.

In a micromagnetic simulation framework based on the open-source libraries MFEM [30] for FEM discretization and H2Lib [31] for basic BEM functionality, we implemented an algorithm for the calculation of the demagnetizing field of disjoint magnetic domains, as they appear in MTJs. This algorithm makes use of the hybrid FEM-BEM approach and allows for the incorporation of long-range interaction

458 VOLUME 9, 2021

between disjoint magnetic domains. For a multilayered structure (potentially) containing non-magnetic domains, first the surface mesh of the magnetic regions is extracted. The BEM library subsequently creates the discretized boundary operator B. As the boundary operator only depends on the structure of the device, this procedure has to be performed only once in the beginning of the simulation.

Fig. 1 shows the magnetic potential calculated for a multilayered structure with uniform magnetization in the two layers as indicated by the arrows in Fig. 1a. The magnetization in the upper layer is  $\mathbf{m}=(1,1,1)$ , while in the bottom layer it is =(0,0,1). If there were no interaction between the layers, the potential would vary linearly along the direction of the magnetization. The top view of the cylindrical structure in Fig. 1b shows how the potential is shifted towards the y-direction due to the interaction with the upper layer.

Advanced STT-MRAM is faster than flash memory and is suitable for last-level caches. However, STT-MRAM loses the power consumption competition to SRAM [21]. A new technological solution is thus required to use MRAM in higher level caches.

## **III. SPIN-ORBIT TORQUE MRAM**

Among the somewhat recently discovered physical phenomena suitable for next-generation MRAM is the spin-orbit torque (SOT) assisted switching of a ferromagnetic layer at room temperature in heavy metal/ferromagnetic [32] or topological insulator/ferromagnetic [33], [34] bilayers. In SOT-MRAM cells the MTJ's free layer is grown on a material with a large spin Hall angle/SOT. The SOT is generated by passing the current through this material. The switching current is injected in-plane along the heavy metal/ferromagnetic bilayer and, due to the spin Hall effect, creates a transverse spin current exerting a torque on the magnetization in the ferromagnetic free layer. Although the current density is quite large, the current does not flow through the MTJ. The high current is still a problem, and its reduction is the pressing issue for SOT-MRAM development. Topological insulators (TIs) are promising materials for reducing the switching current as they are characterized by a large efficiency of charge to spin conversion. The electrical conductivity of TIs, however, is usually too low for power-efficient applications. Recently, BiSe [32] and BiSb [34] TIs were reported as suitable candidates for emerging SOT-MRAM. They possess a charge to spin conversion efficiency of 18.8 and 52, respectively, and large conductivities allowing the reduction of the switching current by two orders of magnitude as compared to tungsten-based SOT-MRAM.

Despite the progress in developing and prototyping SOT-MRAM, there is one important issue which has not been convincingly resolved so far. Namely, a static magnetic field is still required to guarantee deterministic SOT switching of a perpendicularly magnetized free layer. In SOT-MRAM prototypes on 300 mm wafers an additional cobalt magnet was incorporated to provide such a field [35]. The external

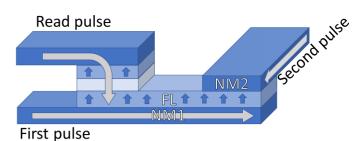

FIGURE 2. SOT MRAM cell for switching based on two orthogonal current pulses. The pulses are sent through the structure via two non-magnetic heavy metal wires, of which one is fully overlapping the FL (NM1) and one only partially (NM2).

magnetic field free approaches are based on cell mirror symmetry breaking [36] with respect to the plane formed by the normal vector to the free layer and the current direction. In this way, the two left and right in-plane magnetization orientations perpendicular to the current become non-equivalent, and the magnetization relaxes deterministically to the opposite stable states from these orientations. The symmetry can be perturbed by modifying the shape of the dielectric [37] or the free layer [38], by controlling the crystal symmetry of the metal layer [39], and by biasing the free layer via an exchange coupling to an antiferromagnet [40] or to an in-plane ferromagnet [41], [42], [43]. The latter experiments ignited the interest towards surprisingly little explored SOTs in ferromagnetic materials.

Approaches based on the breaking of the cell symmetry demand a considerable adaptation in the fabrication process and may compromise the large-scale integration of memory cells. Recently, a magnetic field free switching was reported in a structure of stacked heavy metal lines with opposite Hall angles [44]. This finding is exciting as the structure is compatible with a CMOS fabrication process. Another promising approach is based on a purely electrical dynamic way to induce the required magnetic field by means of two orthogonal current pulses [45]. In this approach, the part performing the writing of the memory cell consists of a perpendicularly magnetized free layer (FL) sandwiched between two orthogonal heavy metal wires (NM1 and NM2). The NM1 wire at the bottom of the FL is fully overlapping, while the NM2 wire on top only overlaps with a part of the FL (see Fig. 2). Previous publications have investigated the robustness of switching with two pulses with respect to fluctuations in the overlap/delay of the pulses and the corresponding influence on the switching speed [45], [46].

Machine learning (ML) is being increasingly applied in the realm of physics [47]. While the predominant amount of ML applications uses supervised learning approaches which require large amounts of data beforehand to train neural networks, the subbranch of reinforcement learning (RL) [48] has gained interest in recent years. Here, an agent interacts with an environment, trying to maximize the cumulative reward it receives from it based on a certain objective, like balancing an inverted pendulum for as long as possible. First

FIGURE 3. General setup of the reinforcement learning simulation: A simulation of the SOT MRAM cell acts as environment which an agent interacts with to build up a policy based on a neural network.

Observed State

**TABLE 1. State variables.**

| Variable                                                                            | Description                                           |

|-------------------------------------------------------------------------------------|-------------------------------------------------------|

| <m<sub>x&gt;, <m<sub>y&gt;, <m<sub>z&gt;</m<sub></m<sub></m<sub>                    | Average x/y/z-component of the magnetization          |

| $<\Delta m_x>$ , $<\Delta m_y>$ , $<\Delta m_z>$                                    | Difference of x/y/z component to previous iteration   |

| <H <sub>eff, x</sub> $>$ , $<$ H <sub>eff,y</sub> $>$ , $<$ H <sub>eff, z</sub> $>$ | Average x/y/z component of effective field            |

| Pulse1_settable, Pulse2_settable                                                    | Indicates whether pulse1/pulse2 is currently settable |

RL breakthroughs were achieved using games like chess or Go [48], but these types of algorithms have also successfully been applied in physics, e.g., [50], where strategies for quantum error correction are found through RL.

In order to simplify and automate the search for a faster switching scheme in the two-pulse switching approach, RL is a promising approach which is confirmed by first research findings.

Fig. 3 shows how the two-pulse switching of an SOT memory cell can be transferred into an RL setting. Two main components are needed: the agent and the environment. At the core of the environment is the simulation of the memory cell for which an in-house developed finite differences code is used [51]. The dimensions of the structure (Fig. 2) are  $40 \, \text{nm} \times 20 \, \text{nm}$  with a free layer thickness of 1.2 nm. The overlap of the NM2 wire is 50%. The simulation was adjusted in a way such that it can be controlled from the outside to change the state of the pulses and that it returns the current state of the simulation together with a reward after every iteration. The policy built up by the agent is approximated by a neural network.

The RL algorithm employed for finding faster switching schemes is the deep Q-network (DQN) algorithm [52]. A neural network is used in the DQN algorithm to approximate the so-called Q-function of the optimal policy, which assigns a quality estimate to every state-action pair:

$$O: S \times A \to \mathbb{R} \tag{4}$$

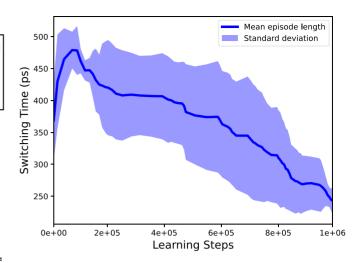

FIGURE 4. Learning curve showing the mean switching time over 6 independent runs performing 10<sup>6</sup> learning steps each.

Based on this estimate the agent selects its action.

In order to direct the algorithm to take actions such that the switching time is reduced, an appropriate scheme for rewarding the agent must be chosen. The current implementation of the learning algorithm returns a negative reward for every time step the memory cell has not yet switched, and once it has switched, i.e., the z-component has reached -0.5, a large positive reward is returned. The inherent working principle of RL algorithms is based on maximization of accumulative reward. A faster switching scheme thus leads to a less negative reward and in total to a larger accumulated reward. The description of the state returned from the environment every iteration consists of 11 variables described in Table 1. These variables are the basis for the learning algorithm to make its decisions for the next action. One needs to make sure that, based on the state information, it can be deduced which action is best to take. If for example the change of the average magnetization components was not included, by only knowing the current value of the components, it would not be clear in which direction the magnetization is moving at this point.

To simplify the learning process, the amount of possible actions has been restricted. The current setup of the experiment allows the agent to individually switch the two pulses on or off, with a minimum pulse width of 100 picoseconds for each pulse. The amplitude of the two pulses was fixed to 130  $\mu$ A for the first pulse (NM1) and 100  $\mu$ A for the second pulse (NM2). A learning episode was considered finished once the z-component of the magnetization reached -0.5.

Fig. 4 shows the learning curve of the performed experiment. The plot shows the mean switching time over the course of the learning period. After an initial increase in switching time, the agent improves its policy and can switch the memory cell faster with a final mean value of around 250 picoseconds. Single runs were able to arrive at an even better policy, which resulted in a switching time of 145 picoseconds. The learned policy of the agent switches

460 VOLUME 9, 2021

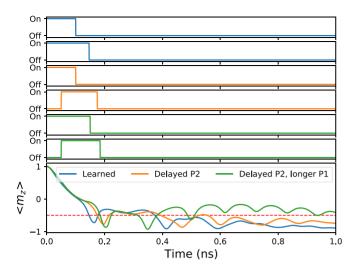

FIGURE 5. Comparison of the best switching scheme found by the RL algorithm with a pulse sequence where the second pulse is slightly delayed and a sequence where the first pulse is applied slightly longer and the second pulse is again delayed.

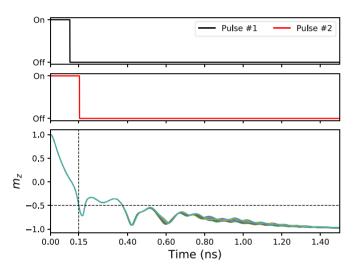

FIGURE 6. The upper two plots show the pulses in the way they were applied. The lower plot shows the z-component of the magnetization of 50 realizations using the switching scheme found by the RL algorithm. The horizontal dashed line indicates the value of the average magnetization at which the cell is considered to be switched. The vertical dashed line indicates the corresponding time at which switching has occurred.

both pulses on, right in the beginning. The first pulse is switched off after 100 picoseconds, while the second pulse stays on until it achieves the requirements given to the RL algorithm, to switch the z-component to -0.5 as fast as possible. When -0.5 is reached, the second pulse is turned off, as shown in Fig. 5. Comparing the best scheme with two slightly adapted pulse sequences (Fig. 5), one can see that, indeed, switching both pulses on right in the beginning leads to the fastest time to reach -0.5 under the given conditions.

In order to evaluate the reliability of the pulse sequence, simulations of 50 realizations were performed. A random thermal field at 300K was considered for these simulations. The results are shown in Fig. 6. The variation between the

realizations is very small and the magnetization is switching indeed reliably. With this RL approach, further experiments are also conceivable. Whereas in the current setup, the current values of the pulses could not be varied by the algorithm, by adding this degree of freedom, the objective for the algorithm could likely be set to finding the most energy efficient switching scheme. Thus, one can see that by using the assistance of machine learning approaches, tedious manual work can be outsourced to algorithms which can easily cope with large amounts of data and find hidden correlations and working principles.

### **IV. SPIN-BASED LOGIC**

The introduction of nonvolatility in CMOS circuits reduces the power consumption by half, with an outstanding 90% reduction for specific logic-in-memory circuits [53]. Placing the actual computation into the nonvolatile domain results in a non-conventional in-memory computing architecture. Any two MTJ-based cells can perform the conditional switching of a target MTJ depending on the state of the source MTJ, an operation called material implication (IMP). IMP completed with the FALSE operation covers the whole space of all Boolean operations. A compact IMP-based full adder realization involving only six 1T-1MTJ cells and 27 subsequent FALSE and IMP operations can be realized [54]. Recently, a massively parallel NOT operation based on the IMP implementation was proposed [55].

Another option for non-volatile computing is to proceed along a more conventional path with memory and computing units separated. Both elements are implemented in the magnetic domain and are nonvolatile. The idea of combining MTJs with a common free layer enables the realization of a nonvolatile magnetic flip-flop [56]. The processing unit consists of an STT-based nonvolatile majority gate and nonvolatile magnetic flip-flops used as memory registers in an entirely nonvolatile processing environment [56]. Recently, a substantial progress in fabricating such devices was reported [57].

The availability of high-capacity nonvolatile memory enables new logic-in-memory and computing-in-memory architectures for future artificial intelligence and cognitive computing. Nonvolatile MTJs are suitable for neural network realizations as they can be considered a current-driven programmable resistor, a memristor. MTJ-based neural networks featuring nonvolatile synapses allow for high-speed pattern recognition with a reduction in gate count of about 70% and a 99% improvement in speed as compared to their CMOS counterparts [53]. All-spin binary neuromorphic computing systems with probabilistic inference and online learning can enable a new generation of state-compressed and low-power computing platforms [58]. Neuromorphic computing is becoming a reality, with the first self-learning chips already in production.

### V. CONCLUSION

We are witnessing the beginning of nonvolatile MRAM entering into the stand-alone and, especially, embedded

memory market, as all major foundries announced the start of production of embedded STT-MRAM based on advanced silicon-on-insulator FinFET technology nodes. It will likely result in an exponential expansion of the MRAM market with a momentous impact on information storage and processing in the near future. In addition, a successful adoption of nonvolatility in microelectronic circuits and systems by developing various logic-in-memory and in-memory processing architectures promises a disruptive impact on cloud computing and edge applications by introducing new concepts in ultralow-power high-performance computing. Furthermore, it has been shown that modern ubiquitous technologies, like machine learning, do not only benefit from the development of application-specific chips, but the development and control of the underlying circuits themselves can take advantage from learning algorithms.

### REFERENCES

- [1] B. Doris et al., "Extreme scaling with ultra-thin Si channel MOSFETS," in Int. Electron Devices Meeting (IEDM)

Conf. Dig., San Francisco, CA, USA, 2020, pp. 267–270,

doi: 10.1109/IEDM.2002.1175829.

- [2] H. Ohno, M. D. Stiles, and B. Dieny, "Scanning the issue," Proc. IEEE, vol. 104, no. 10, pp. 1782–1786, Oct. 2016, doi: 10.1109/JPROC.2016.2601163.

- [3] I. Žutić, J. Fabian, and S. D. Sarma, "Spintronics: Fundamentals and applications," *Rev. Mod. Phys.*, vol. 76, pp. 323–410, Apr. 2004, doi: 10.1103/RevModPhys.76.323.

- [4] R. Jansen, "Silicon spintronics," Nat. Mat., vol. 11, pp. 400–408, Apr. 2012, doi: 10.1038/nmat3293.

- [5] V. Sverdlov and S. Selberherr, "Silicon spintronics: Progress and challenges," *Phys. Rep.*, vol. 585, pp. 1–40, Jul. 2015, doi: 10.1016/j.physrep.2015.05.002.

- [6] A. Fert, "Nobel lecture: Origin, development, and future of spin-tronics," Rev. Mod. Phys., vol. 80, pp. 1517–1530, Dec. 2008, doi: 10.1103/RevModPhys.80.1517.

- [7] P. A. Grünberg, "Nobel lecture: From spin waves to giant magnetoresistance and beyond," *Rev. Mod. Phys.*, vol. 80, pp. 1531–1540, Dec. 2008, doi: 10.1103/RevModPhys.80.1531.

- [8] S. Ikeda et al., "Tunneling magnetoresistance of 604% at 300K by suppression of Ta diffusion in CoFeB/MgO/CoFeB pseudo-spin-valves annealed at high temperature," Appl. Phys. Lett., vol. 93, Aug. 2008, Art. no. 082508, doi: 10.1063/1.2976435.

- [9] W. Skowroński et al., "Understanding stability diagram of perpendicular magnetic tunnel junctions," Sci. Rep., vol. 7, Aug. 2017, Art. no. 10172, doi: 10.1038/s41598-017-10706-2.

- [10] V. Sverdlov, S. Fiorentini, J. Ender, W. Goes, R. L. de Orio, and S. Selberherr, "Emerging CMOS compatible magnetic memories and logic," in *Proc. IEEE Latin Amer. Electron Devices Conf. (LAEDC)*, San José, Costa Rica, 2020, pp. 1–4, doi: 10.1109/LAEDC49063.2020.9073332.

- [11] D. Apalkov, B. Dieny, and J. M. Slaughter, "Magnetoresistive random access memory," *Proc. IEEE*, vol. 104, no. 10, pp. 1796–1830, Oct. 2016, doi: 10.1109/JPROC.2016.2590142.

- [12] J. C. Slonczewski, "Current-driven excitation of magnetic multilayers," J. Magn. Magn. Mater., vol. 159, pp. L1–L7, Jun. 1996, doi: 10.1016/0304-8853(96)00062-5.

- [13] L. Berger, "Emission of spin waves by a magnetic multilayer traversed by a current," *Phys. Rev. B*, vol. 54, pp. 9353–9358, Oct. 1996, doi: 10.1103/PhysRevB.54.9353.

- [14] Y. J. Song et al., "Highly functional and reliable 8Mb STT-MRAM embedded in 28nm logic," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2016, pp. 663–666, doi: 10.1109/IEDM.2016.7838491

- [15] O. Golonzka et al., "MRAM as embedded non-volatile memory solution for 22FFL FinFET technology," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 412–415, doi: 10.1109/IEDM.2018.8614620.

- [16] S. Aggarwal et al., "Demonstration of a reliable 1 Gb standalone spintransfer torque MRAM for industrial applications," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993516.

- [17] K. Lee et al., "1Gbit high density embedded STT-MRAM in 28nm FDSOI technology," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993551.

- [18] V. B. Naik et al., "Manufacturable 22nm FD-SOI embedded MRAM technology for industrial-grade MCU and IOT applications," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993454.

- [19] W. J. Gallagher et al., "22nm STT-MRAM for reflow and automotive uses with high yield, reliability, and magnetic immunity and with performance and shielding options," in Proc. IEEE Int. Electron Devices Meeting (IEDM), 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993604.

- [20] G. Hu et al., "Spin-transfer torque MRAM with reliable 2 ns writing for last level cache applications," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993604.

- [21] S. Sakhare et al., "Enablement of STT-MRAM as last level cache for the high performance computing domain at the 5nm node," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 420–423, doi: 10.1109/IEDM.2018.8614637.

- [22] J. G. Alzate et al., "2 MB array-level demonstration of STT-MRAM process and performance towards L4 cache applications," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2019, pp. 1–4, doi: 10.1109/IEDM19573.2019.8993474.

- [23] A. Makarov, T. Windbacher, V. Sverdlov, and S. Selberherr, "CMOS-compatible spintronic devices: A review," Semicond. Sci. Technol., vol. 31, Oct. 2016, Art. no. 113006, doi: 10.1088/0268-1242/31/11/113006.

- [24] S. Ikeda et al., "A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction," Nat. Mater., vol. 9, pp. 721–724, Jul. 2010, doi: 10.1038/nmat2804.

- [25] H. Sato, M. Yamanouchi, S. Ikeda, S. Fukami, F. Matsukura, and H. Ohno, "MgO/CoFeB/Ta/CoFeB/MgO recording structure in magnetic tunnel junctions with perpendicular easy axis," *IEEE Trans. Magn.*, vol. 49, no. 7, pp. 4437–4440, Jul. 2013, doi: 10.1109/TMAG.2013.2251326.

- [26] K. Watanabe, B. Jinnai, S. Fukami, H. Sato, and H. Ohno, "Shape anisotropy revisited in single-digit nanometer magnetic tunnel junctions," *Nat. Commun.*, vol. 9, p. 663, Feb. 2018, doi: 10.1038/s41467-018-03003-7.

- [27] J. C. Slonczewski, "Currents, torques, and polarization factors in magnetic tunnel junctions," *Phys. Rev. B*, vol. 71, Jan. 2005, Art. no. 024411, doi: 10.1103/PhysRevB.71.024411.

- [28] S. Lepadatu, "Unified treatment of spin torques using a coupled magnetisation dynamics and three-dimensional spin current solver," Sci. Rep., vol. 7, Oct. 2017, Art. no. 12937, doi: 10.1038/s41598-017-13181-x.

- [29] D. R. Fredkin and T. R. Koehler, "Hybrid method for computing demagnetizing fields," *IEEE Trans. Magn.*, vol. 26, no. 2, pp. 415–417, Mar. 1990.

- [30] T. Kolev and V. Dobrev. (2020). MFEM: Modular Finite Element Methods Library. [Online]. Available: http://mfem.org

- [31] N. Albrecht, C. Börst, D. Boysen, S. Christophersen, and S. Börm. (2016). H2Lib. [Online]. Available: http://www.h2lib.org

- [32] S.-W. Lee and K.-J. Lee, "Emerging three-terminal magnetic memory devices," *Proc. IEEE*, vol. 104, no. 10, pp. 1831–1843, Oct. 2016, doi: 10.1109/JPROC.2016.2543782.

- [33] D. C. Mahendr *et al.*, "Room-temperature high spin–orbit torque due to quantum confinement in sputtered  $\text{Bi}_x\text{Se}_{(1--x)}$  films," *Nat. Mater.*, vol. 17, pp. 800–807, Jul. 2018, doi: 10.1038/s41563-018-0136-z.

- [34] N. H. D. Khang, Y. Ueda, and P. N. Hai, "A conductive topological insulator with large spin hall effect for ultralow power spin–orbit torque switching," *Nat. Mater.*, vol. 17, pp. 808–813, Jul. 2018, doi: 10.1038/s41563-018-0137-y.

- [35] K. Garello et al., "Manufacturable 300mm platform solution for field-free switching SOT-MRAM," in Proc. Symp. VLSI Circuits, Kyoto, Japan, Jun. 2019, pp. T194–T195, doi: 10.23919/VLSIC.2019.8778100.

462 VOLUME 9, 2021

- [36] K. L. Wang et al., "Electric-field control of spin-orbit interaction for low-power spintronics," Proc. IEEE, vol. 104, no. 10, pp. 1974–2008, Oct. 2016, doi: 10.1109/JPROC.2016.2573836.

- [37] G. Yu et al., "Switching of perpendicular magnetization by spin-orbit torques in the absence of external magnetic fields," Nat. Nanotechnol., vol. 9, pp. 548–554, May 2014, doi: 10.1038/nnano.2014.94.

- [38] G. Yu et al., "Current-driven perpendicular magnetization switching in Ta/CoFeB/[TaO<sub>x</sub> or MgO/TaO<sub>x</sub>] films with lateral structural asymmetry," Appl. Phys. Lett., vol. 105, Sep. 2014, Art. no. 102411, doi: 10.1063/1.4895735.

- [39] D. MacNeill, G. M. Stiehl, M. H. D. Guimaraes, R. A. Buhrman, J. Park, and D. C. Ralph, "Control of spin-orbit torques through crystal symmetry in WTe<sub>2</sub>/ferromagnet bilayers," *Nat. Phys.*, vol. 13, pp. 300–305, Nov. 2017, doi: 10.1038/nphys3933.

- [40] S. Fukami, C. Zhang, S. DuttaGupta, A. Kurenkov, and H. Ohno, "Magnetization switching by spin-orbit torque in an antiferromagnet-ferromagnet bilayer system," *Nat. Mater.*, vol. 15, pp. 535–541, Feb. 2016, doi: 10.1038/nmat4566.

- [41] S. Łazarski et al., "Field-free spin-orbit-torque switching in Co/Pt/Co multilayer with mixed magnetic anisotropies," Phys. Rev. Appl., vol. 12, Jul. 2019, Art. no. 014006, doi: 10.1103/PhysRevApplied.12.014006.

- [42] S.-H. C. Baek et al., "Spin currents and spin-orbit torques in ferromagnetic trilayers," Nat. Mater., vol. 17, pp. 509–513, Mar. 2018, doi: 10.1038/s41563-018-0041-5.

- [43] H. Wu et al., "Spin-orbit torque from a ferromagnetic metal," Phys. Rev. B, vol. 99, May 2019, Art. no. 184403, doi: 10.1103/PhysRevB.99.184403.

- [44] Q. Ma, Y. Li, D. B. Gopman, Y. P. Kabanov, R. D. Shull, and C. L. Chien, "Switching a perpendicular ferromagnetic layer by competing spin currents," *Phys. Rev. Lett.*, vol. 120, Mar. 2018, Art. no. 117703, doi: 10.1103/PhysRevLett.120.117703.

- [45] R. L. de Orio, A. Makarov, W. Goes, J. Ender, S. Fiorentini, and V. Sverdlov, "Two-pulse magnetic field-free switching scheme for perpendicular SOT-MRAM with a symmetric square free layer," *Physica B, Condes. Matter*, vol. 578, Oct. 2019, Art. no. 411743, doi: 10.1016/j.physb.2019.411743.

- [46] R. L. de Orio et al., "Robust magnetic field-free switching of a perpendicularly magnetized free layer for SOT-MRAM," Solid-State Electron., vol. 168, Jun. 2020, Art. no. 107730, doi: 10.1016/j.sse.2019.107730.

- [47] P. Mehta et al., "A high-bias, low-variance introduction to machine learning for physicists," Phys. Rep., vol. 810, pp. 1–124, May 2019, doi: 10.1016/j.physrep.2019.03.001.

- [48] R. S. Sutton and A. G. Barto, Reinforcement Learning: An Introduction. Cambridge, MA, USA: MIT Press, 1998.

- [49] D. Silver et al., "A general reinforcement learning algorithm that masters chess, shogi, and Go through self-play," Science, vol. 362, no. 6419, pp. 1140–1144, Dec. 2018, doi: 10.1126/science.aar6404.

- [50] T. Fösel, P. Tighineanu, T. Weiss, and F. Marquardt, "Reinforcement learning with neural networks for quantum feedback," *Phys. Rev. X*, vol. 8, no. 3, Sep. 2018, Art. no. 031084, doi: 10.1103/PhysRevX.8.031084.

- [51] A. Makarov, "Modeling of emerging resistive switching based memory cells," Ph.D. dissertation, Dept. Inst. Microelectron., Vienna Univ. Technol., Vienna, Austria, 2014, doi: 10.13140/RG.2.2.11456.74242.

- [52] V. Mnih et al., "Human-level control through deep reinforcement learning," Nature, vol. 518, no. 7540, pp. 529–533, Feb. 2015, doi: 10.1038/nature14236.

- [53] T. Hanyu *et al.*, "Standby-power-free integrated circuits using MTJ-based VLSI computing," *Proc. IEEE*, vol. 104, no. 10, pp. 1844–1863, Oct. 2016, doi: 10.1109/JPROC.2016.2574939.

- [54] H. Mahmoudi, T. Windbacher, V. Sverdlov, and S. Selberherr, "Implication logic gates using spin-transfer-torque-operated magnetic tunnel junctions for intrinsic logic-in-memory," *Solid-State Electron.*, vol. 84, pp. 191–197, Jun. 2013, doi: 10.1016/j.sse.2013.02.017.

- [55] A. Jaiswal, A. Agrawal, and K. Roy, "In-situ, in-memory stateful vector logic operations based on voltage controlled magnetic anisotropy," *Sci. Rep.*, vol. 8, p. 5738, Apr. 2018, doi: 10.1038/s41598-018-23886-2.

- [56] T. Windbacher, A. Makarov, V. Sverdlov, and S. Selberherr, "A universal nonvolatile processing environment," in *Future Trends in Microelectronics—Journey into the Unknown*, S. Luryi, J. Xu, and A. Zaslavsky, Eds. Hoboken, NJ, USA: Wiley, Sep. 2016, pp. 83–91, doi: 10.1002/9781119069225.ch1-6.

- [57] E. Raymenants et al., "Scaled spintronic logic device based on domain wall motion in magnetically interconnected tunnel junctions," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 843–846, doi: 10.1109/IEDM.2018.8614587.

- [58] A. Sengupta, G. Srinivasan, D. Roy, and K. Roy, "Stochastic inference and learning enabled by magnetic tunnel junctions," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2018, pp. 360–363, doi: 10.1109/IEDM.2018.8614616.