#### RESEARCH ARTICLE

WILEY

# Impact of negative bias temperature instability on single event transients in scaled logic circuits

## Ambika Prasad Shah<sup>1,2</sup>

<sup>1</sup>Electrical Engineering Department, Indian Institute of Technology Jammu, Jammu, J&K, India

<sup>2</sup>CDL for SDS at the Institute for Microelectronics, TU Wien, Vienna, Austria

#### Correspondence

Michael Waltl, CDL for SDS at the Institute for Microelectronics, TU Wien, Vienna, 1040, Austria. Email: waltl@iue.tuwien.ac.at

[Correction added on 20 January 2021, after first online publication: corrected email address of Michael Waltl.]

#### **Abstract**

Altering the performance of single transistors and integrated circuits at nominal operating conditions over time, as well as soft errors, are serious reliability issues for integrated CMOS circuits, especially when used in space applications. In principle, the effect of soft errors becomes even more critical if the circuit performance degrades over time. To address this detrimental behavior, the impact of performance degradation due to NBTI on the soft error susceptibility of integrated circuits is analyzed thoroughly. For this, we analyze the critical charge sensitivity of the two-input NAND gate and NOR gate for different operating temperatures at stress times up to 3 years. The results show that the critical charge decreases with the temperature and strongly depends on the input states. Next, we validate the results employing the c17 ISCAS'85 benchmark suite, employing the PTM model with the HSPICE to estimate the soft error at the sensitive nodes. The critical charge is observed to be sensitive to the selected supply voltage and device temperature and thus provides a good measure for the soft error susceptibility with respect to NBTI at various operation conditions.

#### **KEYWORDS**

circuit simulation, ISCAS'85 benchmark circuit, NBTI, reliability, soft error

#### 1 | INTRODUCTION

With the scaling of CMOS technology toward only tens of nanometer small transistors, variability between seemingly identical transistors, and reliability challenges of single transistors have become more and more important for the performance and lifetime of integrated circuits.<sup>1</sup> In this context, negative bias temperature instabilities (NBTI) and positive BTI (PBTI) play an important role for NMOS and PMOS transistors and have been the subject of many experimental and theoretical studies.<sup>2,3</sup> Many of the experiments reveal that NBTI in PMOS transistors is much more dominant compared to PBTI in NMOS transistors. Thus, the NBTI/PMOS case is typically studied and considered to be primarily responsible for the lifetime of CMOS circuits.<sup>4,5</sup>

In more detail, NBTI refers to the case when a negative stress bias (negative  $V_{\rm gs}$ ) is applied which can trigger the creation of so-called interface states and oxide defects, which lead to a drift of the threshold voltage, reduction of the sub-threshold slope, and a reduction of the on-current. When the gate stress has released the shift of the threshold voltage accumulated during the stress phase partially recovers. The threshold voltage shift which remains after a large recovery period of the device has elapsed is considered the permanent degradation which can also slightly increase from

This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

© 2021 The Authors. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields published by John Wiley & Sons Ltd.

one stress cycle to the next stress cycle. This permanent shift of the threshold voltage is particularly disadvantageous for CMOS circuits, as it can introduce some uncertainty in the device and circuit behavior and can lead to a decrease of the device/circuit lifetime. Note that NBTI is the dominant device degradation mechanism at low drain biases. At high drain bias, the so called hot-carrier degradation becomes more dominant and seriously affects the device behavior. 9.9

Along with susceptibility to NBTI, nanoscale devices are more sensitive to radiation-induced errors, which also aggravates the noise immunity of the circuits. Also, the recent technology generation operates at low supply voltages which can, on one hand, reduce the circuit node capacitances, but on the other hand increase the probability of soft errors. Overall the scaled feature sizes, the lowered operating voltage, and the higher operating frequencies in combination with reduced noise margins give rise to an increased soft error rate occurring in integrated circuits. Also,

In addition, the susceptibility to soft errors can become even worse when single event transients (SETs) are considered in such advanced nodes. Such SETs can be caused by strikes from highly energetic particles, like cosmic neutrons on a sensitive region of the semiconductor device, which can affect the circuit performance. For example, when particles strike the silicon substrate, they can create secondary electron-hole pairs that can be collected by surrounding pn-junctions and so influence the device behavior. The alpha particles are emitted mostly due to the radioactive decay of uranium and thorium impurities in the chip packaging. As the alpha particle passes through the semiconductor device, electrons a dislodged from the crystal lattice sites along the track of the alpha particle. The critical charge is the minimum charge required to flip the logic. Next to SETs, the strikes may lead to single event upsets (SEUs) where both can hamper the proper functioning of the circuit, and lead to soft errors. The direct ionization by protons may cause SEU in devices with low critical charge ( $Q_{crit}$ ).

The aforementioned SEU is the most common type for a single event effect (SEE) occurring in storage elements (latches and memory cells), which can lead to a flip of the logic state of a circuits' output. In combinational circuits, SEUs can be induced as an additional current which is injected at selected nodes and then propagates through the logic elements and can give rise to soft errors.<sup>27</sup>

In this work, we evaluate the effect of NBTI in combination with the soft error radiation hardening enhancement of integrated CMOS circuits. To this end, firstly the soft error analysis of a two-input NAND gate is performed at different operating temperatures and a total stress time of up to 3 years. Furthermore, we compute and compare the critical charge of the circuit nodes to evaluate the worst-case input combination which is maximum susceptible to soft errors. Subsequently, the sensitivity of the radiation hardening of the two-input NAND gate is evaluated using the soft error rate ratio (SERR). The worst-case input combination is then identified and used for further analysis. To this extend, we further implement the c17 benchmark circuit from the ISCAS'85 suite<sup>28</sup> and focus on the node which propagates a possible SET directly to the output of the circuit. Further, we analyze the critical charge variation of the c17 circuit with the stress time for the case when the maximum number of PMOS transistors stressed.

## 2 | RADIATION HARDENING ANALYSIS METHODOLOGY

To study the performance of circuits considering device aging due to NBTI, we apply the PTM model calibrated to a 32 nm CMOS technology node. For stress analysis and aging evaluation, we used the HSPICE MOSRA model and perform all simulations at a supply voltage  $V_{\rm dd} = 0.9$  V. The operating temperature is set to T = 125°C, which leads to an acceleration of the aging effects. We have considered the DC stress for analyzing the aging effects in the circuits.

To inject SEU into the simulations, the induced current is modeled by a double exponential current source<sup>31</sup> specified by

$$I_{\rm inj}(t) = \frac{Q_{\rm inj}}{\tau_f - \tau_r} \times \left( e^{-t/\tau_f} - e^{-t/\tau_r} \right) \tag{1}$$

or alternatively by

$$I_{\text{inj}}(t) = I_{\text{peak}} \times \left( e^{-t/\tau_f} - e^{-t/\tau_r} \right) \tag{2}$$

where  $Q_{\rm inj}$  is the total amount of charge deposited at the sensitive node in fC, and  $I_{\rm peak}$  is the peak value of the current source in  $\mu A$ . The parameters  $\tau_f$  and  $\tau_r$  are material dependent parameters and are set to  $\tau_r = 1$  ps and  $\tau_f = 50$  ps according to Ref. 32.

To further calculate  $Q_{\rm crit}$  (in fC), we determine the minimum magnitude and duration of the injected current pulse that is required to flip the state of a logic output. In that way,  $Q_{\rm crit}$  is determined by integrating over the current pulse and can be given as

$$Q_{\text{crit}} = \int_{0}^{T_{\text{crit}}} I_{\text{inj}}(t)dt \tag{3}$$

where  $I_{ini}(t)$  is the injected current pulse injected at the node considered for the SEU analysis.

## 2.1 | Soft error rate (SER)

In principle, a soft error can occur in any digital circuit when enough charge is externally induced that this can lead to a change of the logic value of the respective circuit node. In this work, the SER of a circuit is analyzed considering combinational circuits like the two-input NAND gate and can be evaluated from its  $Q_{crit}$ . The SER depends exponentially on  $Q_{crit}$  and it is found that a larger value of  $Q_{crit}$  directly translates into lower SER.<sup>33</sup> Thus, the SER can be expressed as.<sup>34</sup>

$$SER \propto N_{\rm flux} A e^{-\frac{Q_{\rm crit}}{Q_{\rm S}}}$$

(4)

where  $N_{\rm flux}$  is the neutron flux intensity in particles/(cm<sup>2</sup> × s), A is the cross-section area of the sensitive node in cm<sup>2</sup>, and  $Q_{\rm S}$  is the charge collection efficiency of the device in fC.<sup>35</sup> From the above equation, it is obvious that a small increase in  $Q_{\rm crit}$  will significantly reduce the SER.

For the validation of soft error enhancement of the two-input NAND gate for different input combinations, the soft error rate ratio (SERR) is introduced. The SERR is calculated by assuming only  $Q_{crit}$  being affected by NBTI stress

$$SERR = \frac{SER_{Unstressed}}{SER_{Stressed}} \bigg|_{@T} = \frac{SER_{0Year}}{SER_{3Years}} \bigg|_{@T}.$$

(5)

In terms of the critical charge, the SERR is given by

SERR

$$\approx \text{antilog}_e \left[ Q_{\text{crit}}^{3\text{Years}} - Q_{\text{crit}}^{0\text{Year}} \right] \Big|_{@T}$$

(6)

where  $SER_{0Year}$  and  $SER_{3Years}$  are the soft error rates, and  $Q_{crit}^{0Year}$  and  $Q_{crit}^{3Years}$  are the critical charges without stress and after 3 years of NBTI stress, respectively.

## 2.2 | Masking factors

A direct way to improve the immunity of a logic circuit to radiation is adjusting the sizes of all the gates in order to sustain striking particle energy. However, this approach brings overhead costs like increased required chip area with it. One alternative solution can be masking of the SETs from the logic input to the circuits. The logical masking of any circuit depends on the input pattern, which is applied to the given circuit. Figure 1 shows the two possible combinations for the sensitization and logical masking for the two-input NAND gate. If one of the inputs is at logic high, a possible SET occurring at the other input at the same time will be directly transferred to the output. Whereas if one of the two inputs is at a logic low state, the SET occurring at the other input terminal is logically masked and it will not be transferred to the output and thus the SET will not affect subsequent stages. The probability of logical masking for any circuit is given by 36

(7)

$$P_{\text{Logical masking}} = 1 - P_{\text{Sensitization}}$$

.

#### 3 | SINGLE EVENT TRANSIENT EFFECT ON CIRCUIT PERFORMANCE

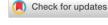

Figures 2 and 3 show the simulated circuit for the two-input NAND gate and NOR gate, respectively. In our simulations, the effect of the SET strike is considered to occur at the drain terminals of each of the transistors. In Figure 2, the parallel PMOS transistors are sensitive to the SET when both M1 and M2 are under stress and we inject SET current into the circuit node Y. In this situation, the active area for strike includes the drain area of both of the PMOS transistors. If we inject SET current with the opposite direction then it will perform a strike on M3. Similarly, if a SET current is injected at node N, it will perform strike on M4.

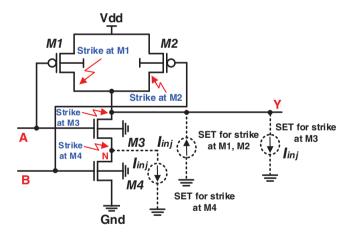

In Figure 3, the PMOS transistor M2 is sensitive to the SET when it is under stress, and we inject SET current into the circuit node Y. Similarly, the PMOS transistor M1 is sensitive to the SET when it is under stress, and we inject SET current into the circuit node P. In this situation, the active area for strike includes the drain area of PMOS transistors M2 and M1. If we inject SET current at node Y in the opposite direction, it will then perform a strike on the parallel NMOS transistors M3 and M4. $^{38,39}$

Here, we have considered a SET strike on only PMOS transistors for both NAND and NOR gates because the effect of NBTI is more severe for PMOS transistors.

## 3.1 | Critical charge analysis

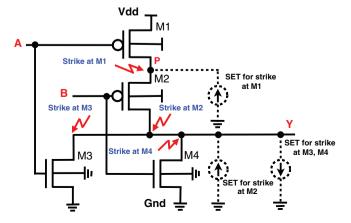

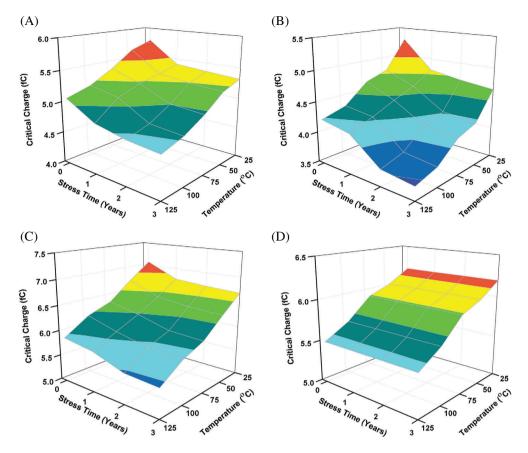

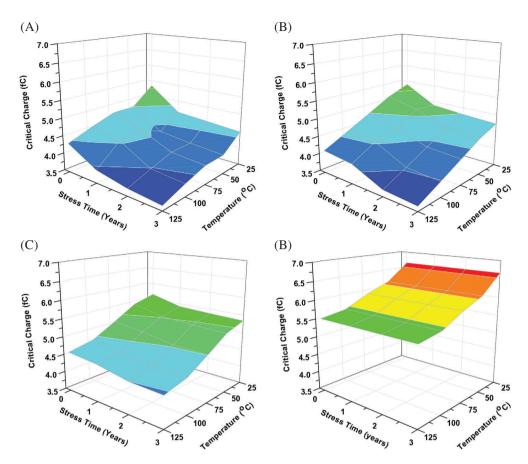

Figure 4 shows the critical charge of a two-input NAND gate as a function of the temperature and stress time for the four possible input combinations. Results demonstrate that the input combinations AB = 01 and AB = 10 exhibits the lowest and highest critical charge compared to the two other input combinations, respectively. Similarly, Figure 5

**FIGURE 2** SETs current source injecting into the sensitive node of all four transistors of the two-input NAND gate

FIGURE 3 SETs current source injecting into the sensitive node of all four transistors of the two-input NOR gate

FIGURE 4 Critical charge of the two-input NAND gate as a function of temperature at different stress times with different input patterns

shows the critical charge of a two-input NOR gate as a function of the temperature and stress time for the four possible input combinations. Results demonstrate that the input combinations AB = 00 and AB = 11 exhibits the lowest and highest critical charge compared to the two other input combinations, respectively. It is further observed that the critical charge for both the NAND gate and NOR gate decreases with increasing stress time and temperature.

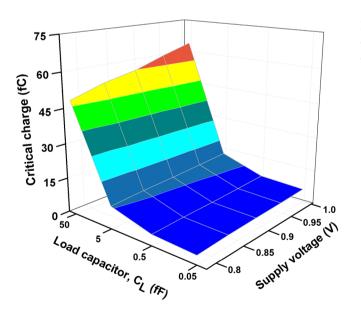

From the above results, we conclude that the two-input NAND gate and two-input NOR gate has minimum critical charges at AB = 01 and AB = 00, respectively, indicating that the effect of the soft error is highest for these input combinations. Our objective is to analyze the effect of the soft error on the ISCAS'85 c17 benchmark circuit, which consists of NAND gates. Therefore, input combination AB = 01 for NAND gate is considered for further analysis in Figure 6, which shows the critical charge variation for different supply voltages, considering different load capacitances. As can be seen, the critical charge of the sensitive node increases with the supply voltage due to the higher current flowing from the supply to the node and thus providing more charge at the sensitive node. A higher supply voltage changes the junction capacitance. When the supply voltage increases, the junction capacitance decreases due to the widening of the depletion region. An increase of the load capacitance also increases the effective circuit capacitance and thus a higher charge is required to unintendedly flip the logic.

## 3.2 | Soft error analysis

For the resistivity of the two-input NAND gate and NOR gate against soft errors, the SERR is evaluated. Table 1 shows the SERR after 3 years of stress at different operating temperatures. It is observed that the SERR increases with temperature for three possible input combinations of both two-input NAND gate and NOR gate. However, in the case of AB = 11, the SERR is constant for all the operating temperatures because none of the PMOS transistors is under NBTI stress. As can be seen, the two-input NAND gate and NOR gate is most sensitive to soft errors at the input combination of AB = 01 and AB = 00, respectively. To extend our analysis, we use the c17 circuit from the ISCAS'85 benchmark suite and is explained in the subsequent section.

FIGURE 5 Critical charge of the two-input NOR gate as a function of temperature at different stress times with different input patterns

**FIGURE 6** Two-input NAND gate critical charge characteristics shown at different supply voltages for various load capacitors  $(C_L)$

## 4 | ISCAS'85 C17 BENCHMARK CIRCUIT

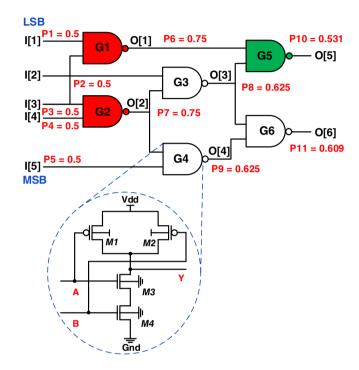

Figure 7 shows the circuit for c17 from the ISCAS'85 benchmark suite which consists of six interconnected NAND gates. We need to identify the critical path in the c17 circuit where the most number of PMOS transistors are stressed during normal operation. In this paper, we primarily focus on the NBTI for PMOS transistors. The PMOS transistors are stressed when a logical low state is applied at the respective input of the NAND gates. The probabilities of getting

**TABLE 1** Soft error rate ratio (SERR) at various operating temperatures for all possible input combinations of the two-input (A,B) NAND gate and NOR gate

|                  | NAND gate |       |       |     | NOR gate |       |       |     |

|------------------|-----------|-------|-------|-----|----------|-------|-------|-----|

| Temperature (°C) | 0,0       | 0,1   | 1,0   | 1,1 | 0,0      | 0,1   | 1,0   | 1,1 |

| 25               | 0.629     | 0.524 | 0.677 | 1.0 | 0.424    | 0.518 | 0.732 | 1.0 |

| 50               | 0.634     | 0.557 | 0.689 | 1.0 | 0.461    | 0.533 | 0.739 | 1.0 |

| 75               | 0.648     | 0.566 | 0.703 | 1.0 | 0.462    | 0.556 | 0.755 | 1.0 |

| 100              | 0.658     | 0.588 | 0.710 | 1.0 | 0.478    | 0.579 | 0.770 | 1.0 |

| 125              | 0.665     | 0.596 | 0.723 | 1.0 | 0.498    | 0.603 | 0.776 | 1.0 |

**FIGURE 7** Schematic of the c17 circuit from the ISCAS'85 benchmark suite.  $P_1$  through  $P_{11}$  are the input and output signal probabilities for six NAND gates of the c17 circuit. The PMOS transistors are under NBTI stress conditions when a logic low state is applied at the respective inputs

logic high at each node of the circuit,  $P_1$  through  $P_{11}$  are shown in Figure 7. All possible input pattern combinations are applied to the inputs I[1]-I[5] of the circuit to compute the probabilities. Here  $P_i$  is the ratio of the number of logic high states on line i to the total number of input patterns. The total number of possible combinations for this circuit are  $2^5 = 32$ . The input signal probability for each of the inputs I[1]-I[5] is considered to be 0.5, as the probability of primary input is 0 or 1 is assumed to be equal.

The effect of NBTI on PMOS transistors and its performance degradation depends on the input signal probability. Furthermore, the impact of NBTI on the entire c17 circuit depends on the input and output signal probability of each NAND gate. The output signal probability of each NAND gate is again the input probability of a subsequent NAND gate. The output signal probability for a logic high state of the input of each NAND gate can be expressed as<sup>41</sup>

$$P(Y=1) = 1 - P_{A}P_{B} \tag{8}$$

where  $P_{\rm A}$  and  $P_{\rm B}$  are the input signal probabilities for having a logic high state at the inputs (considering A and B are two inputs) of the respective NAND gate. As can be seen from Figure 7, the gates G1 and G2 have the highest probability to be NBTI stressed, as one or both inputs are at the logic low state more frequently than the inputs of other NAND gates. NAND gate G5 has the minimum probability of being stressed during operation. The NAND gates with the maximum stress during operation are highlighted in red whereas the NAND gates with minimum NBTI stress are highlighted in green.

Table 2 summarizes the minimum stress patterns and the worst-case stress patterns of 12 PMOS transistors from 6 NAND gates of the c17 circuit. In the c17 circuit, we have 32 possible input combinations and 12 PMOS transistors from 6 NAND gates. For each input combination, the number of stressed PMOS transistors are different. As there is a

total of 12 PMOS transistors, we manually checked the stressed transistors for all possible combinations. We observed that the input patterns 00010 and 10010 has the maximum number of stressed PMOS transistors. These input patterns are further used to analyze the degradation of the c17 circuit.<sup>42</sup>

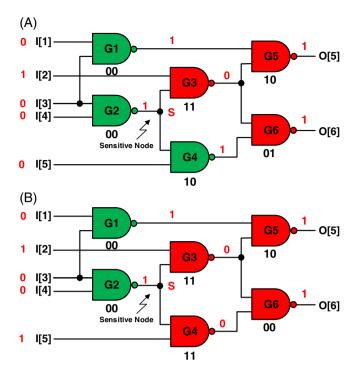

## 4.1 | Sensitization and Logical Masking

Table 3 shows the logical masking and sensitization probabilities of all NAND gates in the c17 benchmark circuit. It can be observed that the logical masking decreases with the number of stages move toward the output of the circuit.

For further analysis, the two worst-case input combinations (00010 and 10010) having the maximum number of PMOS transistors under stress are considered. The logical masking and sensitization of NAND gates on the c17 circuit for the most critical input patterns are shown in Figure 8. For the input pattern 00010, the gates G1, G2, and G4 are logically masked. As the output node (S) of G2 transfers the logic to the next stage, it is the primarily sensitive node in the c17 circuit. This node is considered to be a sensitive node because the stress of PMOS transistors and sensitization probability of the next stage gates depends on the logic at node S. A SET at this sensitive node will be directly transferred to the outputs through G3, G5, and G6, as shown in Figure 8A. The effect of the soft error to NAND gate G6 is more as compared to G5 because the critical charge for the NAND gate input combination 01 is the smallest among all other possible combinations. Thus the transfer of SET to the O[6] will be higher as compared to the output O[5].

Similarly for the input pattern 10010, the gates G1 and G2 are logically masked. A SET induced at node S in the circuit will transfer to the outputs through G3, G4, G5, and G6 as shown in Figure 8B. The effect of SET to NAND gate G6 is more as compared to G6 because the critical charge for input combination 00 is less as compared to the 10.

## 4.2 | Effect of supply voltage variation and device temperature variation on c17 circuit

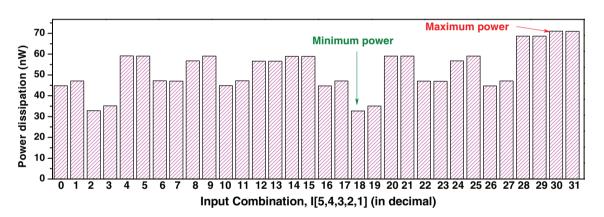

We calculate the active power dissipation of the c17 benchmark circuit considering all possible input combinations without stressing the circuit, as shown in Figure 9. From results, it is observed that the input combinations 10010 and 11110 have the minimum and maximum power dissipations, respectively.

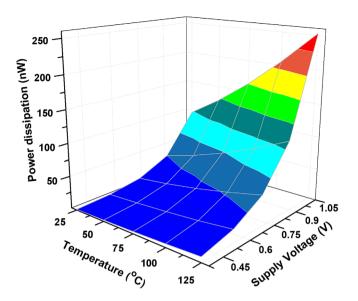

Further, to analyze the effect of supply voltage variation and temperature variation on the dynamic power dissipation by the c17 circuit, we calculated the circuit power dissipation for the device temperature ranging from 25°C to 125°C and different supply voltages from 0.45 to 1.05 V as shown in Figure 10. Results demonstrate that the circuit

|            | Maximum stress |            | Minimum s | stress |

|------------|----------------|------------|-----------|--------|

| NAND Gates | 00010          | 10010      | 11110     | 11111  |

| G1         | $M_1, M_2$     | $M_1, M_2$ | $M_1$     | -      |

| G2         | $M_1, M_2$     | $M_1, M_2$ | -         | -      |

| G3         | -              | _          | $M_2$     | $M_2$  |

| G4         | $M_2$          | _          | $M_1$     | $M_1$  |

| G5         | $M_2$          | $M_2$      | _         | $M_1$  |

| G6         | $M_1$          | $M_1, M_2$ | -         | -      |

**TABLE 2** Stressed PMOS transistors ( $M_1$  and  $M_2$ ) in all NAND gates of c17 circuit for the four extreme input patterns

| NAND Gates | $P_{ m Sensitization}$ | $P_{ m Logical-masking}$ |

|------------|------------------------|--------------------------|

| G1         | 0.25                   | 0.75                     |

| G2         | 0.25                   | 0.75                     |

| G3         | 0.375                  | 0.625                    |

| G4         | 0.375                  | 0.625                    |

| G5         | 0.4375                 | 0.5625                   |

| G6         | 0.4375                 | 0.5625                   |

**TABLE 3** Sensitization and logical masking probabilities of all NAND gates of the c17 circuit

FIGURE 8 Logical masking of the SET of the c17 circuit for two input combinations having maximum stressed PMOS transistors. A, For the input pattern 00010; and B, for the input pattern 10010. The logically masked NAND gates are represented in green whereas the NAND gates are not logically masked as represented in red

FIGURE 9 Static power dissipation of the c17 circuit for all the possible input combinations. Here, I[5] and I[1] are the most and least significant bits, respectively. There are 32 (0 to 31) total number of input combinations from five input c17 circuit

power dissipation increases with the supply voltages as well as the operating temperature of the circuit. To analyze the effect of supply and temperature variations, we calculated power dissipation sensitivity for the c17 circuit. The power dissipation sensitivity with supply voltage and temperature can be calculated as

$$Sensitivity_{power}\Big|_{@T} = \frac{Power|_{V_{dd}^{H}} - Power|_{V_{dd}^{L}}}{V_{dd}^{H} - V_{dd}^{L}}\Big|_{@T}$$

$$(9)$$

and

$$Sensitivity_{power}\Big|_{@V_{dd}} = \frac{Power|_{T^{H}} - Power|_{T^{L}}}{T^{H} - T^{L}}\Big|_{@V_{dd}}$$

$$(10)$$

where  $V_{\rm dd}^{\rm H}$  and  $V_{\rm dd}^{\rm L}$  are the higher and lower supply voltages and  $T^{\rm H}$  and  $T^{\rm L}$  are higher and lower temperatures, respectively. The power dissipation sensitivity with supply variations is 156.92 and 407.47  $\mu$ W/mV at 25°C and 125°C

**FIGURE 10** c17 circuit dynamic power dissipation with supply voltage and temperature variations

operating temperatures respectively, whereas, the power dissipation sensitivity with temperature variations are 71.49  $\mu$ W/°C and 1.57 nW/°C at 0.45 and 1.05 V supply voltages, respectively. From the above discussions, we observe that the change in power dissipation sensitivity is greater for supply voltage variations as compared to the temperature variations. This indicates that the power dissipation sensitivity increases at a higher temperature and supply voltage.

### 4.3 | Effect of SET on c17 circuit

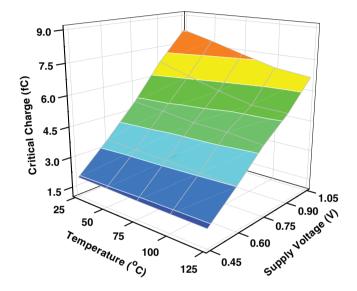

Figure 11 shows the critical charge at the sensitive node (S) of the c17 circuit for the input combination 00010 leading to maximum net stress for PMOS transistors. The stress time is considered to be 3 years in total. The result shows that the critical charge decreases with the stress time. Further, the critical charge at the sensitive node (S) for input combination 00010 is lower than 10010, and thus, the effect of SET is higher for 00010. The critical charge for the c17 circuit is decreased by 9.87% for the input combination 00010 after the stress time of 3 years, whereas, the critical charge is decreased by 6.72% in case the pattern 10010 is applied. This indicates that the soft error hardening of the circuit seriously depends on the NBTI stress of the PMOS transistor, on the selected input pattern of the circuit, and the logical masking and sensitization probability of the gates involved in the circuit.

Also, the effect of supply voltage and temperature variations on the critical charge at the sensitive node (S) of c17 circuit is analyzed, as shown in Figure 12. Results demonstrate that the critical charge increases with the supply voltage, whereas the critical charge decreases with increasing temperature. The critical charge sensitivity with supply voltage and temperature can be calculated as

$$Sensitivity_{Q_{crit}}\Big|_{@T} = \frac{Q_{crit}|_{V_{dd}^{H}} - Q_{crit}|_{V_{dd}^{L}}}{V_{dd}^{H} - V_{dd}^{L}}\Big|_{@T}$$

$$(11)$$

and

$$Sensitivity_{Q_{crit}}\Big|_{@V_{dd}} = \frac{Q_{crit}|_{T^H} - Q_{crit}|_{T^L}}{T^H - T^L}\Big|_{@V_{dd}}$$

$$(12)$$

The critical charge sensitivity with supply variations are 10.43 and 7.983 fC/V at 25°C and 125°C operating temperatures respectively, whereas, the critical charge sensitivity with temperature variations is 6.7 aJ/10°C and 153.4 aJ/10°C at 0.45 and 1.05 V supply voltages, respectively. From the above discussions, we can observe that the critical change

**FIGURE 11** Critical charge at the sensitive node (S) of the c17 circuit for two worst-case input combinations with the different stress time

**FIGURE 12** Critical charge variation at the sensitive node (S) of the c17 circuit with supply voltage and temperature variations for the input combination '00010'

**FIGURE 13** Monte Carlo distribution of the critical voltages at the sensitive node 'S' or O[2] and output O[5] of the c17 circuit for the input patterns having the maximum number of PMOS are under stress

sensitivity with supply voltage is higher as compared to the critical charge sensitivity with temperature. The critical charge at the sensitive node increases with supply voltage because the current driving capability of the circuit increases at higher supply voltage.

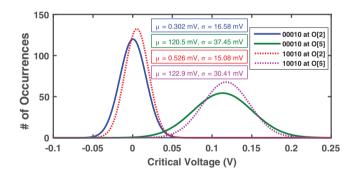

## 4.4 | Effect of process variations on c17 circuit

For the effect of process variations on the critical voltage at the sensitive node (S) and output node O[5], we have performed 5000 Monte Carlo simulations for the input combinations '00010' and '10010' as shown in Figure 13. We have considered only the O[5] output node because the signal probability is less as compared to the output node O[6], as shown in Figure 7. Results demonstrate that the effect of process variation is more at the sensitive node (S) and output

node O[5] for the input combination '00010' as compared to the '10010'. A higher deviation indicates that the sensitive node is more sensitive to the process variation as well as a single event transient.

#### 5 | CONCLUSION

Performance degradation of transistors due to NBTI and single event transients occurring in ICs might give rise to unstable electronic applications. We analyze the effect of NBTI on the soft error susceptibility on two input NAND and NOR gates as well as on the ISCAS'85 c17 benchmark circuit. We show that NBTI significantly reduces the critical charge at the sensitive nodes of the circuits. We further introduce a soft error rate ratio (SERR) to validate the effect of NBTI at various operating temperatures and observe that the NAND gate and NOR gate is most sensitive to the soft error at the input combination AB = 01 and AB = 00, respectively. Further, we also determine the critical charge of the sensitive node for all possible worst-case input combinations of the c17 benchmark circuit. We also evaluate the critical charge sensitivity at the sensitive node of the c17 circuit with temperature and supply variations and observe that the critical charge sensitivity with supply variation is more as compared to temperature variations. The effect of process variations is considered using 5000 Monte Carlo simulations at the sensitive node of the c17 circuit. The result indicates that the c17 circuit is most sensitive to the soft error if the maximum number of PMOS transistors is under stress.

#### **ACKNOWLEDGEMENTS**

The research leading to this work has received substantial funding from the Take-off program of the Austrian Research Promotion Agency FFG (projects no. 861022, and 867414, and INCONTROL-RL). The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development and the Christian Doppler Research Association is gratefully acknowledged too. The authors also acknowledge TU Wien Bibliothek for financial support through its Open Access Funding Programme.

#### ORCID

Ambika Prasad Shah https://orcid.org/0000-0003-0810-814X Michael Waltl https://orcid.org/0000-0001-6042-759X

#### REFERENCES

- 1. Shah AP, Rossi D, Sharma V, Vishvakarma SK, Waltl M. Soft error hardening enhancement analysis of NBTI tolerant Schmitt trigger circuit. *Microelectron Reliab*. 2020;107:113617.

- 2. Ang D, Wang S, Du G, Hu Y. A consistent deep-level hole trapping model for negative bias temperature instability. *IEEE Trans Device Mater Reliab*. 2008;8(1):22-34.

- 3. Grasser T, Kaczer B. Evidence that two tightly coupled mechanisms are responsible for negative bias temperature instability in oxynitride MOSFETs. *IEEE Trans Electron Dev.* 2009;56(5):1056-1062.

- 4. Schroder DK. Negative bias temperature instability: what do we understand? Microelectron Reliab. 2007;47(6):841-852.

- 5. Shah AP, Yadav N, Beohar A, Vishvakarma SK. Process variation and NBTI resilient Schmitt trigger for stable and reliable circuits. *IEEE Trans Device Mater Reliab*. 2018;18(4):546-554.

- 6. Wang Y, Enachescu M, Cotofana SD, Fang L. Variation tolerant on-chip degradation sensors for dynamic reliability management systems. *Microelectron Reliab*. 2012;52(9):1787-1791.

- 7. Schrimpf R, Warren K, Weller R, et al. Reliability and radiation effects in IC technologies. *Reliability Physics Symposium, 2008. IRPS 2008. IEEE International.* Phoenix, AZ: IEEE; 2008:97-106.

- 8. Rott GA, Rott K, Reisinger H, Gustin W, Grasser T. Mixture of negative bias temperature instability and hot-carrier driven threshold voltage degradation of 130 nm technology p-channel transistors. *Microelectron Reliab*. 2014;54(9–10):2310-2314.

- 9. Afacan E, Yelten MB, Dündar G. Analog design methodologies for reliability in nanoscale CMOS circuits. 2017 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD). Giardini Naxos, Italy: IEEE; 2017:1-4.

- 10. Baumann RC. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans Dev Mater Reliab. 2005;5(3):305-316.

- 11. Bol D, Ambroise R, Flandre D, Legat J-D. Interests and limitations of technology scaling for subthreshold logic. *IEEE Trans Very Large Scale Integr VLSI Syst.* 2009;17(10):1508-1519.

- 12. Lin S, Kim Y-B, Lombardi F. Analysis and design of nanoscale CMOS storage elements for single-event hardening with multiple-node upset. *IEEE Trans Dev Mater Reliab*. 2012;12(1):68-77.

- 13. Detcheverry C, Dachs C, Lorfevre E, et al. SEU critical charge and sensitive area in a submicron CMOS technology. *IEEE Trans Nucl Sci.* 1997;44(6):2266-2273.

- 14. Cohen N, Sriram T, Leland N, Moyer D, Butler S, Flatley R. Soft error considerations for deep-submicron CMOS circuit applications. *International Electron Devices Meeting 1999. Technical Digest (Cat. No. 99CH36318)*. Washington, DC: IEEE; 1999:315-318.

- 15. Mavis DG, Eaton PH. Soft error rate mitigation techniques for modern microcircuits. 2002 IEEE International Reliability Physics Symposium. Proceedings. 40th Annual (Cat. No. 02CH37320). Dallas, TX: IEEE; 2002:216-225.

- 16. Baumann R. The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction. *Electron Devices Meeting*, 2002. *IEDM'02. International*. San Francisco, CA: IEEE; 2002:329-332.

- 17. Abe S-i, Watanabe Y, Shibano N, et al. Neutron-induced soft error analysis in MOSFETs from a 65 nm to a 25 nm design rule using multi-scale Monte Carlo simulation method. *Reliability Physics Symposium (IRPS)*, 2012 IEEE International. Anaheim, CA: IEEE; 2012:SE-3.

- 18. Shah AP, Yadav N, Beohar A, Vishvakarma SK. An efficient NBTI sensor and compensation circuit for stable and reliable SRAM cells. *Microelectron Reliab*. 2018;87:15-23.

- 19. Uemura T, Kato T, Matsuyama H, Hashimoto M. Soft-error in SRAM at ultra-low voltage and impact of secondary proton in terrestrial environment. *IEEE Trans Nucl Sci.* 2013;60(6):4232-4237.

- 20. Li L, Xiao L, Cao X, Qi C, Mao Z. Impact of BTI aging effect on soft error rate of combination circuit. 2017 Prognostics and System Health Management Conference (PHM-Harbin). Harbin, China: IEEE; 2017:1-5.

- 21. Rossi D, Omaña M, Metra C, Paccagnella A. Impact of aging phenomena on soft error susceptibility. 2011 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems. Vancouver, BC, Canada: IEEE; 2011:18-24.

- 22. Chandra V, Aitken R. Impact of technology and voltage scaling on the soft error susceptibility in nanoscale CMOS. *IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems*. Boston, MA: IEEE; 2008:114-122.

- 23. Bagatin M, Gerardin S, Paccagnella A, Faccio F. Impact of NBTI aging on the single-event upset of SRAM cells. *IEEE Trans Nucl Sci.* 2010;57(6):3245-3250.

- 24. Cannon EH, KleinOsowski A, Kanj R, Reinhardt DD, Joshi RV. The impact of aging effects and manufacturing variation on SRAM soft-error rate. *IEEE Trans Dev Mater Reliab*. 2008;8(1):145-152.

- 25. Rossi D, Omaña M, Metra C, Paccagnella A. Impact of bias temperature instability on soft error susceptibility. *IEEE Trans Very Large Scale Integr VLSI Syst.* 2014;23(4):743-751.

- 26. Sierawski BD, Warren KM, Reed RA, et al. Contribution of low-energy (<<10 meV) neutrons to upset rate in a 65 nm SRAM. *Reliability Physics Symposium (IRPS), 2010 IEEE International.* Anaheim, CA: IEEE; 2010:395.

- 27. Calomarde A, Amat E, Moll F, Vigara J, Rubio A. SET and noise fault-tolerant circuit design techniques: application to 7 nm FinFET. *Microelectron Reliab*. 2014;54(4):738-745.

- 28. ISCAS'85 Benchmark Circuits, http://www.pld.ttu.ee/~maksim/benchmarks/iscas85/, Accessed April 9, 2019.

- 29. Predictive Technology Model (PTM), http://ptm.asu.edu/, Accessed December 12, 2017.

- 30. Synopsys, "Hspice user guide: simulation and analysis," 2010.

- 31. Jahinuzzaman SM, Sharifkhani M, Sachdev M. An analytical model for soft error critical charge of nanometric SRAMs. *IEEE Trans Very Large Scale Integr VLSI Syst.* 2009;17(9):1187-1195.

- 32. Alouani I, Elsharkasy WM, Eltawil AM, Kurdahi FJ, Niar S. AS8-static random access memory (SRAM): asymmetric SRAM architecture for soft error hardening enhancement. *IET Circ Dev Syst.* 2017;11(1):89-94.

- 33. Ding Q, Luo R, Wang H, Yang H, Xie Y. Modeling the impact of process variation on critical charge distribution. *SOC Conference*, 2006 *IEEE International*. Taipei, Taiwan: IEEE; 2006:243-246.

- 34. Hazucha P, Svensson C. Impact of CMOS technology scaling on the atmospheric neutron soft error rate. *IEEE Trans Nucl Sci.* 2000;47 (6):2586-2594.

- 35. Shivakumar P, Kistler M, Keckler SW, Burger D, Alvisi L. Modeling the effect of technology trends on the soft error rate of combinational logic. *Proceedings International Conference on Dependable Systems and Networks*. Washington, DC: IEEE; 2002:389-398.

- 36. Zhou Q, Mohanram K. Gate sizing to radiation harden combinational logic. *IEEE Trans Comput-Aided Des Integr Circ Syst.* 2005;25(1): 155-166.

- 37. Sootkaneung W, Howimanporn S, Chookaew S. Temperature effects on BTI and soft errors in modern logic circuits. *Microelectron Reliab*. 2018;87:259-270.

- 38. Khan S, Hamdioui S, Kukner H, Raghavan P, Catthoor F. BTI impact on logical gates in nano-scale CMOS technology. 2012 IEEE 15th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS). Tallinn, Estonia: IEEE; 2012:348-353.

- 39. Andjelkovic M, Krstic M, Kraemer R. Comparison of the SET sensitivity of standard logic gates designed in 130 nm CMOS technology. 2017 IEEE 30th International Conference on Microelectronics (MIEL). Nis, Serbia: IEEE; 2017:217-220.

- 40. Shah AP, Girard P. Impact of aging on soft error susceptibility in CMOS circuits. 2020 IEEE 26th International Symposium on On-Line Testing and Robust System Design (IOLTS). Napoli, Italy: IEEE; 2020:1-4.

- 41. Ghavami B, Raji M, Saremi K, Pedram H. An incremental algorithm for soft error rate estimation of combinational circuits. *IEEE Trans Device Mater Reliab*. 2018;18(3):463-473.

- 42. Shah AP, Moshrefi A, Waltl M. Utilizing NBTI for operation detection of integrated circuits. *International Symposium on VLSI Design and Test*. Indore, India: Springer; 2019:190-201.