# DISSERTATION

# **Integrating Technology Simulation** into the Semiconductor Manufacturing **Environment**

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

O.Univ.Prof. Dipl.-Ing. Dr.techn. Siegfried Selberherr Institut für Mikroelektronik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

Rainer Minixhofer

TU **Bibliothek**, Die approbierte gedruckte Originalversion dieser Dissertation ist an der TU Wien Bibliothek verfügbar.

The approved original version of this doctoral thesis is available in print at TU Wien Bibliothek.

Sein und Wissen ist ein uferloses Meer: Je weiter wir vordringen, um so unermeßlicher dehnt sich aus, was noch vor uns liegt jeder Triumph des Wissens schließt hundert Bekenntnisse des Nichtwissens in sich.

Isaac Newton

# Kurzfassung

IE FERTIGUNG VON INTEGRIERTEN SCHALTKREISEN ist heutzutage ein Milliardendollargeschäft und einer der kompliziertesten Industriezweige der Welt.

Historisch gesehen haben sich die Entwicklungskosten für das Einführen einer neuen Prozesstechnologie (eines neuen Technologieknotens) ständig erhöht. Diese Tendenz wird durch den Eintritt in den Bereich der Nanotechnologie mit seinen in hohem Grade schwierigen neuen Lithographieprozessen noch weiter beschleunigt. Um diesen Trend unter Kontrolle halten zu können, hat Computergestützte Technologiesimulation (TCAD) immer mehr an Bedeutung gewonnen.

Dieser Ansatz der "frühest möglichen" Entwicklung, hat die Geschwindigkeit und die Qualität der Verfahrenstechnikentwicklung des Halbleiters erheblich verbessert. Weiters konnten dadurch auch die Entwicklungskosten für die Einführung einer neuen Technologiegeneration signifikant reduziert werden (35% im Jahr 2005 [1]).

Derzeit ist TCAD eine sehr spezialisierte Vorgehensweise für eine kleine Gruppe von Ingenieuren innerhalb der Halbleiterfirmen. Die konsequente Nutzung dieser Methode im Bereich der Fertigungssteuerung steckt trotz des großen Einsparungspotentials noch in den Kinderschuhen.

Technologiesimulation hat bis heute den Sprung, von einem Werkzeug für eine kleine Gruppe von Spezialisten zu einem bei Routinetätigkeiten eingesetzten Werkzeug für eine grössere Anzahl von Anwendern im Halbleiterfertigungsbereich, noch nicht geschafft.

Hauptprobleme bei der breiteren Nutzung entstehen durch die komplexe oft wenig intuitive Benutzung der Werkzeuge, die aufwendigen zugrundeliegenden Modellansätze und vor allem durch die fehlende Integration in den Arbeitsablauf in einer modernen Halbleiterfertigungslinie.

Diese Arbeit zielt darauf ab, die Distanz zwischen der Halbleiter-Fertigungsline und der TCAD Gruppe, die in fast jeder Halbleiterproduktionsfirma existiert, zu überbrücken. Dabei kommt der Ubertragung von bereits vorhandenen Strukturen und Arbeitsabläufen in gespiegelter Form auf das TCAD System ein besonderer Stellenwert zu.

Das dabei entstandene, in die Fertigung eng integrierte, Simulationssystem ermöglicht es auch, nichtspezialisierten Ingenieuren von den Vorteilen der Technologiesimulation zu profitieren.

In dieser Arbeit wurde die Gesamtsituation beider Welten analysiert und in einer strukturierten, hierarchischen Weise kategorisiert. Ein konsistenter und effektiver TCAD Arbeitsfluss wurde aufgesetzt. Die notwendigen Informationen für diesen Arbeitsfluss wurden identifiziert. Zusätzlich wurden die bestehenden Datenschnittstellen zwischen Fertigung und Simulation analysiert und deren Struktur und Verknüpfungspunkte dargestellt.

Die dabei identifizierten Schnittstellen zwischen TCAD und Fertigung wurden nachfolgend einer genaueren Analyse unterzogen und schlussendlich ein integriertes Schnittstellensystem zwischen den beiden "Welten" implementiert. Es wurde darauf Wert gelegt, das dieses integrierte Schnittstellensystem für die Gemeinsamkeiten aller verfügbaren TCAD Softwarepakete verwendet werden kann.

Um die notwendigen Eingabeinformationen für Simulationen möglichst automatisch und fehlerminimierend generieren zu können, wurde basierend auf dieser Analyse ein kompakter Satz von Konvertern und Datentransfer-Prozeduren definiert. Die Interaktion mit dem Benutzer des TCAD Systems wurde auf das absolut notwendige Minimum beschränkt. Dies führte zu einer starken Verbesserung der Qualität, Zuverlässigkeit und auch Vorhersagbarkeit der Resultate der TCAD Simulationen.

Die Konverter wurden in den gesamten TCAD Arbeitsfluss integriert. Mehrere Beispiele für fast jeden Aspekt des typischen TCAD Arbeitsflusses zeigen die wichtigsten Auswirkungen dieses neuen Ansatzes. Während der Entwicklung von neuen Prozesstechnologien aber auch speziell zur Unterstützung von typischen Produktionsproblemen (wie Ausbeuteproblemen in der Fertigung) konnte dieser Ansatz erfolgreich angewendet werden. Weiters wurden damit Optimierungen von Ofenprogrammen (ein auch im Routinebetrieb einer Halbleiterfertigung immer wieder auftretender Fall) durchgeführt. Es konnte die Verwendung von Beugungskorrekturrechnung für eine genauere Darstellung von Verbindungsstrukturen gezeigt werden. Dadurch konnte eine wesentliche Verbesserung in der Berechnung von parasitären Elementen, der Optimierung einer EEPROM Zelle und der drei-dimensionalen Simulation einer lateralen PIN Diode erzielt werden. Als ein weiterer Anwendungsbereich wurde die inverse Modellierung einer polykristallinen Fuse gezeigt. Dabei wurden sehr schwer messbare thermo-elektrische Materialparameter von in der Fuse verwendeten Materialien (Wolfram, Titan, Titannitrid) über inverse Modellierung bestimmt. Abschliessend wurde die Verwendung von Technologiesimulation im Bereich der statistischen Prozesskontrolle dargelegt.

Die Arbeit schliesst mit einem kurzen Ausblick auf zukünftige Perspektiven und noch offene Probleme.

## Abstract

INTEGRATED CIRCUIT MANUFACTURING is nowadays a multi-billion dollar business and one of the most complex industry branches in the world.

Historically the development costs for introducing a new technology generation (technology node) have been steadily increasing. This trend is even accelerated by entering the nanotechnology regime with its highly complicated new lithography processes. To keep this trend under control, Technology Computer Aided Design (TCAD) have gained more and more importance.

This "front loaded" approach in development has improved the speed and quality of the semiconductor process technology development significantly. It was also very successful in reducing the development cost significantly (by 35% in 2005[1]).

However TCAD is still mainly a very specialized tool for only a small group of engineers inside semiconductor companies. Despite the big savings potential, the consistent application of this methodology on the control of the manufacturing process is still in the fledgling stages.

Technology simulation has not done the leap, from a tool for a small group from specialists to a tool for a larger number of users in the semiconductor production area, yet.

Main problems of the broader use result from the complex, often little intuitive use of the tools, the complex underlying physical models and particularly by the missing integration into the work flow of a modern semiconductor production line.

This work aims to bridge the distance between the semiconductor manufacturing line and the TCAD group, which exists in nearly each semiconductor production company. Special attention has to be payed to the transfer of the operational work flow sequences to the TCAD system in a similar form.

This new system enables non-specialized engineers to profit from the advantages of a theoretical evaluation through the closely integrated TCAD framework.

In this work the overall situation of both worlds was analyzed and categorized in a structured, hierarchical way. A consistent and effective TCAD work flow was set up. The necessary information for this work flow was identified. Additionally the existing data interfaces between manufacturing and simulation were analyzed and their structure and coupling nodes were represented.

In the following the interfaces between TCAD and manufacturing, identified thereby, were subject to a more throughout analysis and finally an integrated interface system between the two "worlds" was implemented. A strong emphasis was put on the border condition that all available TCAD software packages could be used together with this new integrated interface system.

In order to be able to generate the necessary input information for simulations as automatically and resistant to errors as possible, based on this analysis a compact set of converters and data transfer procedures was defined. The interaction with the user of the TCAD system was limited to the absolutely necessary minimum. This led to a strong improvement of the quality, reliability and also predictabilty of the results of the TCAD simulations.

The converters were integrated into the entire TCAD work flow. Several examples of nearly each aspect of the typical TCAD work flow show the most important effects of this new approach. In addition, during the development of new process technologies, particularly for the support of typical production problems (like yield problems in the manufacturing) this approach has been tested successfully. Furthermore, optimizations of furnace programs (a task which may frequently occur during manufacturing of qualified processes too) have been performed. The use of diffraction correction calculation for a better representation of interconnect structures could be shown. Thus a substantial improvement in the computation of parasitic elements, the optimization of a EEPROM cell and the three-dimensional simulation of a lateral pin diode could be obtained. As a further application area the inverse modelling of a polycrystalline fuse was shown. The difficult to measure thermoelectric material parameters of the materials used in the fuse (e.g. tungsten, titanium, titanium nitride) were determined through inverse modelling. Finally the use of technology simulation within the area of statistic process control was demonstrated.

The work closes with a short outlook and open problems.

# Acknowledgment

FIRST AND FOREMOST I want to thank Prof. SIEGFRIED SELBERHERR for giving me the opportunity to conduct my scientific work in parallel to my professional engagement in semiconductor industry. Furthermore, for providing the excellent infrastructure at the Institute for Microelectronics, and for the professional support and help in getting me to finalize my thesis.

I thank Prof. Wolfgang Pribyl, that he was willing to serve on my examination committee even on very short notice.

I am grateful to my boss MARTIN SCHREMS to help me with my thesis in a very supportive and positive manner. Furthermore, he provided a very innovative and interesting working environment.

I wish to thank all my co-authors for the very good and fruitful discussion on the contents of my publications.

I especially want to thank Georg Röhrer from austriamicrosystems AG, Dieter Rathei from DR Yield, STEFAN HOLZER and ANDREAS HÖSSINGER from Institute for Microelectronics, TU Vienna and JÜRGEN LORENZ from the Fraunhofer Gesellschaft, IISB for their contributions to the examples in Chapter 6.

After all my wife Christine and my children Christoph and Benjamin provided me with love and understanding, especially when another weekend passes by, me sitting at the computer and working on my thesis. They carried me through the tough times last year, when the work seemed to be never ending.

Finally, none of my studies would have been possible without the continuous support of my parents.

## This work is dedicated to my father WERNER MINIXHOFER who passed away far too early

'... Das Unmögliche = Das, was man nie versucht hat.' (The impossible = What one has never tried)

Hans Günther Adler (1910 - 1988)

# Contents

| Kur  | rzfassung                                         | ii                                                                                                                                                                                                            |

|------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abs  | stract                                            | iv                                                                                                                                                                                                            |

| Ack  | cnowledgment                                      | vi                                                                                                                                                                                                            |

| Con  | ntents                                            | viii                                                                                                                                                                                                          |

| List | of Abbreviations and Acronyms                     | xiv                                                                                                                                                                                                           |

| List | of Symbols                                        | xvi                                                                                                                                                                                                           |

|      | Notation                                          | xvi                                                                                                                                                                                                           |

|      | Constants                                         | xvi                                                                                                                                                                                                           |

| List | of Figures x                                      | vii                                                                                                                                                                                                           |

| List | of Tables                                         | xxi                                                                                                                                                                                                           |

| Intr | roduction                                         | 1                                                                                                                                                                                                             |

| The  | e Processing Chain in Semiconductor Manufacturing | 3                                                                                                                                                                                                             |

| 2.1  | Overview                                          | 3                                                                                                                                                                                                             |

| 2.2  | Design                                            | 4                                                                                                                                                                                                             |

| 2.3  | Layout                                            | 7                                                                                                                                                                                                             |

| 2.4  | Mask Generation                                   | 9                                                                                                                                                                                                             |

|      | Abs Ack Cor List List List The 2.1 2.2 2.3        | List of Abbreviations and Acronyms  List of Symbols Notation Constants  List of Figures  List of Tables  Introduction  The Processing Chain in Semiconductor Manufacturing 2.1 Overview 2.2 Design 2.3 Layout |

|   |     | 2.4.1                           | Introduction                                         | 9                    |

|---|-----|---------------------------------|------------------------------------------------------|----------------------|

|   |     | 2.4.2                           | Imaging Basics                                       | 9                    |

|   |     | 2.4.3                           | Optical Proximity Effect                             | 13                   |

|   | 2.5 | Fabric                          | eation                                               | 14                   |

|   |     | 2.5.1                           | Description of Semiconductor Manufacturing Processes | 14                   |

|   |     | 2.5.2                           | Lithography                                          | 14                   |

|   |     | 2.5.3                           | Ion Implantation                                     | 14                   |

|   |     | 2.5.4                           | Diffusion                                            | 17                   |

|   |     | 2.5.5                           | Film Deposition                                      | 17                   |

|   |     | 2.5.6                           | Etching                                              | 18                   |

|   |     |                                 | 2.5.6.1 Isotropic Etching                            | 18                   |

|   |     |                                 | 2.5.6.2 Anisotropic Etching                          | 18                   |

|   | 2.6 | Electr                          | ical Test                                            | 18                   |

|   | 2.7 | Sort a                          | nd Final Test                                        | 25                   |

|   | 2.8 | Packa                           | ging                                                 | 26                   |

| 3 | The | тсл                             | D Concept                                            | 27                   |

| 3 | 3.1 |                                 | luction and State-Of-The-Art                         | 27                   |

|   | 3.1 | 3.1.1                           | Process Simulation                                   | 27                   |

|   |     | 3.1.1                           |                                                      |                      |

|   |     |                                 | 3.1.1.1 Generic Process Simulators                   | 28                   |

|   |     | 0.1.0                           | 3.1.1.2 Equipment Simulators                         | 29                   |

|   |     | 3.1.2                           | Device Simulators                                    | 29                   |

|   |     |                                 | 3.1.2.1 Generic Device Simulators                    | 30                   |

|   |     | 0.1.0                           | 3.1.2.2 Specialized Device Simulators                | 30                   |

|   |     | 3.1.3                           | TCAD Work Flow Environment Software                  | 31                   |

|   | 3.2 | () TOTAL                        |                                                      |                      |

|   |     |                                 | iew                                                  | 32                   |

|   | 3.3 | TCAI                            | O Input                                              | 33                   |

|   | 3.3 |                                 | D Input                                              |                      |

|   | 3.3 | TCAI                            | O Input                                              | 33                   |

|   | 3.3 | TCAI<br>3.3.1<br>3.3.2<br>3.3.3 | D Input                                              | 33<br>33             |

|   | 3.4 | TCAI<br>3.3.1<br>3.3.2<br>3.3.3 | D Input                                              | 33<br>33<br>34       |

|   |     | TCAI 3.3.1 3.3.2 3.3.3 Proces   | D Input                                              | 33<br>33<br>34<br>36 |

|   | 3.6  | Conta   | ct Definition                                                                   | 44 |

|---|------|---------|---------------------------------------------------------------------------------|----|

|   | 3.7  | Device  | e Simulation                                                                    | 44 |

|   | 3.8  | Electr  | ical Key-Parameter Extraction                                                   | 47 |

|   | 3.9  | Optim   | nization and Inverse Modeling                                                   | 47 |

| 4 | Inte | egratio | n between Semiconductor Fabrication and TCAD                                    | 49 |

|   | 4.1  | Introd  | uction                                                                          | 49 |

|   | 4.2  | Interfa | aces                                                                            | 49 |

|   |      | 4.2.1   | Between Design/Layout as Process Simulation Input                               | 49 |

|   |      | 4.2.2   | Between Process Flow Description and Process Simulation Command File            | 53 |

|   |      | 4.2.3   | Between Electrical Test and Device Simulation                                   | 55 |

|   |      | 4.2.4   | Between Device Characterization and Device Modeling (SPICE) $\ \ldots \ \ldots$ | 56 |

|   | 4.3  | Packag  | ge Modeling Interface                                                           | 57 |

| 5 | Imp  | olemen  | tation                                                                          | 58 |

|   | 5.1  | Layou   | t Interface                                                                     | 58 |

|   | 5.2  | Proces  | ss Flow Interface                                                               | 59 |

|   |      | 5.2.1   | Semiconductor Process Flows in Development                                      | 59 |

|   |      | 5.2.2   | Semiconductor Process Flows in Production                                       | 59 |

|   |      | 5.2.3   | Diffusion Recipes                                                               | 61 |

|   |      | 5.2.4   | Other Recipes                                                                   | 62 |

|   |      | 5.2.5   | Conclusions                                                                     | 62 |

|   | 5.3  | Electr  | ical Test Interface                                                             | 65 |

|   |      | 5.3.1   | Introduction                                                                    | 65 |

|   |      | 5.3.2   | Electrical Parameter Test                                                       | 66 |

|   |      |         | 5.3.2.1 Measurement Routines                                                    | 66 |

|   |      |         | 5.3.2.2 Test Program Definition                                                 | 68 |

|   |      |         | 5.3.2.3 Automated Creation of Test Program Definitions                          | 68 |

|   |      | 5.3.3   | Documentation                                                                   | 69 |

|   |      | 5.3.4   | Conclusions                                                                     | 69 |

|   | 5.4  | SPICE   | E Modeling Interface                                                            | 69 |

| 6 | Ind  | ustrial | Application of TCAD                                                             | 71 |

X

6.1

|              |     | and 8"   | Wafer Fabrication Facilities                                                                             | L |

|--------------|-----|----------|----------------------------------------------------------------------------------------------------------|---|

|              | 6.2 | Docum    | nentation and Training                                                                                   | 1 |

|              | 6.3 | Layou    | t and Mask Generation                                                                                    | 5 |

|              |     | 6.3.1    | Proximity Correction of Masks                                                                            | 5 |

|              |     | 6.3.2    | Integrating an EEPROM Module into a State-of-the-Art Silicon Foundry Process with Three-Dimensional TCAD | 3 |

|              |     |          | 6.3.2.1 Introduction                                                                                     | 3 |

|              |     |          | 6.3.2.2 EEPROM Module Integration                                                                        | 3 |

|              |     |          | 6.3.2.3 EEPROM Cell Optimization                                                                         | ) |

|              |     |          | 6.3.2.4 Conclusions                                                                                      | 1 |

|              |     | 6.3.3    | Generation of 3D-Mask Photo Resist Shape for lateral PIN-Diodes 85                                       | 5 |

|              | 6.4 | Inverse  | e Modeling of Polycrystalline Fuses                                                                      | 3 |

|              |     | 6.4.1    | Introduction                                                                                             | 3 |

|              |     | 6.4.2    | Experiment                                                                                               | 2 |

|              |     | 6.4.3    | Simulation and Inverse Modeling                                                                          | 1 |

|              |     |          | 6.4.3.1 Mathematical Models                                                                              | 1 |

|              |     |          | 6.4.3.2 Simulation Setup                                                                                 | 1 |

|              |     |          | 6.4.3.3 Inverse Modeling                                                                                 | 5 |

|              |     | 6.4.4    | Results and Discussion                                                                                   | 5 |

|              |     | 6.4.5    | Conclusions                                                                                              | 7 |

|              | 6.5 | Using    | TCAD with SPC                                                                                            | 3 |

|              |     | 6.5.1    | Introduction                                                                                             | 3 |

|              |     | 6.5.2    | Computational Effort                                                                                     | ) |

|              |     | 6.5.3    | Selecting a Set of Parameters                                                                            | ) |

|              |     | 6.5.4    | Simulation Results                                                                                       | ) |

|              |     | 6.5.5    | Conclusions                                                                                              | ) |

| 7            | Sun | nmary    | and Outlook 103                                                                                          | L |

| $\mathbf{A}$ | Bas | is of tl | ne GAUSSIAN Normal Distribution Function 102                                                             | 2 |

|              | A.1 |          | Aussian Normal Distribution                                                                              |   |

|              | A.2 |          | entral Limit Theorem                                                                                     |   |

|              |     |          |                                                                                                          |   |

Transfer of Semiconductor Diffusion and Oxidation Process Recipes Between 4"

|   |     | A.2.1   | Theorem                                     |

|---|-----|---------|---------------------------------------------|

|   |     | A.2.2   | Proof                                       |

| В | Lay | out Da  | ata Formats 108                             |

|   | B.1 | Caltec  | h Intermediate Format (CIF)                 |

|   |     | B.1.1   | Geometry                                    |

|   |     | B.1.2   | Hierarchy                                   |

|   |     | B.1.3   | Control                                     |

|   | B.2 | Calma   | GDS II stream format (GDSII)                |

|   |     | B.2.1   | Record Format                               |

|   |     | B.2.2   | Library Head and Tail                       |

|   |     | B.2.3   | Structure Head and Tail                     |

|   |     | B.2.4   | Boundary Element                            |

|   |     | B.2.5   | Path Element                                |

|   |     | B.2.6   | Structure Reference Element                 |

|   |     | B.2.7   | Array of Structures Element                 |

|   |     | B.2.8   | Text Element                                |

|   |     | B.2.9   | Node Element                                |

|   |     | B.2.10  | Box Element                                 |

|   | В.3 | Electro | onic Design Interchange Format (EDIF)       |

|   |     | B.3.1   | EDIF Structure                              |

|   |     | B.3.2   | Contents                                    |

|   |     |         | B.3.2.1 Declarations                        |

|   |     |         | B.3.2.2 Instances                           |

|   |     |         | B.3.2.3 Routing and Simulation              |

|   |     |         | B.3.2.4 Geometry                            |

|   |     |         | B.3.2.5 Miscellaneous Statements            |

|   |     | B.3.3   | Interface                                   |

|   |     |         | B.3.3.1 Ports and Bodies                    |

|   |     |         | B.3.3.2 Gate-Array and Behavioral Interface |

|   |     | B.3.4   | View Maps                                   |

|   |     | B.3.5   | Technology                                  |

|   |     |         |                                             |

|              | B.4  | Electro        | on Beam Exposure System (EBES) Format                   | 133 |

|--------------|------|----------------|---------------------------------------------------------|-----|

|              |      | B.4.1          | File Structure                                          | 133 |

|              |      | B.4.2          | Control Commands                                        | 134 |

|              |      | B.4.3          | Rectangles                                              | 134 |

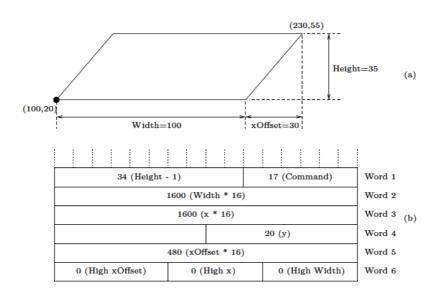

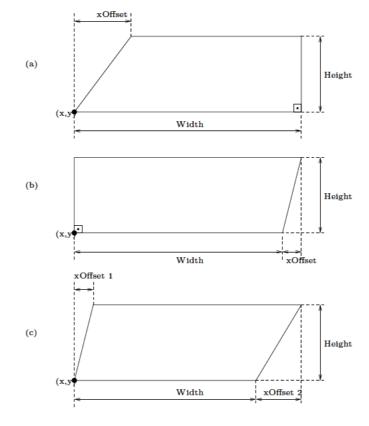

|              |      | B.4.4          | Parallelograms                                          | 134 |

|              |      | B.4.5          | Trapezoids                                              | 135 |

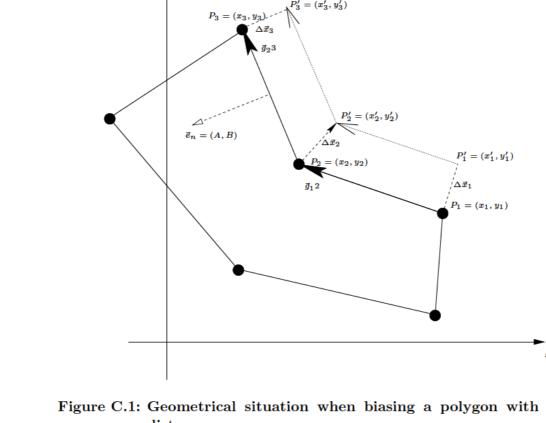

| $\mathbf{C}$ | Gen  | neral <b>A</b> | lgorithm for Polygon-Biasing                            | 137 |

| D            | Fro  | m Bolt         | zmann Distribution to Drift-Diffusion Current Equations | 140 |

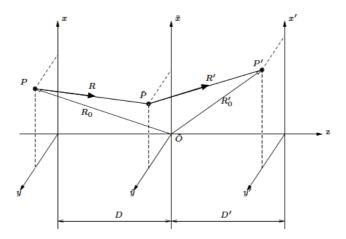

| ${f E}$      | Diff | raction        | n in Far Field Approximation                            | 142 |

|              | E.1  | Linear         | Approximation                                           | 142 |

|              | E.2  | Circul         | ar Aperture                                             | 146 |

|              | E.3  | Rectar         | ngular Aperture                                         | 151 |

|              | Bib  | liograp        | ohy                                                     | 154 |

|              | Owi  | n Publ         | ications                                                | 170 |

|              | Cur  | ricului        | m Vitae                                                 | 172 |

# List of Abbreviations and Acronyms

AAPSM Alternating Aperture Phase Shift Masks

American Standard Code for Information Interchange ASCII

**NMOS** n-type MOS **PMOS** p-type MOS

**BiCMOS** Bipolar & Complementary MOS

**BSIM** Berkeley Short-Channel IGFET Model

CDCritical Dimension

CIF Caltech Intermediate Format

**CMOS** Complementary MOS

CMPChemical Mechanical Polishing

$\mathbf{COG}$ Chrome on Glass DFT Design for Test

DOE Design of Experiments

dpm Defective Parts Per Million

$\mathbf{DRAM}$ Dynamical RAM  $\mathbf{DUT}$ Device Under Test

**EAPSM** Embedded Attenuated Phase Shift Masks

**ECAD** Electronic Computer-Aided Design

EDAElectronic Design Automation

**EEPROM** Electrically Erasable Programmable Read-Only Memory

Field-Effect Transistor FET **GDSII** Geometric Data Stream II

HTMHalf Tone Masks

HTMLHypertext Markup Language  $\mathbf{IC}$ Integrated Circuit . . .

I/OInput/Output . . .

ITRSInternational Technology Roadmap for Semiconductors

IVCurrent(I)-Voltage . . . LDDLightly Doped Drain

LOCOS Local Oxidation of Silicon LSL Lower Specification Limit . . .

MES . . . Manufacturing Execution System

MOS Metal-Oxide-Semiconductor

MPUMicroprocessor Unit . . . MPWMulti Product Wafer . . .

**MOSFET** MOS Field-Effect Transistor . . .

**NTRS** National Technology Roadmap for Semiconductors

NVMNon-Volatile Memory . . .

OPC Optical Proximity Correction . . . OTPOne Time Programmable Device

PCMProcess Control Monitor . . . PCIProcess Capability Index . . .

PERL Practical Extraction and Reporting Language

POR Process of Record . . . ppb Parts Per Billion . . . ppm Parts Per Million

RAMRandom-Access Memory . . . RIEReactive Ion Etching . . . RTARapid Thermal Annealing

SDTSingle Die Tooling . . .

SIMS . . . Secondary Ion Mass Spectroscopy

SLMScribe Line Monitor SMUSource Measure Unit . . . SOC . . . System On a Chip

**SPICE** Simulation Program with Integrated Circuit Emphasis . . .

SPRSimple Process Representation . . .  $\mathbf{SRAM}$ Static Random-Access Memory . . . TCAD Technology Computer-Aided Design . . . TEMTransmission Electron Microscopy

USL Upper Specification Limit . . .

$\mathbf{U}\mathbf{V}$ Ultraviolet . . .

**VBIC** Vertical Bipolar Intercompany Model

Very High Speed Integrated Circuit Hardware Description Language VHDL

Work in Process WIP

# List of Symbols

## Notation

Scalar

Vector

Unity vector in direction x

Unity vector in direction of vector  $\vec{n}$

$\vec{x} \cdot \vec{y}$ Scalar (in) product

$\vec{x} \times \vec{y}$ Cross product

Partial derivative with respect to t

$\nabla$ Nabla operator

$\nabla \vec{x}$ Gradient of  $\vec{x}$

Divergence of  $\vec{x}$

$\nabla \cdot \nabla = \nabla^2$ Laplace operator

Statistical average

$f(\vec{r}, \vec{k}, t)$ Distribution function

FOURIER transform and inverse FOURIER transform respectively

$J_n(\cdot)$ Bessel function of nth order

## Constants

$6.6260755 \times 10^{-34} \,\mathrm{Js}$ hPlanck's constant

Reduced Planck's constant  $h/(2\pi)$

$1.380662 \times 10^{-23} \,\mathrm{JK^{-1}}$  $k_{\rm B}$ Boltzmann's constant  $1.6021892 \times 10^{-19} \,\mathrm{C}$ Elementary charge q

$9.1093897 \times 10^{-31} \,\mathrm{kg}$  $m_0$ Electron rest mass

$8.8541878\times 10^{-12}\,\mathrm{AsV^{-1}m^{-1}}$ Dielectric constant  $\kappa_0$

$\sqrt{-1}$

# List of Figures

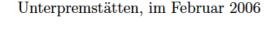

| 1.1  | inter wir o transistor density trend starting with the 4040 processor.                                         |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

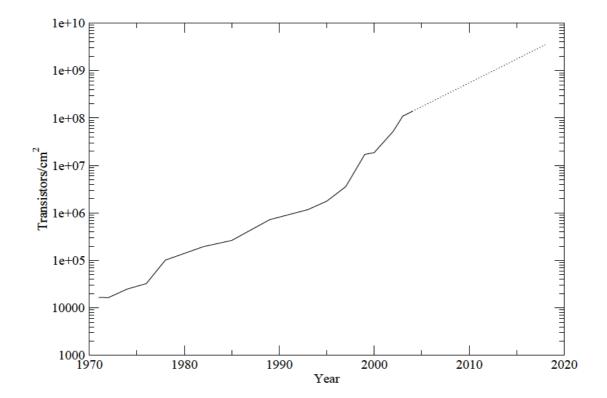

| 2.1  | Processing chain of integrated circuit production                                                              | 5  |

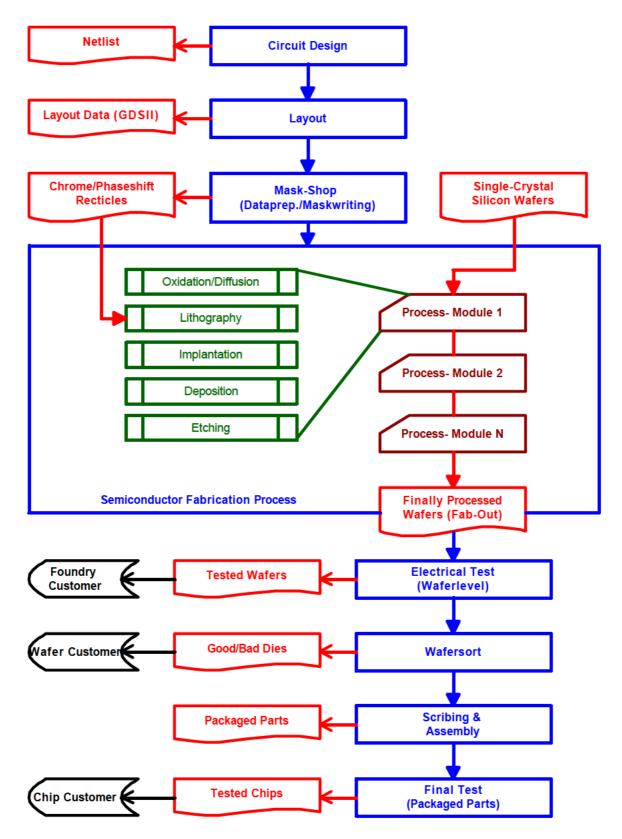

| 2.2  | Structure of the semiconductor process flow and its mirror image the TCAD simulation flow                      | 6  |

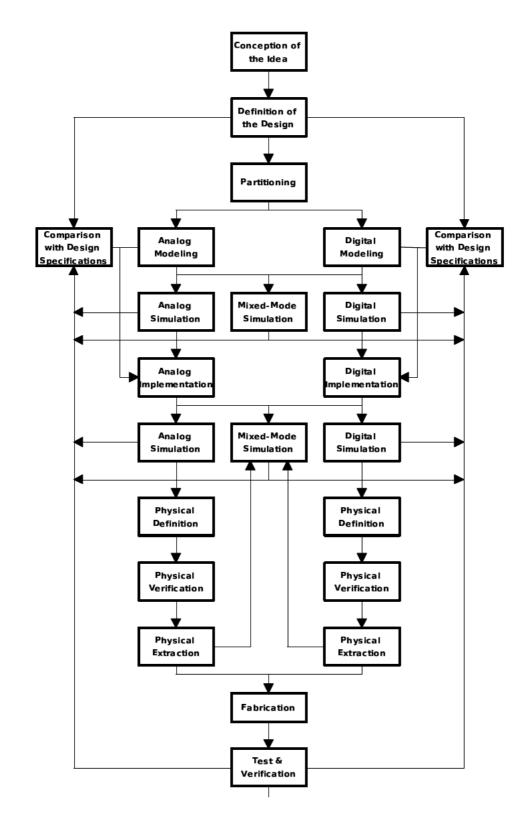

| 2.3  | Design flow of a mixed-signal design, comprising of an analog and a digital part                               | 8  |

| 2.4  | Basic imaging characteristics                                                                                  | 10 |

| 2.5  | Geometric situation in simple projection optical system                                                        | 11 |

| 2.6  | Light intensity distribution from a point source projected through a circular imaging lens                     | 12 |

| 2.7  | Rayleigh criterion for resolution of two point images                                                          | 12 |

| 2.8  | Expanded flow chart of the wafer fabrication cycle comprising one alignment step and the associated processing | 15 |

| 2.9  | Schematic view of the main components of the illumination system of a lithography tool                         | 16 |

| 2.10 | General schematic of an ion implantation equipment                                                             | 16 |

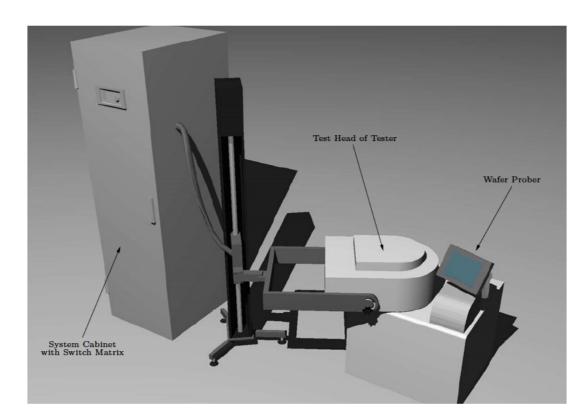

| 2.11 | An automated parameter tester including wafer prober for final wafer acceptance test                           | 19 |

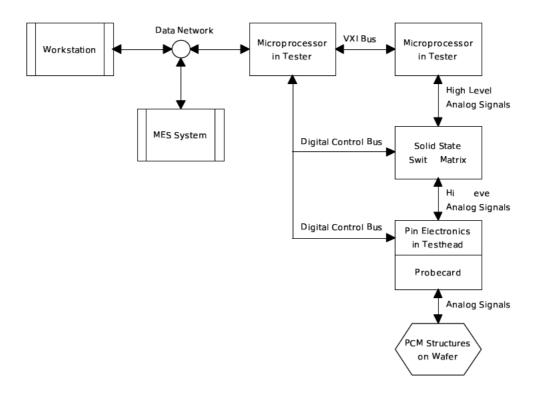

| 2.12 | Schematic overview of how the automated parameter tester system performs a test                                | 20 |

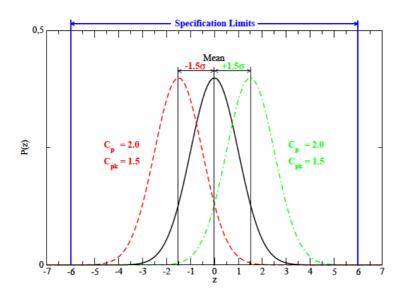

| 2.13 | Example for parameter distributions and resulting $\mathcal{C}_p$ and $\mathcal{C}_{pk}$ indices .             | 22 |

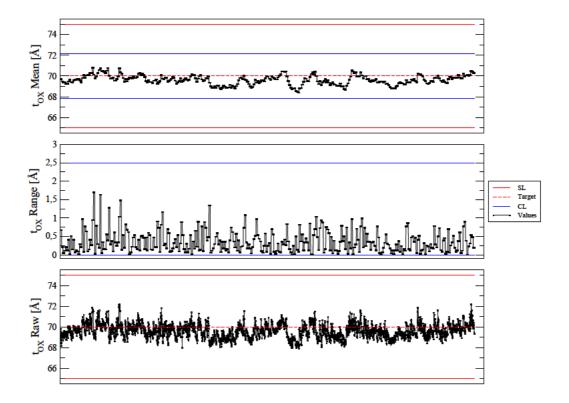

| 2.14 | Example for a SPC chart showing a time series of thickness measurements of the gate oxide thickness            | 23 |

|      |                                                                                                                |    |

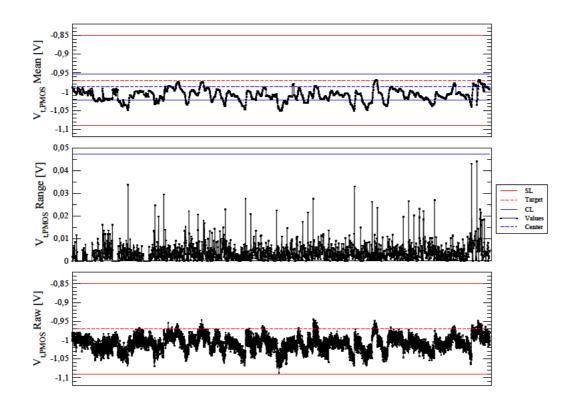

| 2.15 | Example for a SPC chart showing out-of-control events including the impact of corrective actions for the threshold voltage of a PMOS transistor | 24      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|

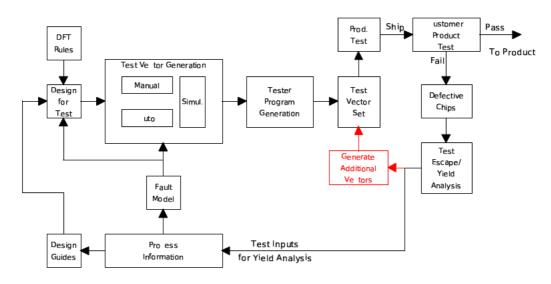

| 2 16 | The test process                                                                                                                                | 25      |

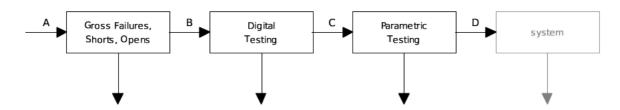

|      | The three phases of IC testing                                                                                                                  | 26      |

|      | •                                                                                                                                               |         |

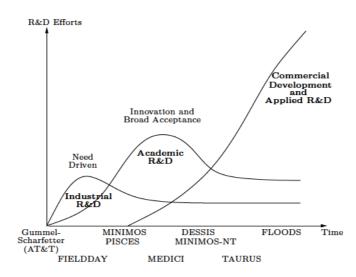

| 3.1  | Schematic time-line of TCAD R&D for device analysis                                                                                             | 31      |

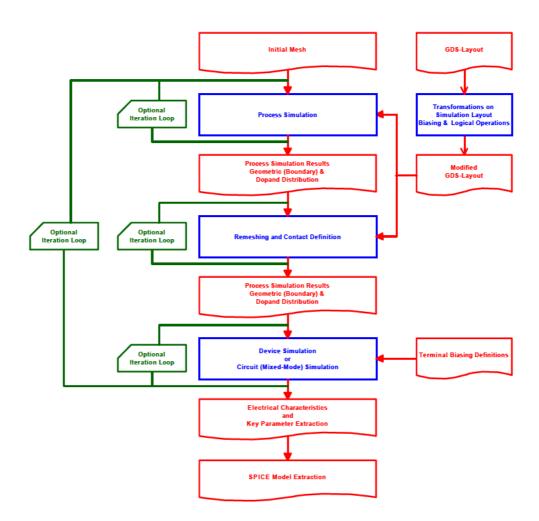

| 3.2  | TCAD work flow scheme showing possible iteration loops                                                                                          | 33      |

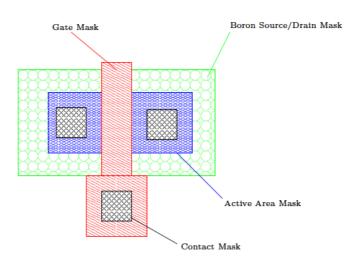

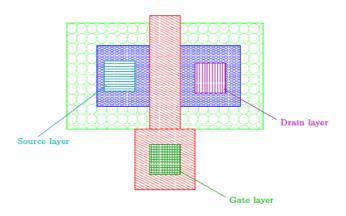

| 3.3  | Simple layout example of a PMOS transistor                                                                                                      | 34      |

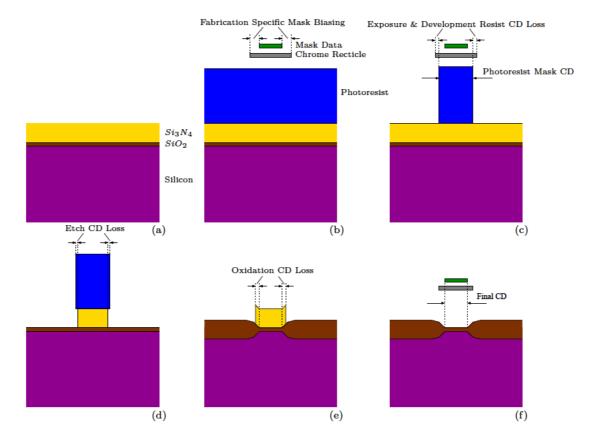

| 3.4  | Typical LOCOS module sequence                                                                                                                   | 35      |

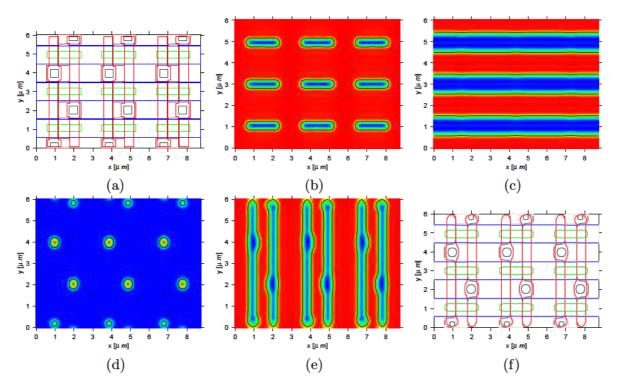

| 3.5  | Example for proximity effects in a part of an EEPROM cell                                                                                       | 36      |

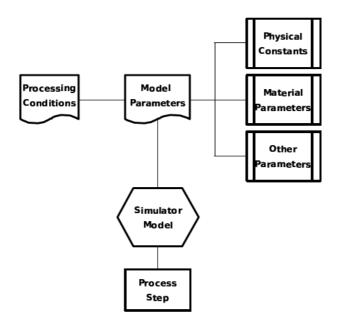

| 3.6  | Parameter classes for process simulation                                                                                                        | 38      |

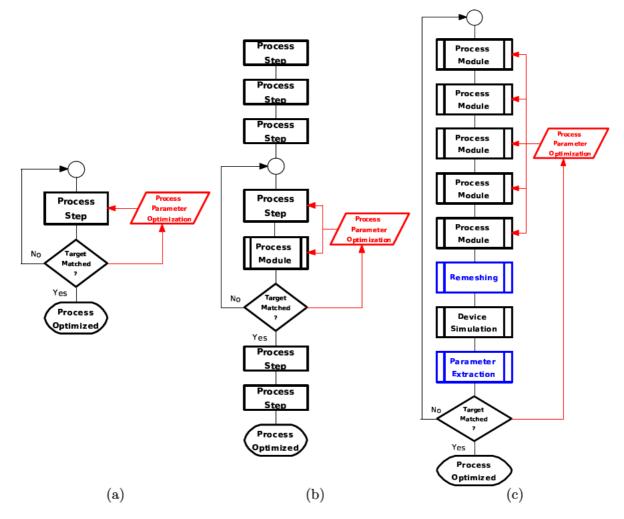

| 3.7  | Types of process simulation applications                                                                                                        | 39      |

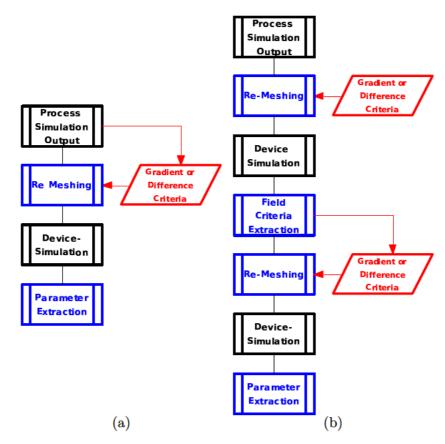

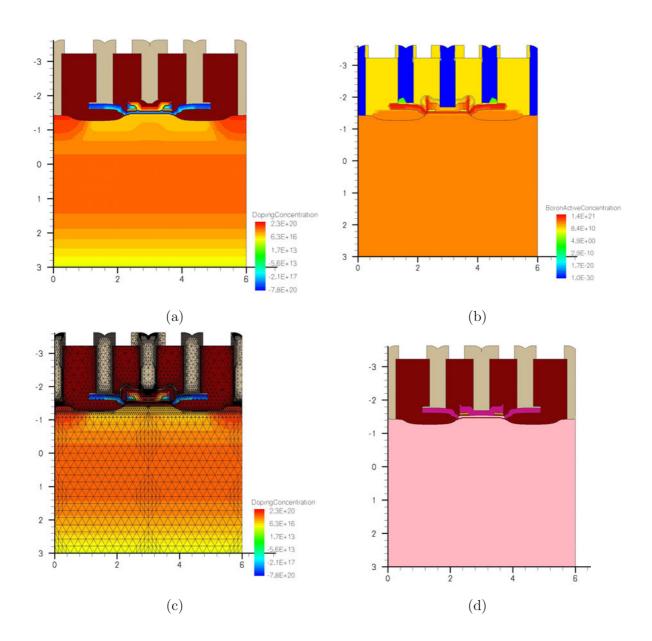

| 3.8  | Strategies for re-meshing structures generated by process simulation .                                                                          | 41      |

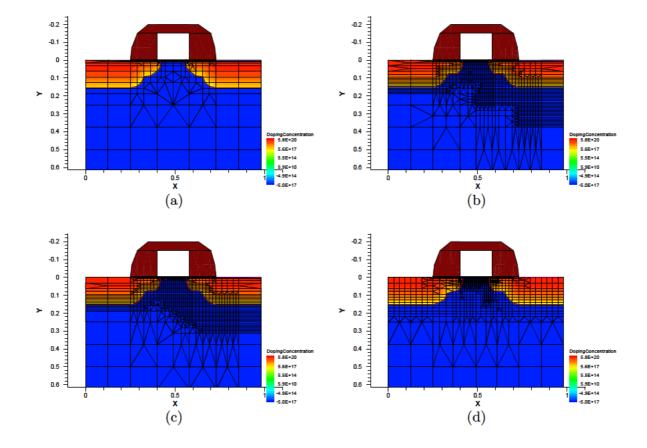

| 3.9  | Comparison of automatically and manually refined meshes                                                                                         | 42      |

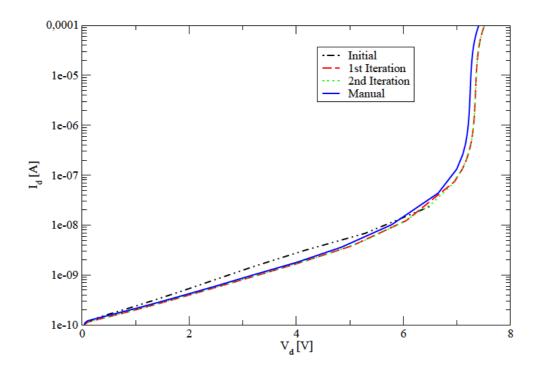

| 3.10 | Comparison of the different meshes in terms of device simulation results                                                                        | 43      |

| 3.11 | Simple layout example for contact naming of a MOS transistor                                                                                    | 44      |

| 3.12 | Example for a typical input structure for device simulation                                                                                     | 45      |

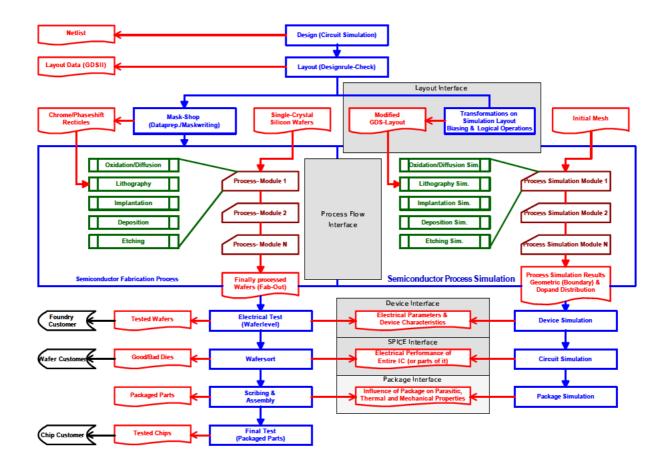

| 4.1  | Scheme of identified interfaces between TCAD and semiconductor fabrication                                                                      | 50      |

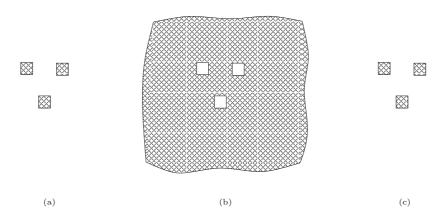

| 4.2  | Example of a dark field mask configuration                                                                                                      | 51      |

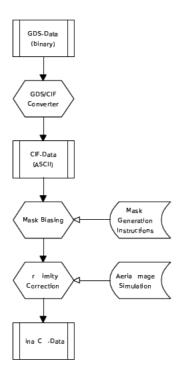

| 4.3  | Interface of layout-data to simulation mask-data                                                                                                | 53      |

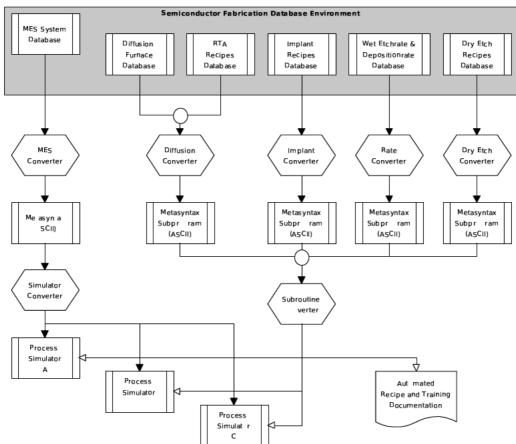

| 4.4  | Interface of process flow information to process simulation command files                                                                       | 54      |

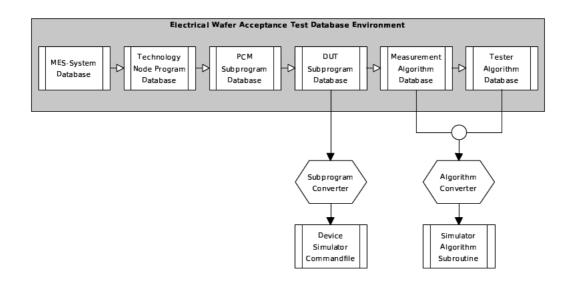

| 4.5  | Interface of electrical wafer acceptance test information to device simulation command files                                                    | 56      |

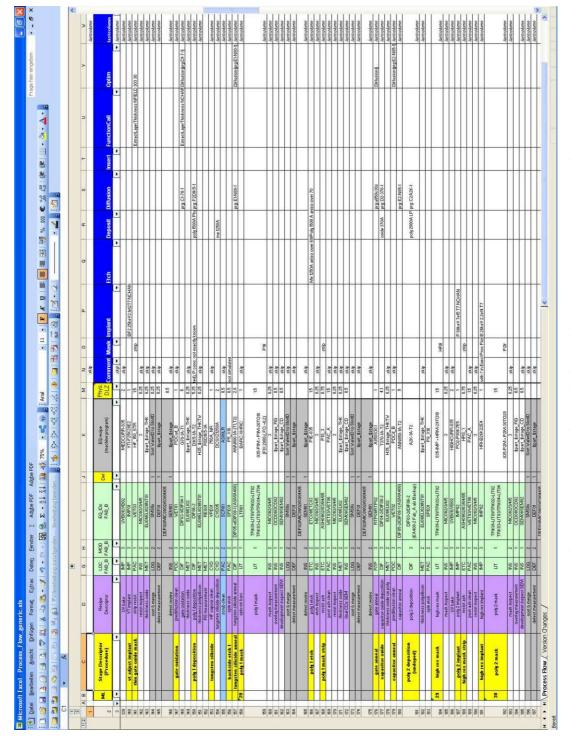

| 5.1  | Screen-shot of EXCEL-Sheet description for research&development short-loops or semiconductor processes in development                           | -<br>60 |

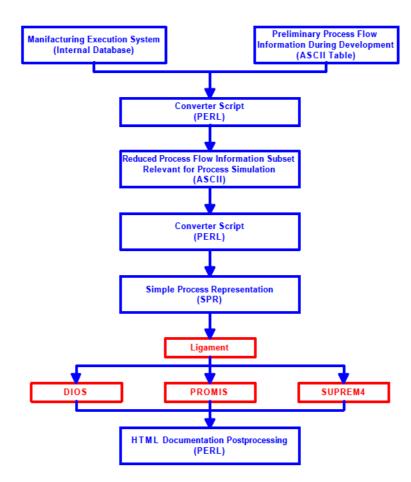

| 5.2  | Conversion scheme for semiconductor process flow information                                                                                    | 61      |

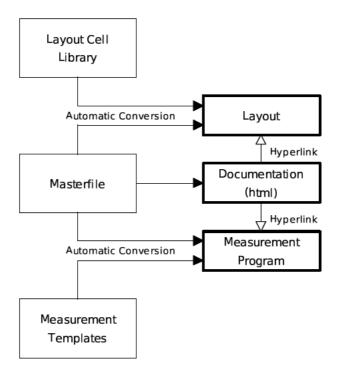

| 5.3  | Electrical test program conversion work-flow                                                                                                    | 65      |

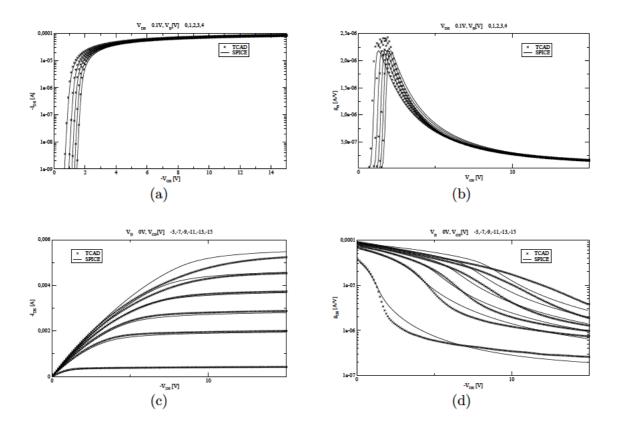

| 5.4  | Simulated characteristics of a simulated high voltage PMOS driver compared to SPICE model fit                                                   | 70      |

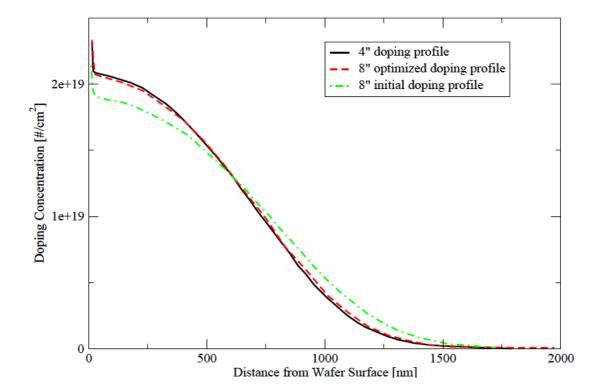

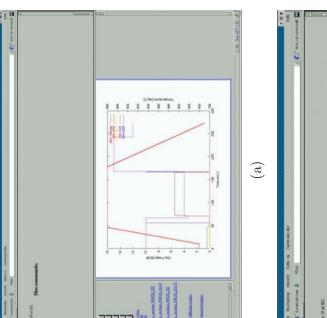

| 6.1  | Doping profile for a 4" diffusion furnace compared to a 8" diffusion furnace before and after optimization                        | 72 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

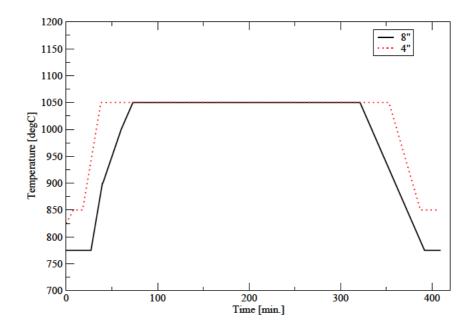

| 6.2  | Graphical comparison between the 4" and 8" diffusion recipe for a typical p-well diffusion                                        | 73 |

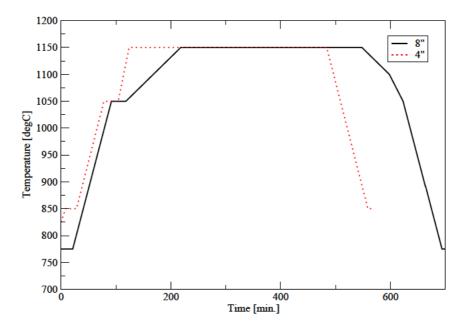

| 6.3  | Graphical comparison between the 4" and 8" diffusion recipe for a typical n-well diffusion                                        | 73 |

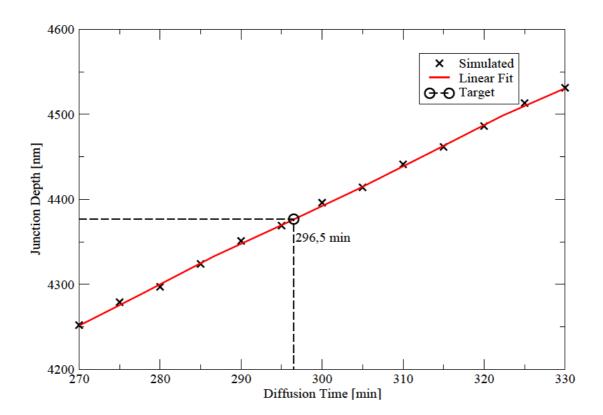

| 6.4  | N-well junction depth over time of annealing step                                                                                 | 74 |

| 6.5  | Examples demonstrating the capabilities of automated process flow documentation                                                   | 76 |

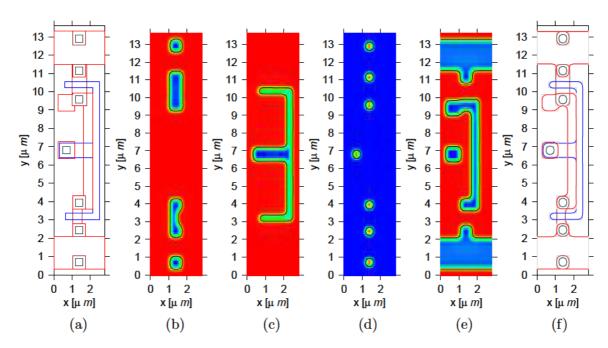

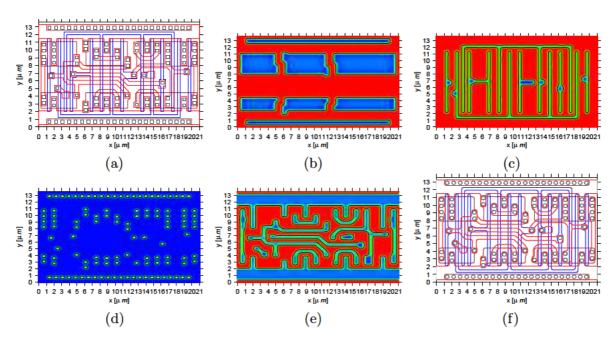

| 6.6  | Proximity correction simulation of digital inverter layout                                                                        | 77 |

| 6.7  | Proximity correction simulation of big digital cell                                                                               | 78 |

| 6.8  | Comparison of the interconnect shape of a three-dimensional structure of a big digital cell with and without proximity correction | 79 |

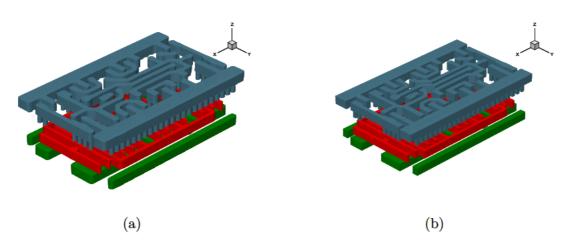

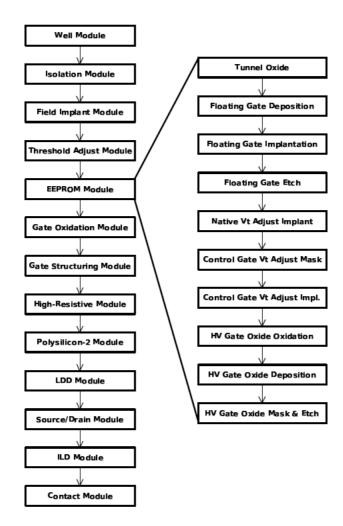

| 6.9  | Block diagram of the front-end silicon foundry process flow                                                                       | 80 |

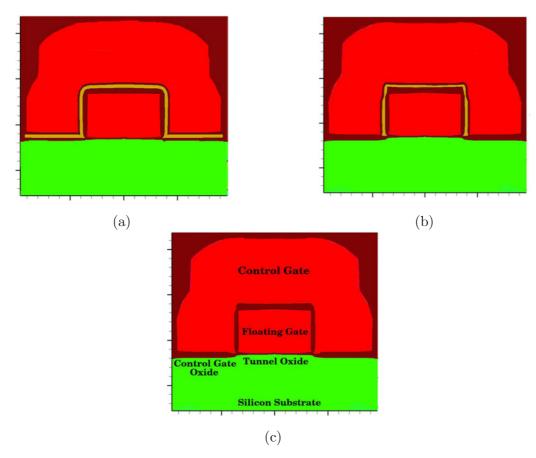

| 6.10 | Comparison of the three different EEPROM cell architectures                                                                       | 81 |

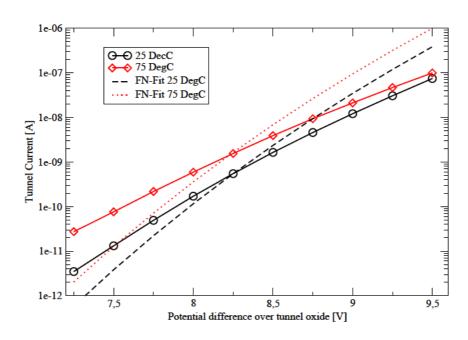

| 6.11 | Comparison of simulated and measured tunnel currents through the tunneling oxide                                                  | 82 |

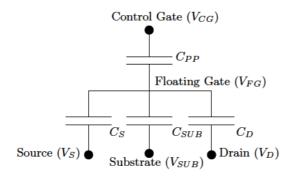

| 6.12 | Capacitive equivalent circuit of the EEPROM cell                                                                                  | 82 |

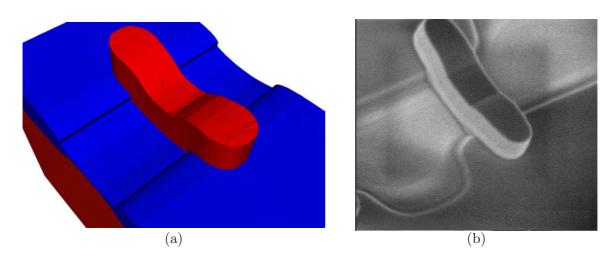

| 6.13 | EEPROM cell after floating-gate mask etch                                                                                         | 83 |

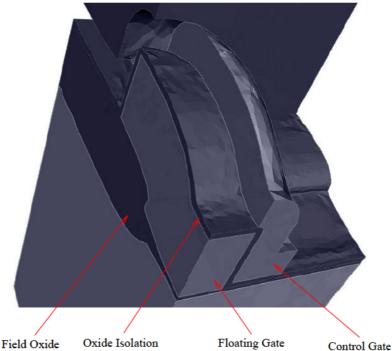

| 6.14 | Structure of the EEPROM memory cell generated by three-dimensional process simulation (one quarter of the cell is shown)          | 84 |

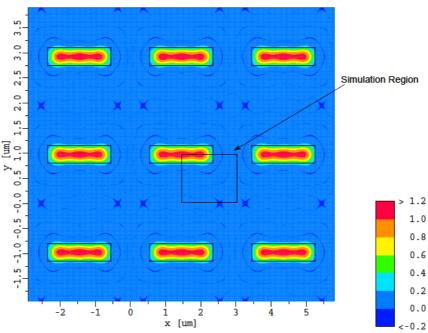

| 6.15 | Aerial image simulation result of the floating gate mask of a $3\times3$ EEPROM cell array                                        | 85 |

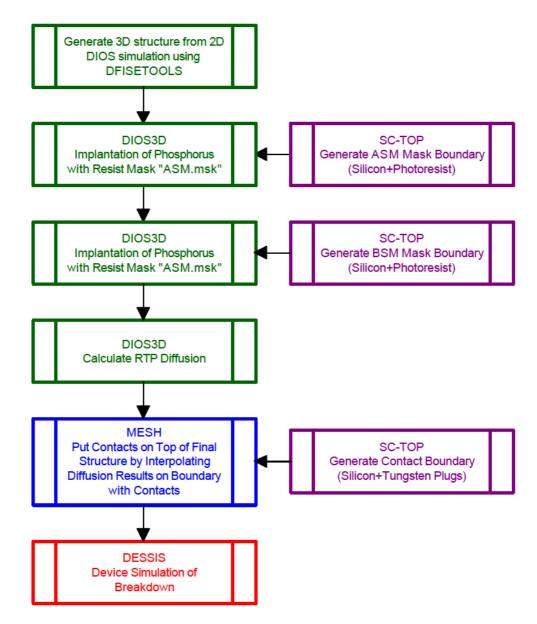

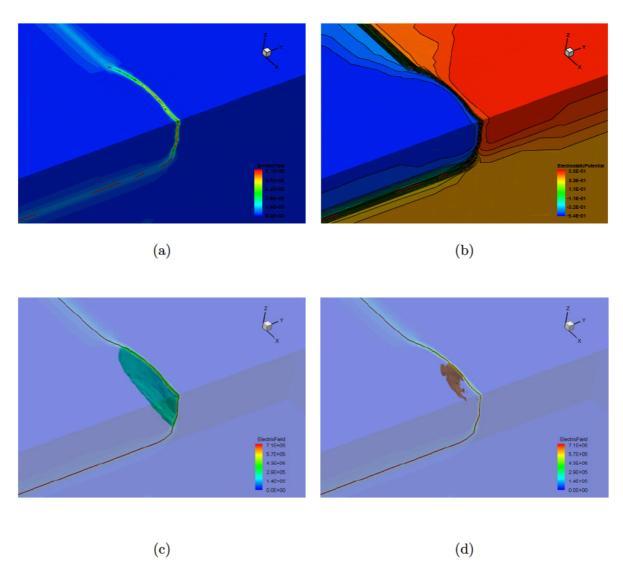

| 6.16 | Schematic flow for coupled three-dimensional process and device simulation                                                        | 87 |

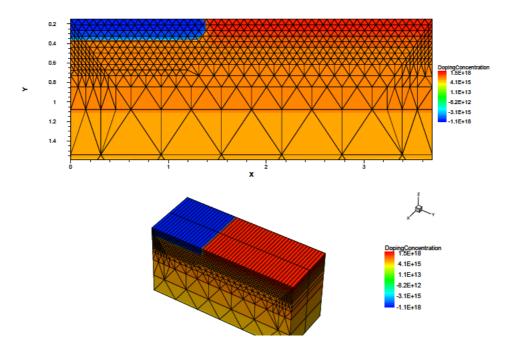

| 6.17 | Two-dimensional initial structure and resulting three-dimensional mesh after conversion into three dimensions                     | 88 |

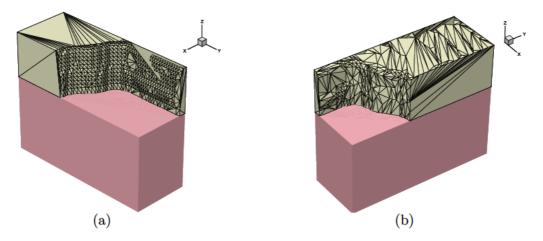

| 6.18 | SC-TOP simulations of Zener diode implantation masks                                                                              | 88 |

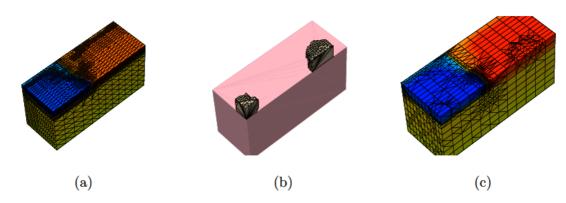

| 6.19 | Generation of Zener diode mesh suitable for device simulation                                                                     | 89 |

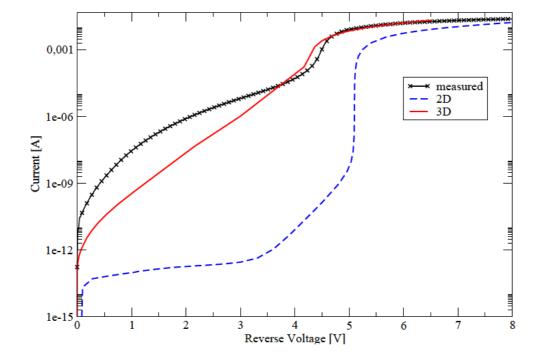

| 6.20 | Comparison of two-dimensional and three-dimensional device simulation results with measured characteristics of PIN-diode          | 89 |

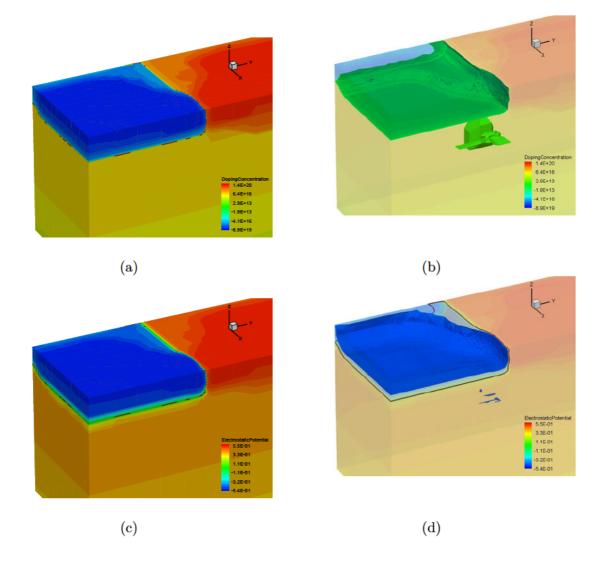

| 6.21 | Doping and potential distribution inside the zener structure                                                                      | 90 |

| 6.22 | Electrical field distribution inside zener structure                                                                              | 91 |

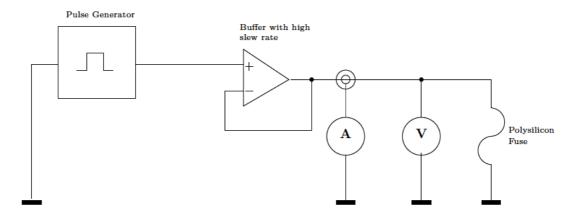

| 6.23 | Schematic of the Polysilicon fuse measurement                                                                                     | 93 |

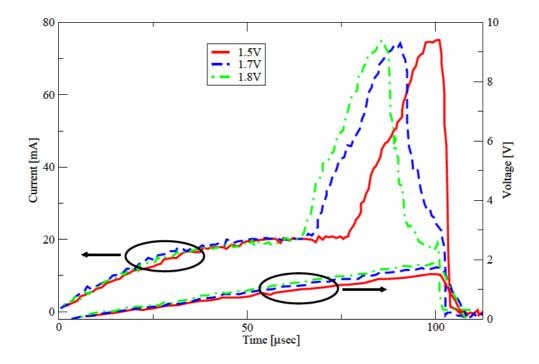

| 0.24 | function of time                                                                                                            | 93  |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

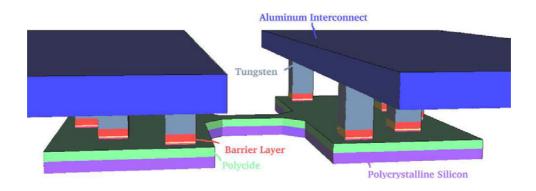

| 6.25 | Fuse device structure showing the variety of included materials                                                             | 94  |

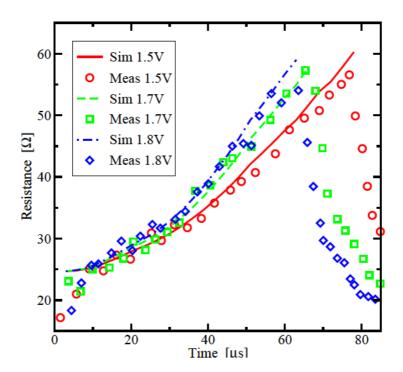

| 6.26 | Comparison of measured and simulated polysilicon fuse resistance as a function of time                                      | 96  |

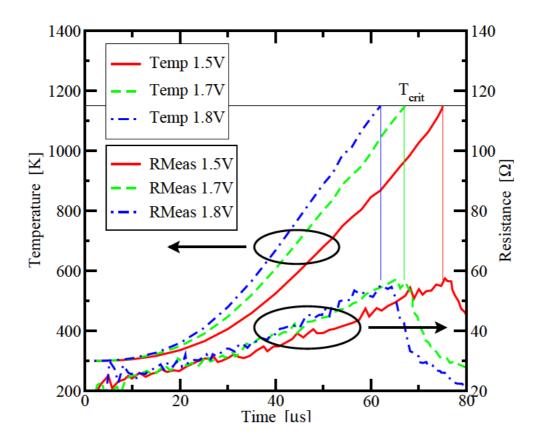

| 6.27 | Comparison of the simulated temperature and measured polysilicon fuse resistance showing the extracted critical temperature | 97  |

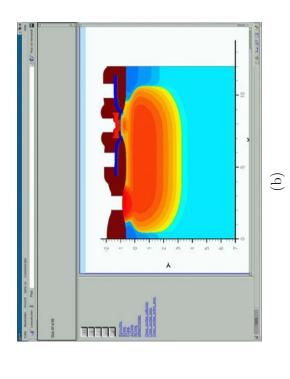

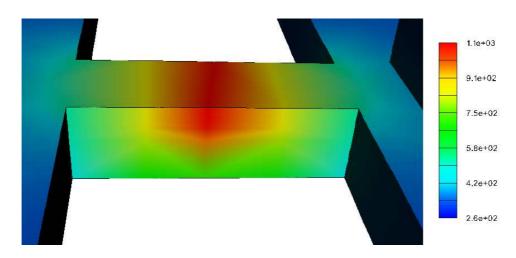

| 6.28 | Temperature distribution in the polysilicon fuse interconnect structure at $65\mu\mathrm{s}$ and $1.7\mathrm{V}$            | 98  |

| B.1  | A sample CIF "wire" statement                                                                                               | 109 |

| B.2  | A sample CIF "polygon" statement                                                                                            | 110 |

| В.3  | The transformations of a CIF "call"                                                                                         | 111 |

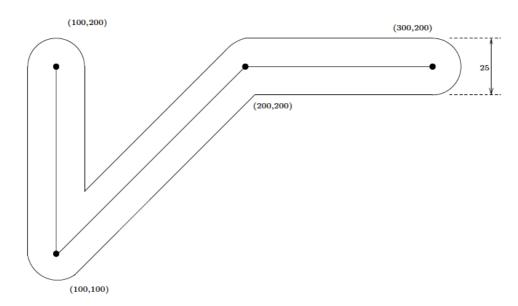

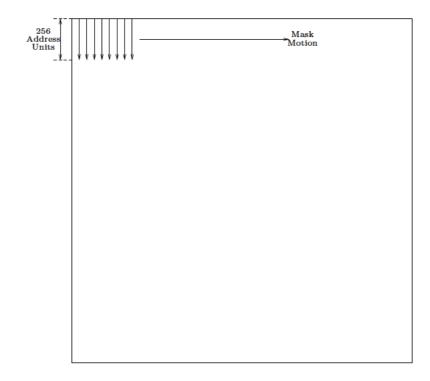

| B.4  | EBES raster motion, actual mask making sweeps out 256 rows as it advances horizontally                                      | 133 |

| B.5  | EBES parallelogram example                                                                                                  | 135 |

| B.6  | EBES trapezoid types                                                                                                        | 136 |

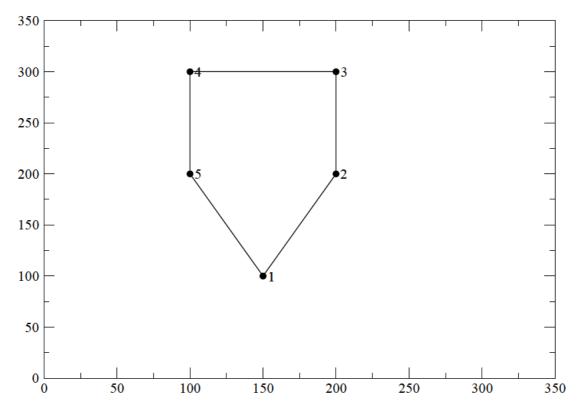

| C.1  | Geometrical situation when biasing a polygon with a given distance                                                          | 138 |

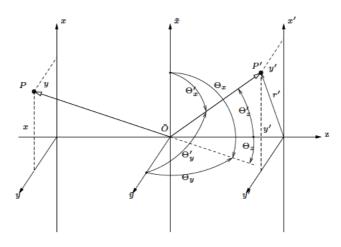

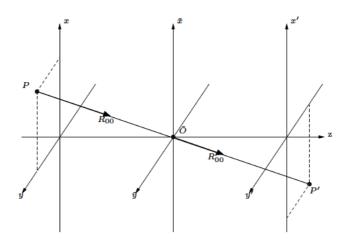

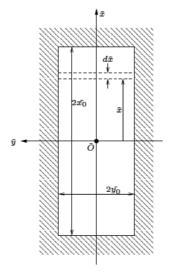

| E.1  | Standard geometry of theory of diffraction                                                                                  | 142 |

| E.2  | Viewing angles of source point and projection point as seen from the center of the aperture                                 | 143 |

| E.3  | Direct light propagation through aperture                                                                                   | 146 |

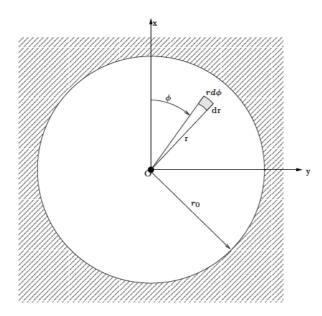

| E.4  | Coordinate system in a circular aperture                                                                                    | 147 |

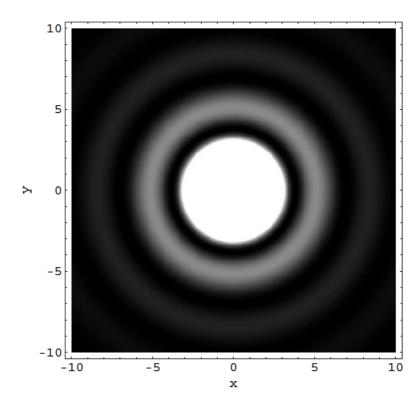

| E.5  | Airy-disk with rings                                                                                                        | 150 |

| E.6  | Coordinate system in a rectangular aperture                                                                                 | 150 |

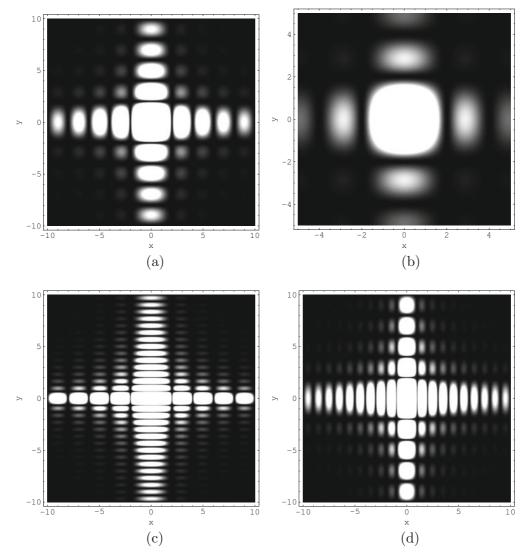

| E.7  | Comparison of different intensity distributions after diffraction at different shapes of aperture                           | 153 |

# List of Tables

| 2.1 | Definitions for important wavelength nodes in itnography 19                                            |

|-----|--------------------------------------------------------------------------------------------------------|

| 2.2 | Examples for typical lens configurations for deep sub micron technology nodes                          |

| 2.3 | Overview over the three different parameter classes                                                    |

| 3.1 | Examples for current level of details in the description of semiconductor process steps                |

| 4.1 | Example of mask generation instruction table including biasing and CD (critical dimension) information |

| 5.1 | Parameters for threshold measurement routine                                                           |

| 6.1 | Maximum allowable temperature ramp rates for vertical 8" furnaces . 71                                 |

| 6.2 | Extracted capacitances within the EEPROM memory cell 84                                                |

| 6.3 | Parameters of electrical and thermal conductivity for materials used in the polysilicon fuse structure |

| 6.4 | Calculated differences of the selected parameters to the nominal implant set (1,1,1) in percent        |

| B.1 | Typical user extensions to CIF                                                                         |

| B.2 | GDS II header record types                                                                             |

| В.3 | GDS II element record types                                                                            |

| B.4 | Contents statements allowed in EDIF                                                                    |

| B.5 | Interface statements allowed in EDIF                                                                   |

|     |                                                                                                        |

'... The complexity for minimum component costs has increased at a rate of roughly a factor of two per year.

Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years.

That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000.

I believe that such a large circuit can be built on a single wafer.

Gordon E. Moore, 1965

### Chapter 1

# Introduction

Cemiconductor technology and industry has enormously advanced in the past decades. Start-Oing from a plastic triangle, a slab of germanium, some gold foil and gold contacts (the first bipolar transistor in 1947), as of 2004 the typical transistor density per circuit is around 140 million transistors/ $cm^2$  for MPU (micro processor unit) applications, doubling every year (Moore's Law [2]). This trend is shown in Figure 1.1 starting with the 4040, the first Intel Processor in 1971. Semiconductor Industry is the main driving force for technology innovation and "New Economy" markets. The ongoing development of faster integrated circuits with higher device density has led to highly complex and sophisticated products which are widely accepted by society. A modern integrated circuit cannot be developed without the massive use of computer aided design (CAD) in any step of the complex flow from the idea to the final product. This work concentrates on technology computer aided design (TCAD) [5] and its integration into the semiconductor fabrication process flow. The use of TCAD is twofold: Firstly it models the complex flow of semiconductor fabrication steps ending up with detailed information on geometric shape and doping profile distribution of a semiconductor device in scope (like CMOS- or Bipolar-Transistors) ⇒ Process TCAD-Simulation. Secondly it uses the information of the first step to predict the device characteristics of semiconductor devices leading to circuit simulation models as implemented in any circuit simulator like PSPICE [6], ELDO [7], SPECTRE [8] etc.  $\Rightarrow$  Device TCAD-Simulation. The setup of such a simulation methodology requires an almost completely documented semiconductor fabrication process flow including such fabrication details like angle of incidence of ions implanted in ion implantation process steps, or etch rate distribution as a function of the local angle of the etched layer surface. Any modern semiconductor fabrication facility maintains such documentation to an extremely high detail level, but commercial TCAD simulation software like Synopsys [9] or Silvaco [10] Tools need this information in a very specialized format [11] which cannot be directly deduced from the standard process flow documentation. The traditional way of setting up the process- and to some extent also the device TCAD-simulation framework is, entering it by hand, which is of course a source of numerous errors. This work proposes a new methodology with the main target to automate this conversion process to a high extent.

Chapter 2 describes the overall chain of processes, how integrated circuits are fabricated. An overview with respect to the related simulator tools is given.

Figure 1.1: Intel MPU transistor density trend starting with the 4040 processor [3]. The dashed line shows the ITRS chip size model [4]

Chapter 3 concentrates on the detailed simulation methodologies to model the IC (Integrated Circuit) fabrication.

Chapter 4 identifies the interfaces between the fabrication process and simulation. It outlines the detailed structure of the interfaces. A comprehensive overview over the interactions in this integrated system is given as well.

Chapter 5 provides the detailed description of how this interfaces are implemented.

Chapter 6 demonstrates the strengths of such a structured and integrated approach with a couple of cases in a real semiconductor fabrication environment.

Finally, Chapter 7 briefly summarizes this work with some conclusions and an outlook.

'... The bourgeoisie has stripped of its halo every occupation hitherto honoured and looked up to with reverent awe. It has converted the physician, the lawyer, the priest, the poet, the man of science, into its paid wage labourers.'

Karl Marx and Friedrich Engels, 1888

# The Processing Chain in Semiconductor Manufacturing

### 2.1Overview

The semiconductor industry is starting from the product idea the following sequential steps Loccur in a standard integrated circuit development and production flow [12].

- 1. Development: Starting from the product idea, the electronic contents of the overall system are developed, leading into a schematic of the electronic circuitry. For digital circuitry this development process is similar to writing a software program by using Very High Speed Integrated Hardware Description Language (VHDL) as a abstract description of the digital block. The development of a digital block starts with the specification (operation and timing) and the subsequent description of this specification via a model in VHDL.

- 2. Design: The integrated circuit is designed starting from the schematic, and taking into account the special demands of integrated circuits (crosstalk, common substrate, etc.). It is now standard to use ECAD tools to simulate the behaviour of a design as an integrated circuit by using detailed circuit simulation models and design rules, which are specific to a process family (technology node) [13],[14].

- 3. Layout: The resulting integrated circuit is drawn as a layout on the specific layers which are given by the semiconductor process family (technology node). The combination of multiple layers, like implantation masks and etch masks, define the shape and functionality of the electronic devices in the integrated circuit [15], [16], [17].

- 4. Mask-Shop: The layout is post processed to take into account process induced size variations (layer biasing) and constraints on combination of layers (logical combination). The physical mask layers are written from this data by using laser- [18] or e-beam [19] equipment.

- 5. The wafer start material is released at the beginning of the process flow into fabrication [20]. In the following these wafers are subject to numerous single process steps like

ion-implantation, deposition and etching of semiconductor, dielectric, and metallic materials, furthermore diffusion of dopants, and oxidation and lithography to structure deposited layers using the previously fabricated mask reticles.

- 6. After leaving the fabrication the now functional integrated circuits are tested electrically. Firstly on single device level on process control monitors (PCM's), secondly on full device level (wafer sort). These tests select the functioning parts for further processing.

- 7. Scribing into pieces and packaging of the single circuits.

- 8. Electrical functionality test of the packaged pieces.

The overall processing chain is shown in Figure 2.1.

The ECAD simulation tools in Subject 1, Subject 2, and Subject 3 are already closely integrated into the development chain [21] and are therefore very efficient.

Packaging simulation is not subject to this work, however, tools [22], [23] are used to analyse new packages with respect to electromagnetic field, stress, and self heating.

For Subject 4 to Subject 6 good simulation solutions exist for the single process step (e.g. SIGMA-C or PROLITH for lithography and mask fabrication step simulation, TCAD Tools from Synopsys and Silvaco for the process- and device-simulation steps), which are sufficient for most of the two-dimensional process- and device-simulation applications.

However, the set-up of these TCAD-simulators is highly complicated and time consuming. Changes in fabrication procedures like parameter optimization of process conditions are not reflected in simulation with the traditional way of defining this set-up by hand. Therefore the simulation flow definitions become asynchronous to the semiconductor fabrication very quickly.

The main concept to be considered is to match the simulation methodology as closely as possible to the fabrication methodology in an automatic (or at least semi-automatic) way. The resulting work flow and the main application areas for TCAD integration into fabrication can be seen in Figure 2.2.

In the following the main aspects of the parts of this implementation are outlined.

### 2.2Design

As mentioned above the integration between design of integrated circuits and their simulation is already very efficient. The circuit design is almost exclusively performed at workstations by using a sophisticated set of software tools to model the behaviour of the schematic to be implemented as integrated circuit on silicon wafers. To enable a high degree of modeling accuracy an extensive set of characterization of the available devices on silicon has to be done in advance. This task is called process and device characterization (PDC). It will be shown in Chapter 4 how TCAD may support this task especially for the development of new process technologies. PDC is generating the model parameters for the SPICE models used by circuit designers. The consistency and accuracy of these SPICE models is absolutely mandatory for enabling designs with the envisaged electrical specifications. The generation of the SPICE models is carried out after the

Figure 2.1: Processing chain of integrated circuit production

Figure 2.2: Structure of the semiconductor process flow and its mirror image the TCAD simulation flow

semiconductor process freeze during development of new process flows or occasionally, if some major semiconductor process change occurred. To reflect shifts or drifts in the semiconductor device performance as well as the statistical variations of the process technology a feedback loop is established between electrical test and the SPICE models. This feedback is implemented by using the pass/fail limits of the electrical test to supply worst/case conditions to the designer. There are numerous new approaches for simulating statistical fabrication fluctuations within the ECAD environment labeled under the term DFM (design for manufacturability) [24],[25], however, the details are outside of the scope of this work. By using SPICE models, EDA (Electronic Design Automation) design tools from companies like Mentor [26], Cadence [27], or Agilent [28] are able to simulate the behaviour of the schematic entered by hand or imported with net lists. A typical design flow is shown in Figure 2.3.

### 2.3Layout

After finalization of the behavioural modeling of the schematic, the design is layed out into a complex combination of masks. There are several basic building blocks of the layout. The digital library consists of predefined highly optimized (in terms of speed and area) digital cells which are connected automatically by metal interconnect layers during place and route.

Memory blocks (SRAM, DRAM, OTP or NVM) are normally placed by memory generators automatically. The most demanding building block for a designer is the analog part of a design, where linearity, accuracy, and matching of the single devices play an important role. Especially the layout of this block may have an important influence on the subsequent performance of the analog part of the design by introducing additional parasitics between the single devices in the silicon (e.g. leakage). High frequency or timing dependent applications can be strongly influenced by the RLC-network of the interconnects between the analog components. Therefore, after layout a parasitic extraction has to be performed, where the RLC-network of the interconnects is extracted from the layout and this extracted values are put into the overall schematic of the integrated circuit in an additional circuit simulation run. Finally the bonding pads are placed to provide the ports of the design, where the package bond wires are connected to. There are several different pad types:

- 1. Digital I/O pads: These pads are optimized for the connection to and from the digital logic. The operating voltages range from 5V down to 1.3V for low power logic.

- 2. Analog I/O pads: These pads take special measures to provide different voltage levels depending on the process technology [29] (e.g. for high voltage drivers analog outputs have to support higher voltages than 5V).

- 3. VDD and VSS pads: These pads are for the supply of the chip.

The main difference of the above types is in their ESD (electrostatic discharge) protection concept. Because the devices connected to the pad types are very different (digital cells, drivers or power buses), the ESD protection concept has to account for this independently. A special subset of the Analog I/O pads is frequently termed as RF pad which provides a reduced amount of interconnect parasitics for critical analog high frequency applications. After finalization of the layout the integrated circuit may be clustered together with other circuits, if multiple products

Figure 2.3: Design flow of a mixed-signal design, comprising of an analog and a digital part

are processed together in one batch in an MPW (multi product wafer batch). For high volume products a SDT (single die tooling) is prefered, where only one product is processed in a wafer batch. The tape out marks the transfer of the layout data to the mask shop for generation of the lithography masks for processing. The data can be transferred in different formats like CIF, GDSII, EBES, or EDIF which are described in more detail in Appendix B.

### 2.4 Mask Generation

### Introduction 2.4.1

A fundamental requirement for almost all useful semiconductor devices is the definition of patterned elements. The main stream technology choice for patterning has been optical lithography. Up to the early 70's lithography was done as a contact printing process in which blue or near UV light was passed through a photo mask directly onto a photo resist coated semiconductor substrate [30]. This shadow imaging process has been described in many research publications and handbooks [31], [32]. Beginning in the early 80's a new class of projection exposure tools, known as steppers, was introduced [33]. For the first time the pattern definition imaging on the semiconductor wafers was performed one chip at a time in a step-and-repeat fashion. Most stepper systems employed a reduction projection lens to ease the fabrication difficulty of the photo mask and to improve the overall precision and accuracy of the overlay of patterns on the wafer. Even more recently a combination of the earlier scanning approach with the step-andrepeat approach was created [34]. The step-and-scan approach has spread rapidly throughout the lithography tool industry, and is used for critical layers (like gate, metallization and contact layers) at the 250nm node and below [35]. Until the mid 90's all optical photo masks have been chrome on glass (called COG-photo masks) [36], also called binary photo masks. Starting from the 350nm node significant innovations in binary masks such as OPC (optical proximity correction) [37] and AAPSM (alternating aperture phase shift masks) [38] were introduced which improved the resolution capability of binary photo masks. A second approach besides the binary photo masks then emerged as EAPSM (embedded attenuated phase shift masks) [39] also called HTM (half tone masks).

### 2.4.2 **Imaging Basics**

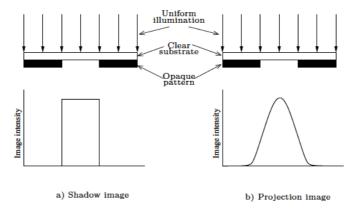

Lithography is based on replicating the pattern on a photo mask into resist covered wafers. In an ideal case without degradation in the imaging process, a simple copy of the mask pattern would result, as shown in Figure 2.4 a.

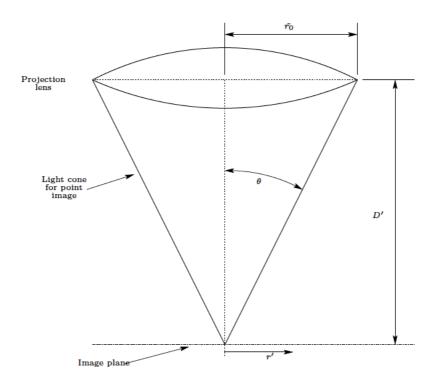

However, in a projection process the imaging is always subject to degradation from diffraction and from imperfections in the projection system. An example of the image from a diffractionlimited projection system is shown in Figure 2.4 b. The spreading of the image profile results from the wave nature of light, and it is this property that limits the resolution capability of optical imaging systems. In an imaging lens system with a circular aperture of radius  $\tilde{r_0}$  and imaging distance D', the image intensity resulting from a point source can be described by an

expression containing a first order Bessel function,

$$I'(x) = I(0) \left(2\frac{J_1(x)}{x}\right)^2 \tag{2.1}$$

where  $x = \frac{2\pi \tilde{r_0}r'}{D'\lambda}$  and r' is the distance in the image plane from the geometrical image point.  $\lambda$ is the wavelength of the monochromatic light source. A detailed deduction of this expression is given in Appendix E.2. The fraction  $\frac{r_0}{D'}$  given by

$$\frac{\tilde{r_0}}{D'} = \tan \theta \cong \sin \theta \quad \text{for} \quad \theta \ll$$

(2.2)

equals the numerical aperture NA defined by

$$NA \equiv n\sin\theta \tag{2.3}$$

with n as the refractive index of the medium behind the aperture or lens. Therefore the expression for x can be further simplified to  $x = 2\pi \rho \frac{NA}{\lambda}$ . For air as medium  $(n \approx 1)$  a simplified description of NA is given in Figure 2.5 as  $NA = \sin \theta$

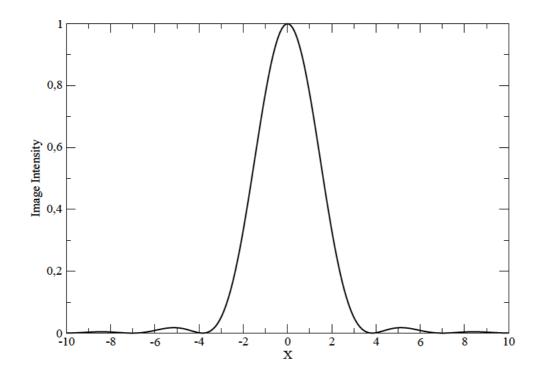

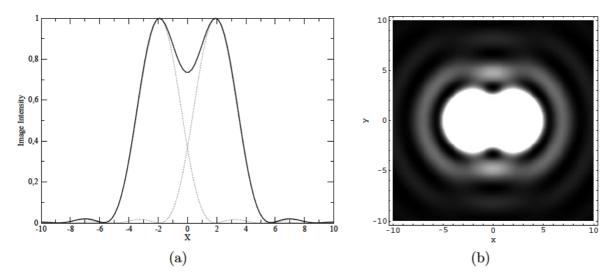

This light intensity distribution is known as the AIRY pattern, after G.B. AIRY who first derived it in 1835 [40]. In addition to the general shape of the curve, shown in Figure 2.6, the first zero value is of interest. At about  $x = 0.612\pi$  occurs a intensity minimum and an intensity maximum at  $x = 0.822\pi$ .

Resolution is defined as the ability to distinguish components of an object or a group of objects. The resolution capability of astronomical telescopes was studied in detail by LORD RAYLEIGH in the 19th century [41]. He defined the limit of resolution for a telescope as the angular separation between two stars when the peak of the AIRY intensity pattern from one star coincided with the first minimum of the AIRY intensity pattern for the other star. This leads to the well-known Rayleigh condition for angular resolution

$$NA = \sin \theta = 0.61 \frac{\lambda}{\tilde{r}_0} \tag{2.4}$$

Figure 2.4: Basic imaging characteristics (a) Ideal shadow imaging; (b) Diffraction-broadened projection imaging

Figure 2.5: Geometric situation in simple projection optical system

where  $\tilde{r_0}$  is again the radius of the imaging objective aperture. A sketch of the RAYLEIGH resolution condition is shown in Figure 2.7. Note that the intensity at the midpoint between the image peaks is reduced to about 78% of the peak intensity, which provides discernible separation, but not with high contrast between the bright and dark regions.

While the analogy of astronomical imaging to photo lithography is not completely quantitative, some key observations can be made. There is a limit to resolution for any given optical projection system, and it is not possible to resolve arbitrarily small or closely spaced features. It is also apparent that the resolution can be improved by using a smaller wavelength of the exposure light, and the resolution can be improved by making the projection system aperture larger. In practical lithography the RAYLEIGH condition is typically restructured into the "RAYLEIGH equation"

$$resolution = k_1 \frac{\lambda}{NA} \tag{2.5}$$

where NA is the numerical aperture of the projection system and  $k_1$  is a constant in the order of 0.4-0.8. There is no rigorous optical definition for the constant  $k_1$ , and it is generally used as a qualitative descriptor of the overall lithography process capability. More details on the RAYLEIGH equation are given in Table 2.1. Table 2.2 shows the numeric aperture, the resolution, and the depth of focus for the most important wavelengths in lithography.

This common description of resolution capability is closely related to the AIRY pattern described above. In particular, the first minimum of the AIRY pattern occurs at about  $r' = 0.61 \frac{\lambda}{NA}$ , and

Figure 2.6: Light intensity distribution from a point source projected through a circular imaging lens. The variable x on the horizontal axis is defined in the text

Figure 2.7: RAYLEIGH criterion for resolution of two point images in (a) 1D and (b) 2D. Scale is the same as in Figure 2.6

## **Definitions**

| $\lambda(\text{g-line})$ | $436~\mathrm{nm}$ |

|--------------------------|-------------------|

| $\lambda(	ext{i-line})$  | $365~\mathrm{nm}$ |

| $\lambda({ m KrF})$      | $248~\mathrm{nm}$ |

| $\lambda({ m ArF})$      | $193~\mathrm{nm}$ |

| $\lambda(F_2)$           | $157~\mathrm{nm}$ |

## Resolution

| Rayleigh Resolution | $R = k_1 \frac{\lambda}{NA}$ |

|---------------------|------------------------------|

| Traditional         | $k_1 = 0.8$                  |

| Advanced            | $k_1 = 0.4 - 0.6$            |

## Depth of Focus

Rayleigh Depth of Focus  $DoF = k_2 \frac{\lambda}{NA^2}$ Traditional  $k_2 = 1.0$

Table 2.1: Definitions for important wavelength nodes in lithography

| Wavelength | NA   | <b>Resolution</b> [ $\mu m$ ] | <b>DoF</b> $[\mu m]$ |

|------------|------|-------------------------------|----------------------|

| i-line     | 0.63 | 0.35                          | 0.92                 |

| KrF        | 0.60 | 0.25                          | 0.69                 |

| KrF        | 0.70 | 0.21                          | 0.51                 |

| ArF        | 0.70 | 0.17                          | 0.39                 |

| $F_2$      | 0.70 | 0.13                          | 0.32                 |

Table 2.2: Examples for typical lens configurations ( $k_1 = 0.6$ ) for deep sub micron technology nodes

the first maximum occurs at  $r' = 0.82 \frac{\lambda}{NA}$ . The qualitative agreement with the usual range of  $k_1$  is apparent.

### 2.4.3 Optical Proximity Effect

High performance optical projection imaging for lithography is strongly impacted by diffraction effects as noted in several previous sections. One result of this behavior is that individual pattern features do not image independently, but rather they interact with neighboring pattern features. A detailed analysis of the projection imaging process, for example, the analysis described in the paper by Hopkins [42], considers contributions from every portion of the reticle object and every portion of the projection optics in determining the exact image at the wafer plane. A simple heuristic argument considers the extended diffraction structure of the AIRY function comprising of the additional local maxima in the intensity distribution. Overlap of the diffraction peaks with adjacent pattern features leads to increased or decreased exposure intensity at any point in the image, compared to a purely geometrical image model.

### 2.5 **Fabrication**

### 2.5.1Description of Semiconductor Manufacturing Processes

THE PROCESSING CHAIN IN SEMICONDUCTOR MANUFACTURING

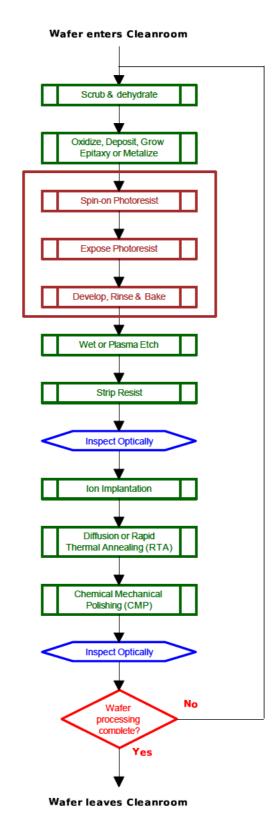

In the following subsections an overview over the different process steps, a wafer undergoes during its fabrication in the clean-room, is given. A semiconductor manufacturing process differs markedly from other processes. In many other types of processing plants, the material being processed moves through the plant in a fairly simple, straightforward, and well-integrated manner. Despite the fact that the processing flow of this material is straightforward and linear, a flow chart depicting the process will usually be quite complicated. Contrast this with a semiconductor manufacturing process, which can be described very easily with a linear processing flow chart, but whose work-in-process (WIP) moving through the plant will follow complex paths, crisscrossing back and forth in intricate patterns. During wafer processing - i.e. in the semiconductor fabrication clean-room - the integrated circuitry is formed at the surface of the single crystal silicon wafer by numerous repetitive micro-lithographic, deposition, diffusion, and etching steps, until it is finished. During this processing, depending on the complexity of the technology, a set of about fifteen up to more than thirty-five separate wafer processing cycles (which form modules like gate module, LDD module, metal module and so on), including the associated lithography step, were performed. An expanded flow chart of one of these cycles appears as shown in Figure 2.8.

Here it can be seen that the wafer will iterate through this inner circle as many times as there are masks(alignments)<sup>1</sup> for adding new circuitry.

### 2.5.2Lithography

Micro-lithography is the process of defining useful shapes on the surface of a semiconductor wafer. Typically this consists of a patterned exposure into some sort of photosensitive material already deposited on the wafer. A variety of processes that directly pattern the wafer are possible, such as directly writing on the wafer with an electron beam, or nanoimprinting structures with stamps, but at this time none is in use for high volume semiconductor manufacturing.

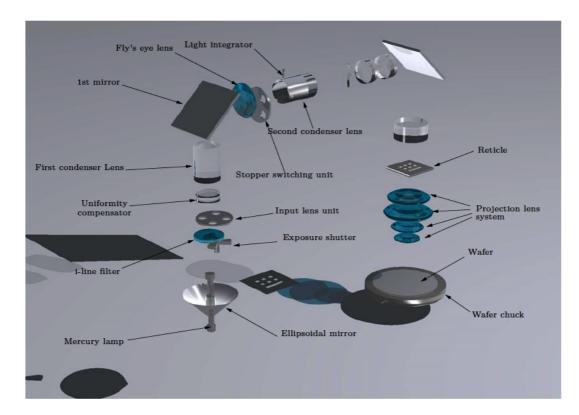

The imaging basics of optical lithography have been outlined in Section 2.4 already. Figure 2.9 shows the principal components of the illumination system of a typical i-line stepper [43] practical for structure sizes down to 350nm.

A detailed description of the lithography process and its modeling basics can be found in [44].

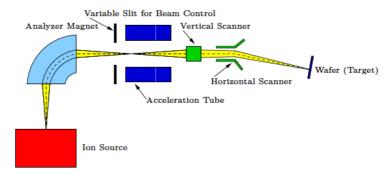

### 2.5.3Ion Implantation

Ion implantation is a process whereby energetic dopant ions are made to impinge on a silicon or other target, resulting in the penetration of these ions below the target surface and thereby giving rise to controlled, predictable dopant distributions. Low implant energy produces dopant distributions near the surface such as are required for MOS source and drain regions, or bipolar

<sup>&</sup>lt;sup>1</sup>One has to carefully distinguish between the terms "mask" and "alignment". A mask is the physical reticle for the illumination process. An alignment is the group of steps performed in a lithography track as shown in Figure 2.8 in the box. The number of masks and alignments is normally not equal, because certain reticles may be used for more than one alignment.

Figure 2.8: Expanded flow chart of the wafer fabrication cycle comprising one alignment step and the associated processing