# DISSERTATION

## Investigation of the Impact of Oxide and Interface Defects on the Performance of 4H-SiC MOSFETs

ausgeführt zum Zwecke der Erlangung des akademischen Grades

eines Doktors der technischen Wissenschaften

eingereicht an der

**Technischen Universität Wien**

Fakultät für Elektrotechnik und Informationstechnik

von

**MSc. Aleksandr Vasilev**

geboren am 17. September 1990 in Nizhnie Borki

Temnikow, Mordovian ASSR

UNTER BETREUUNG VON

**Univ.Prof. Dipl.-Ing. Dr.techn. Michael Waltl**

Wien, October 2025

# Contents

|                                                                                             |           |

|---------------------------------------------------------------------------------------------|-----------|

| <b>Acknowledgment</b>                                                                       | <b>5</b>  |

| <b>Abstract</b>                                                                             | <b>7</b>  |

| <b>Kurzfassung</b>                                                                          | <b>9</b>  |

| <b>List of Abbreviations</b>                                                                | <b>10</b> |

| <b>1. Introduction</b>                                                                      | <b>11</b> |

| 1.1. Silicon Carbide Material Properties . . . . .                                          | 11        |

| 1.2. 4H-SiC/SiO <sub>2</sub> Interface Properties. Crystal Faces . . . . .                  | 12        |

| 1.3. 4H-SiC MOSFET and MOSCAP Structures . . . . .                                          | 13        |

| <b>2. Overview of Reliability Concerns</b>                                                  | <b>15</b> |

| 2.1. Hysteresis in the $C - V$ Characteristics of MOSCAPs and MOSFETs Devices . . . . .     | 16        |

| 2.2. Hysteresis in the $I_d - V_{gs}$ Characteristics of MOSFETs Devices . . . . .          | 17        |

| 2.3. Hysteresis at Fast Bipolar Switching . . . . .                                         | 18        |

| 2.4. Correlation Between Bias Temperature Instability and Hysteresis . . . . .              | 19        |

| 2.5. State of the Art and Thesis Outline . . . . .                                          | 20        |

| <b>3. Measurement Techniques for Investigating SiC/SiO<sub>2</sub> interface Properties</b> | <b>22</b> |

| 3.1. Fast and Ultra-fast $I_d - V_{gs}$ Measurement Techniques . . . . .                    | 22        |

| 3.2. Hysteresis Measurements at $I_d - V_{gs}$ . . . . .                                    | 23        |

| 3.3. "Up-and-Down" $C - V$ Measurement and Impedance Analysis . . . . .                     | 24        |

| 3.4. Measure-Stress-Measure Technique . . . . .                                             | 26        |

| 3.5. The Fast $I_d$ Measurement Technique . . . . .                                         | 26        |

| 3.6. Bipolar AC Gate Bias Stress Test . . . . .                                             | 27        |

| 3.7. Charge-Pumping Technique . . . . .                                                     | 27        |

| 3.8. The Pump-Probe Measurement . . . . .                                                   | 28        |

| 3.9. Gate-Switching-Stress Test . . . . .                                                   | 29        |

| 3.10. Summary . . . . .                                                                     | 29        |

| <b>4. Instability of 4H-SiC MOSCAPs and MOSFETs</b>                                         | <b>30</b> |

| 4.1. Hysteresis at MOSCAPs . . . . .                                                        | 30        |

| 4.1.1. Temperature Dependence of the Hysteresis Width at Various Faces                      | 31        |

| 4.1.2. Anomalous Hysteresis Width at High Temperatures . . . . .                            | 33        |

| 4.1.3. Hysteresis Phenomena in $n$ -Type and $p$ -Type MOSCAPs . . . . .                    | 34        |

---

|                                                                                                                         |    |

|-------------------------------------------------------------------------------------------------------------------------|----|

| 4.1.4. $\Delta V_{fb}$ Shift and Hysteresis Width Under Specified Measurement Conditions . . . . .                      | 35 |

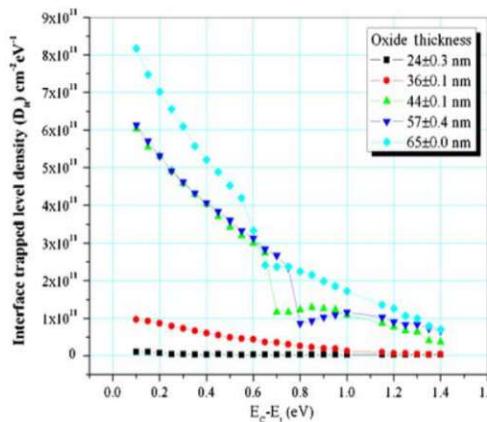

| 4.2. DOS Characterization at the 4H-SiC/SiO <sub>2</sub> Interface and Interfacial Transition Layer . . . . .           | 36 |

| 4.2.1. Effect of Oxide Thickness on Interface Trap Density in 4H-SiC/SiO <sub>2</sub> Structures . . . . .              | 39 |

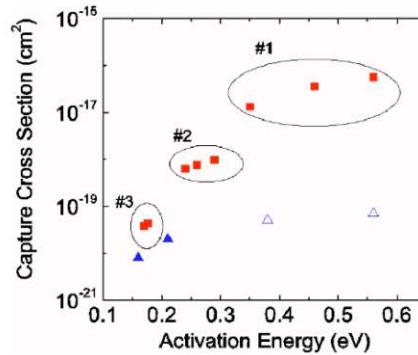

| 4.2.2. Trap Capture Cross Section Measurements and Analysis . . . . .                                                   | 39 |

| 4.2.3. Spatial Distribution of Traps ( $x_t$ ) Near the 4H-SiC/SiO <sub>2</sub> Interface . . . . .                     | 40 |

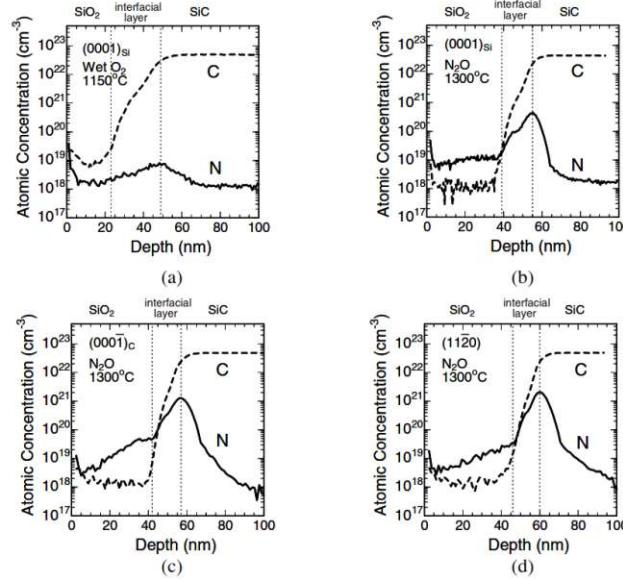

| 4.2.4. Techniques for Enhancing and Controlling the Interfacial Properties of SiC/SiO <sub>2</sub> Structures . . . . . | 42 |

| 4.3. Hysteresis in the $C - V$ curve of MOSFETs . . . . .                                                               | 45 |

| 4.3.1. Hysteresis in the $C - V$ Characteristics of Lateral and Trench MOSFETs . . . . .                                | 46 |

| 4.4. Hysteresis in the $I_d - V_{gs}$ Characteristics of MOSFETs . . . . .                                              | 48 |

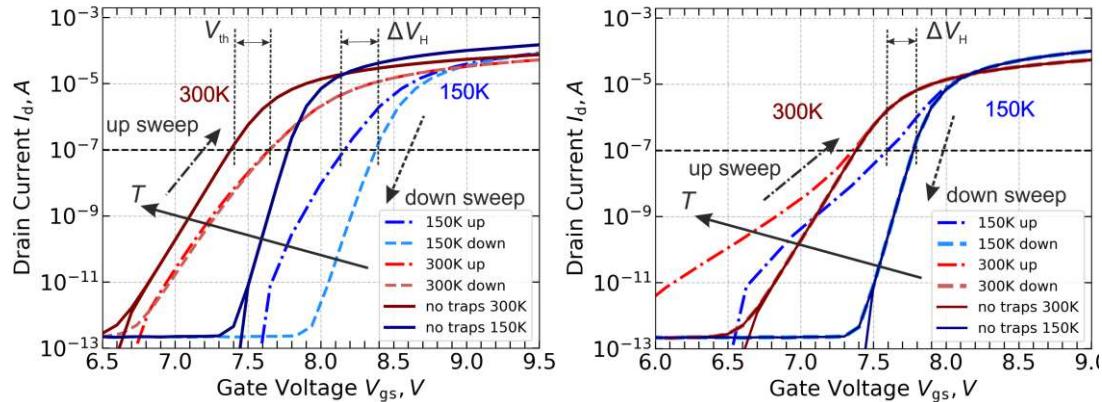

| 4.4.1. Hysteresis in the $I_d - V_{gs}$ Characteristics of Lateral MOSFETs at Various Temperature . . . . .             | 51 |

| 4.4.2. Hysteresis in the $I_d - V_{gs}$ Characteristics of Lateral and Trench MOSFETs at Various Sweeps . . . . .       | 53 |

| 4.5. Gate Switching Instability and Hysteresis . . . . .                                                                | 54 |

| 4.6. Summary . . . . .                                                                                                  | 59 |

| <b>5. Overview of Trap Kinetics Simulation Methods for the SiC/SiO<sub>2</sub> Interface</b> <b>60</b>                  |    |

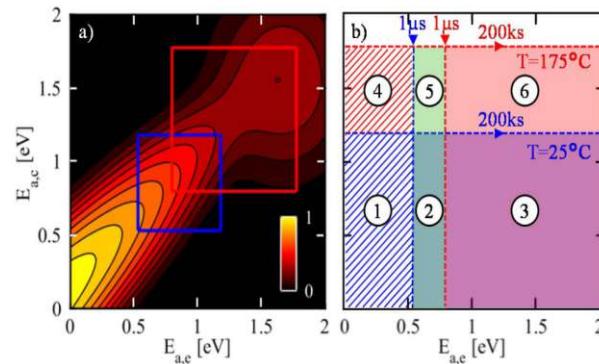

| 5.1. Capture and Emission Time (CET) Maps . . . . .                                                                     | 64 |

| 5.2. Density Functional Theory (DFT) . . . . .                                                                          | 65 |

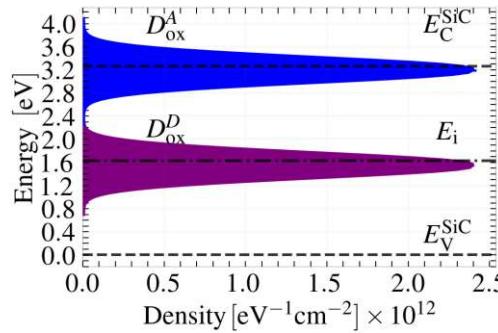

| 5.3. Trap Density of States (DOS) . . . . .                                                                             | 66 |

| 5.4. Shockley–Read–Hall model . . . . .                                                                                 | 67 |

| 5.4.1. Trap Occupation Dynamics . . . . .                                                                               | 67 |

| 5.4.2. Capture Cross-Section Model . . . . .                                                                            | 69 |

| 5.5. Channel Mobility Degradation Model . . . . .                                                                       | 70 |

| 5.6. Amphoteric or Defect-Pool Model . . . . .                                                                          | 71 |

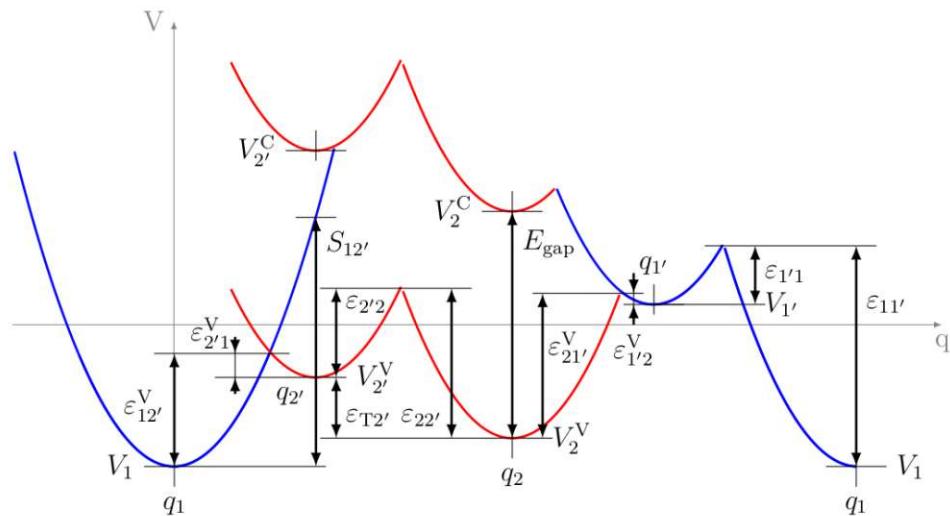

| 5.7. 4-state Non-Radiative-Multiphonon (NMP) model . . . . .                                                            | 72 |

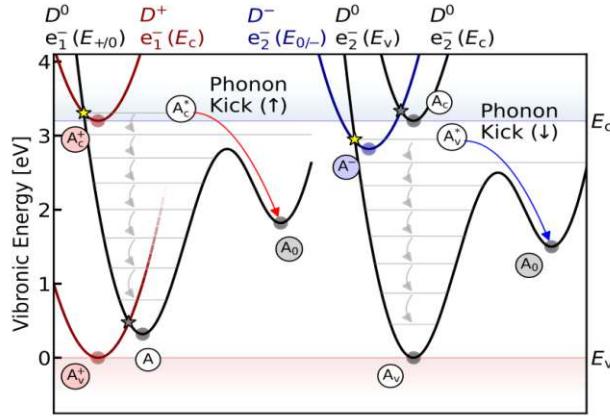

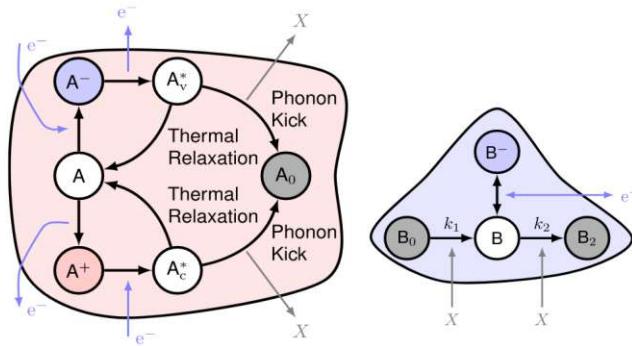

| 5.8. Combined REDR-NMP Model . . . . .                                                                                  | 76 |

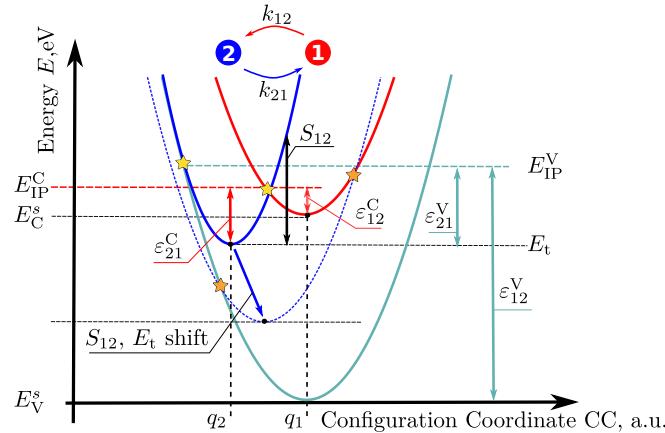

| 5.9. 2-state Non-Radiative-Multiphonon Model . . . . .                                                                  | 78 |

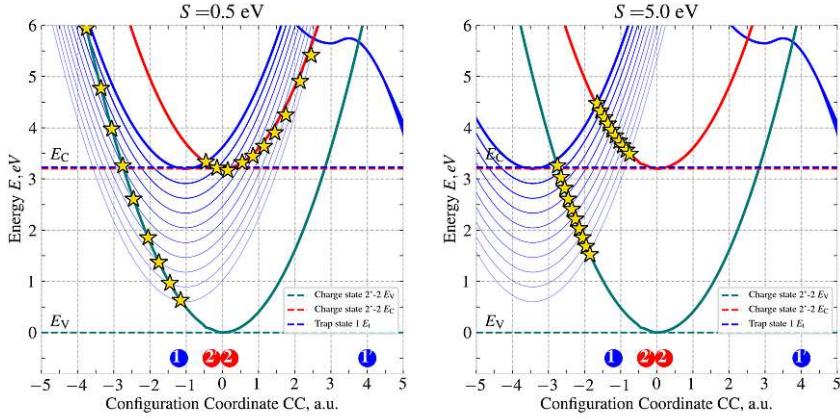

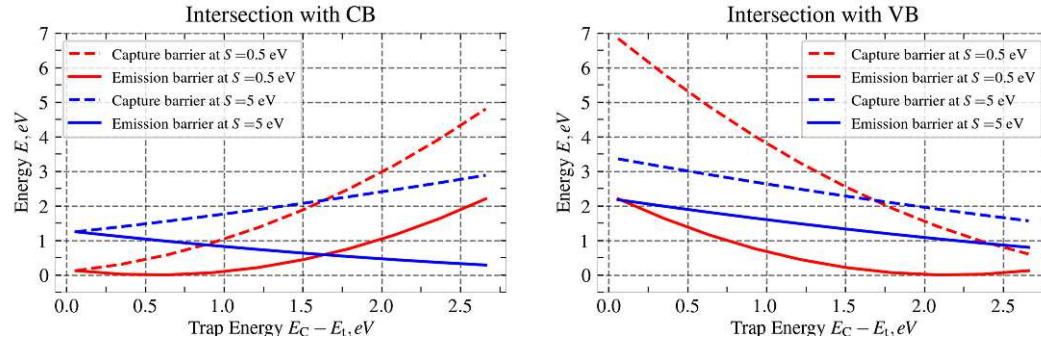

| 5.9.1. Capture and Emission Energy Barriers. Impact of the Relaxation energy $S$ . . . . .                              | 79 |

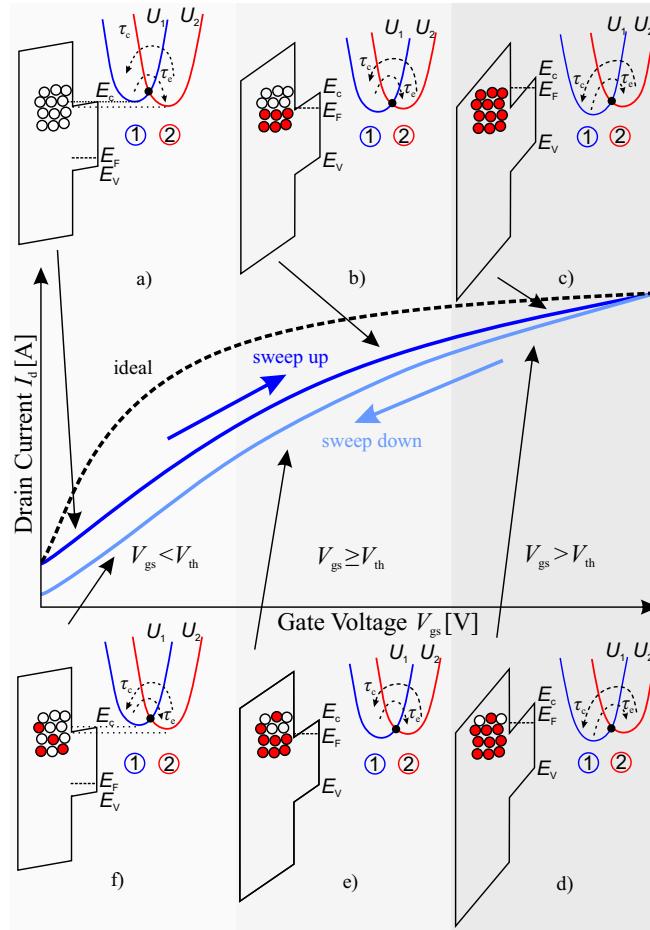

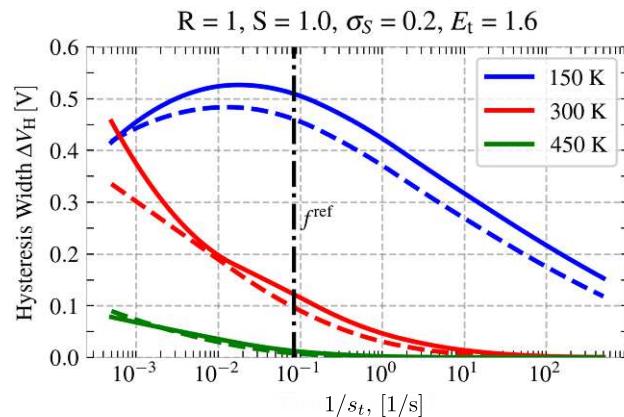

| 5.9.2. Simulation of Hysteresis Behavior in $I_d - V_{gs}$ Characteristics . . . . .                                    | 81 |

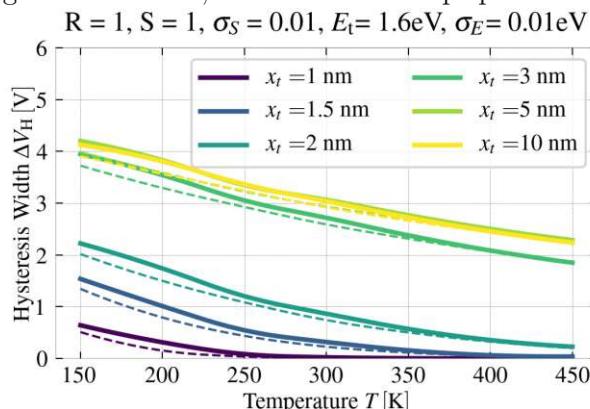

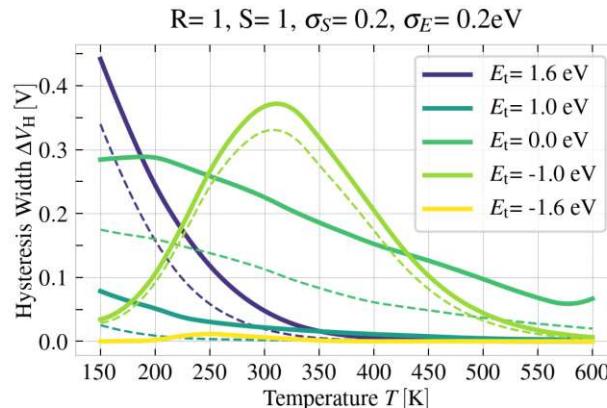

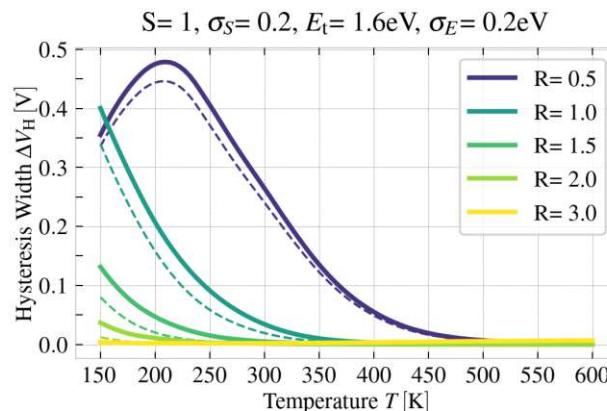

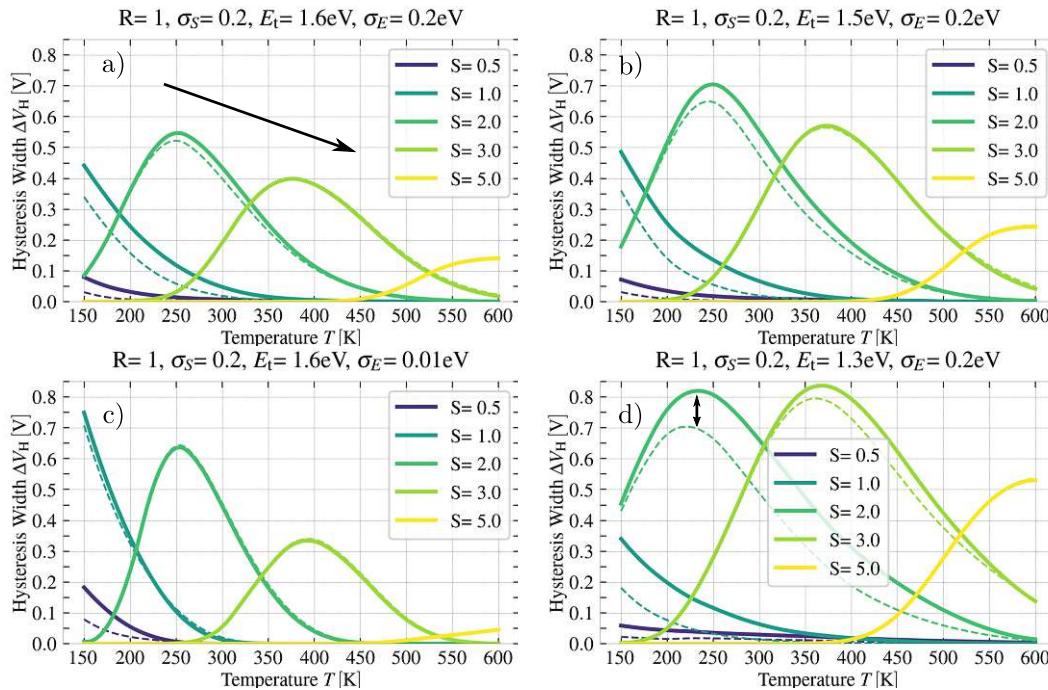

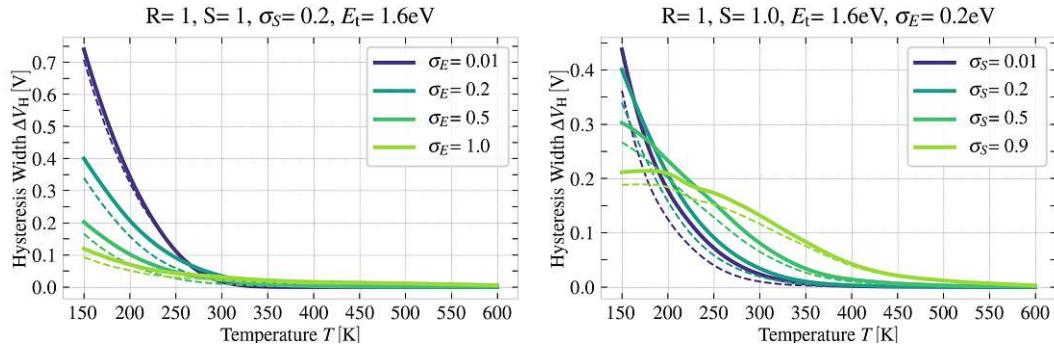

| 5.9.3. Effect of NMP Parameters on Hysteresis Width Across Temperatures . . . . .                                       | 84 |

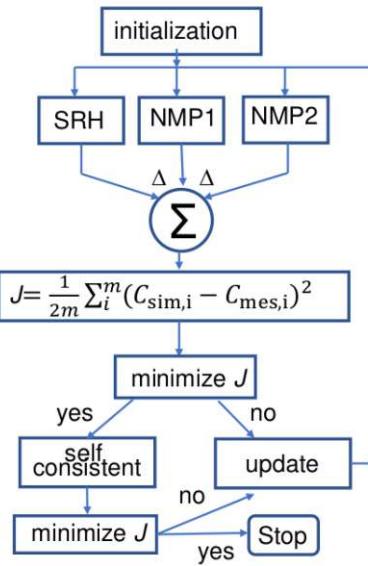

| 5.9.4. Post-Processing Steps for $I_d - V_{gs}$ and $C - V$ Fit . . . . .                                               | 87 |

| 5.10. Summary . . . . .                                                                                                 | 89 |

| <b>6. Results of Investigating Defects in 4H-SiC MOSFETs</b> <b>90</b>                                                  |    |

| 6.1. Hysteresis and BTI of Lateral MOSFETs . . . . .                                                                    | 90 |

| 6.2. Hysteresis of Lateral MOSFETs over an Extended Temperature Range . . . . .                                         | 98 |

|                                                                                                     |            |

|-----------------------------------------------------------------------------------------------------|------------|

| 6.3. Hysteresis in $I_d - V_{gs}$ of Trench MOSFETs over Multiple Cycles . . . . .                  | 99         |

| 6.4. Hysteresis in $C - V$ of Lateral MOSFETs Across Varying Frequencies and Temperatures . . . . . | 101        |

| 6.5. Hysteresis in $C - V$ of Trench MOSFETs . . . . .                                              | 107        |

| <b>7. Outlook and Conclusions</b>                                                                   | <b>109</b> |

| 7.1. Conclusions . . . . .                                                                          | 109        |

| 7.2. Outlook . . . . .                                                                              | 110        |

| <b>List of Figures</b>                                                                              | <b>122</b> |

| <b>A. Parameters of Interface Traps</b>                                                             | <b>124</b> |

| <b>Bibliography</b>                                                                                 | <b>161</b> |

| <b>List of Publications</b>                                                                         | <b>164</b> |

| <b>Curriculum Vitae</b>                                                                             | <b>167</b> |

# Acknowledgement

First, I would like to express my deep gratitude to PROFESSOR MICHAEL WALTL, who provided all the resources and funding<sup>1</sup> during this uncertain time. In addition, his time and attention to my project were exclusively valued.

I would also like to thank PROFESSOR TIBOR GRASSER for allowing me to dive into a new scientific field that provided an invaluable experience in conjunction with useful guidance and feedback.

I have been fortunate to collaborate with numerous of excellent colleagues at the Institute for Microelectronics, despite the challenges posed by the pandemic in terms of communication and connections. I am profoundly grateful to each of you, many of whom have become close companions during this fascinating even somewhat difficult period. The following is an arbitrary list of names: CHRISTIAN SCHLEICH, BERNARD STAMPFER, DOMINIC WALDHÖR, JAKOB MICHL, THERESIA KNOBLOCH, MARKUS JECH, AL-MOATASEM BELLAH EL-SAYED

Also, I would like to thank the colleagues from our industrial partners at Infineon Villach and Munich, KAI, imec and GTS. Without your unlimited experimental support and advise, this thesis would not have been possible: GERHARD RZEPKA, ALEXANDER GRILL, MAXIMILIAN W. FEIL, GREGOR POBEGEN, PAUL ELLINGHAUS, PETER ANISCH-NEGRELLI, ANDREW WOOD and especially STANISLAV TYAGINOV for the opportunity to work on this interesting project.

I am particularly grateful for the highly professional skills that I have enhanced as a result of the exchange of invaluable experience, and the useful advice and support provided by: ASSOCIATE PROFESSOR YURY ILLARIONOV, PROFESSOR MIKHAIL I. VEXLER, PROFESSOR ALEXEI F. KARDO-SYSOEV

A special thank you is due to the people who have created a perfect working atmosphere at the Institute: DIANA POP, PETRA KAMPTNER-JONAS, MANFRED KATTERBAUER, JOHANN CERVENKA

Thank you all, and also for providing your critical feedback to this thesis.

I want to be particularly grateful to my family, my wife YULIA, and my daughter EVA for their support, love and provided time.

---

<sup>1</sup>The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development, and the Christian Doppler Research Association are gratefully acknowledged.

# Abstract

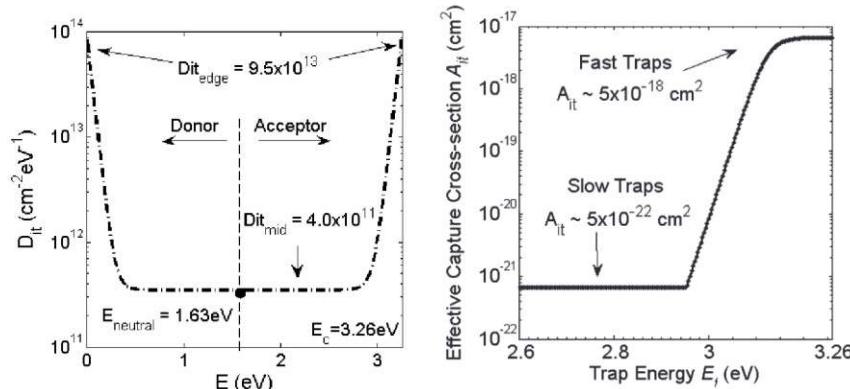

The reliability issues caused by oxide and interface defects of a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) play a major role in the robustness of device functionality. 4H silicon carbide (4H-SiC) MOSFETs are a serious competitor to silicon (Si) power devices because of their ability to operate at higher temperatures, higher power densities, higher frequencies, reduced dimensions, and higher voltages than Si-based MOSFETs. Even with well-known manufacturing processes, much research has focused on the reliability concerns associated with the SiC/SiO<sub>2</sub> interface and oxide quality, attributed to the higher defect density that can be observed when data is compared to that of the SiO<sub>2</sub>/Si interface. A new direction for future generations of 4H-SiC power MOSFETs is related to trench technologies, which offer increased channel mobility, resulting in reduced ON resistance owing to their unique interface properties. The differences between planar and trench 4H-SiC MOSFETs are evident in the hysteresis width observed in the  $I_d - V_{gs}$  and  $C - V$  curves, as well as in the Bias Temperature Instability (BTI) and Gate Switching Instability (GSI), which arise from the different kinds of defects and their associated charge trapping kinetics affected by the applied voltage bias, ambient temperature, sweep duration, and frequency.

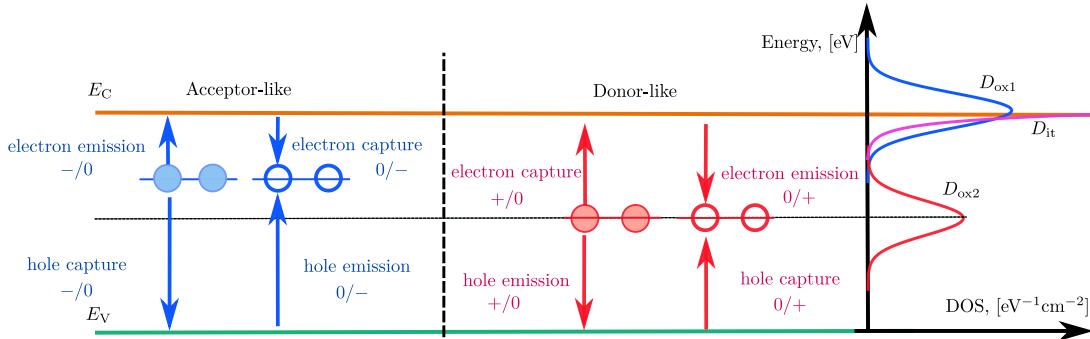

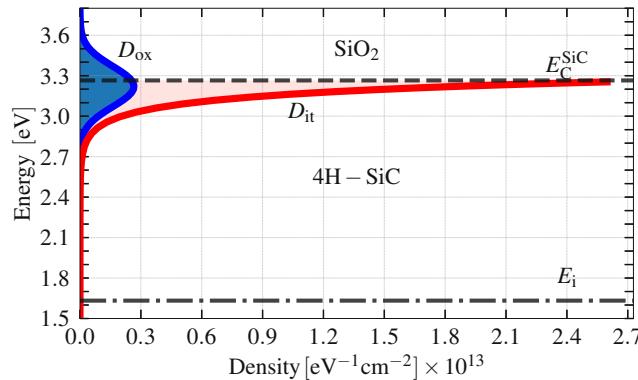

Despite the evident advancements in recent years regarding interface enhancement via post-oxidation annealing in various gases, as well as the improvement of channel carrier mobility, threshold voltage stability, and reduction of hysteresis width, the precise origin and electrical properties of these traps continue to be a contentious issue, particularly concerning the different properties of planar and trench MOSFETs interfaces and the corresponding distinct gas recipes for interface enhancement. The various trap types at the SiC/SiO<sub>2</sub> interface have been shown to consist of acceptor-like or donor-like types, which can be categorized as "slow" border traps which located deep in the insulator or "fast" interface traps in relation to their charge-trapping kinetics, exhibiting complex cumulative instability effects. Thus, the fundamental charge transfer reactions for the "slow" traps can be characterized by the Non-Radiative Multi-Phonon (NMP) model. To understand the "fast" traps behavior, a physical-based modeling approach based on Shockley-Read-Hall (SRH) theory was used in this research. By using TCAD simulations and comparing them with the measurement results, a possible trap candidate for anomalously elevated hysteresis width at higher temperatures was investigated. It was postulated that the increase in the hysteresis width at elevated temperatures may be attributed to amphoteric  $P_b$  or  $P_{bc}$  trap centers with varying NMP parameters.

Finally, the hysteresis width characteristics across a broad temperature range were examined in both the  $I_d - V_{gs}$  and  $C - V$  curves, along with the BTI and subthreshold

voltage slopes for the lateral MOSFETs. The hysteresis width of the  $I_d - V_{gs}$  curves across multiple cycles and  $C - V$  curves for the trench devices were simulated. The results presented in this study will contribute to improving simulation frameworks to explain the intricate behavior of charge trapping phenomena under various operating conditions.

## Kurzfassung

Die Zuverlässigkeit von Metalloxid-Halbleiter-Feldeffekttransistoren (MOSFETs) stellt einen zentralen Aspekt für die Robustheit und Langzeitsatibilität in Applikationen dar. Insbesondere 4H-Siliziumkarbid (4H-SiC)-MOSFETs ersetzen zunehmend konventionelle Silizium-(Si)-Leistungshalbleiter, da sie in der Lage sind, unter höheren Temperaturen, mit höheren Leistungsdichten, höheren Schaltfrequenzen, kleineren Abmessungen sowie bei erhöhten Betriebsspannungen gegenüber Si-basierten MOSFETs zu arbeiten.

Trotz etablierter Fertigungsprozesse konzentriert sich ein erheblicher Teil der aktuellen Forschung weiterhin auf die Zuverlässigkeit dieser Bauelemente, insbesondere im Hinblick auf die SiC/SiO<sub>2</sub>-Grenzfläche und die Qualität der Gate-Oxide. Die Ursache hierfür liegt in der signifikant höheren Defektdichte im Vergleich zur etablierten Si/SiO<sub>2</sub>-Grenzfläche, welche aus elektrischen Messungen an SiC Transistoren hervorgeht. Konventionelle planare MOSFET-Strukturen weisen diesbezüglich Nachteile auf und bleiben hinsichtlich ihrer Leistungsfähigkeit hinter den neuesten kommerziell verfügbaren 4H-SiC-Leistungs-MOSFETs zurück.

Ein innovativer Ansatz für zukünftige Generationen von 4H-SiC-MOSFETs stellt die Implementierung von Grabenstrukturen (Trench-Technologien) dar, welche durch eine erhöhte Kanalflächendichte eine Reduktion des Einschaltwiderstands ermöglichen. Diese Vorteile ergeben sich maßgeblich aus den besonderen Eigenschaften der Grenzfläche.

Die Unterschiede zwischen planaren und trench-basierten 4H-SiC-MOSFETs manifestieren sich deutlich in der beobachteten Hysteresebreite sowohl in den  $I_d$ - $V_{gs}$ - als auch den  $C$ - $V$ -Kennlinien sowie in der Ausprägung der Bias Temperature Instability (BTI) und der Gate Switching Instability (GSI). Diese Phänomene sind das Resultat unterschiedlicher Systeme und Dynamiken des Ladungsfangs an Defekten im Transistor, die durch die angelegte Vorspannung, die Umgebungstemperatur, die Schwingungsdauer und die Anregungsfrequenz beeinflusst werden.

Auch wenn in den letzten Jahren erhebliche Fortschritte erzielt wurden – insbesondere durch Nachoxidationsprozesse unter unterschiedlichen Gasatmosphären, die Grenzflächeneigenschaften verbessern, die Kanalträgermobilität erhöhen, die Schwellenspannung stabilisieren und die Hysteresebreite reduzieren – sind die genauen physikalischen Eigenschaften der beteiligten Defekte weiterhin Gegenstand intensiver Forschungsarbeiten. Dies gilt insbesondere im Kontext der strukturellen und prozesstechnologischen Unterschiede zwischen planaren und trench-basierten Bauelementarchitekturen sowie der Verwendung unterschiedlicher Gasrezepte zur Grenzfläch-enpassivierung.

Die Defekte, welche sich an der SiC/SiO<sub>2</sub>-Grenzfläche befinden, lassen sich in akzeptor- und donatorartige Zustände unterteilen, die entsprechend ihrer Ladungsdy-

namik als "schnell" bzw. "langsam" klassifiziert werden. Diese Zustände können komplexe, kumulative Instabilitätseffekte hervorrufen. Die fundamentalen Ladungstransferprozesse bei "langsamem" Trap-Centers können dabei durch das nicht-strahlende Multiphononenmodell (Non-Radiative Multi-Phonon, NMP) beschrieben werden. Zur Modellierung des Verhaltens der "schnellen" Trap wurde im Rahmen dieser Arbeit ein physikalisch fundierter Modellierungsansatz auf Basis der Shockley-Read-Hall-(SRH) Theorie herangezogen.

Mittels Computers Simulationen in Kombination mit experimentellen Messergebnissen wurde ein möglicher Kandidat für eine Defektklasse identifiziert, die für die, bei erhöhten Temperaturen beobachtete, anomale Verbreiterung der Hysteresekennlinien verantwortlich sein könnten. Es ist davon auszugehen, dass nicht ausschließlich mobile Ionen, sondern insbesondere amphotere  $P_b$ - bzw.  $P_{bC}$ -Zentren mit variierenden NMP-Parametern diese Effekte verursachen könnten.

Abschließend wurden die Hysteresebreiten in einem weiten Temperaturbereich sowohl für die  $I_d - V_{gs}$  als auch die  $C - V$  Kennlinien systematisch untersucht. Dazu wurden BTI Phänomene und die Subthreshold-Spannungsneigung für laterale MOSFET-Strukturen analysiert. Ergänzend zu der Untersuchung wurden die Hysteresebreiten der  $I_d - V_{gs}$  Kurven und die Kennlinienverläufe der  $C - V$ -Messungen bei Trechn-Bauelementen simulativ erfasst. Die Auswertung offenbarte ein charakteristisches Trap-System, das sich durch spezifische Parameter beschreiben lässt, und welches die experimentell ermittelten Messergebnisse gut widerspiegelt. Die gewonnenen Ergebnisse unterstützen zukünftige Arbeiten dabei Simulationsmodelle noch besser zu kalibrieren und so das Verhalten der SiC Transistoren noch besser beschreiben zu können.

# List of Abbreviations

|               |                                                        |             |                                           |

|---------------|--------------------------------------------------------|-------------|-------------------------------------------|

| <b>4H-SiC</b> | 4H-Silicon Carbide                                     | <b>MSM</b>  | Measure Stress Measure                    |

| <b>BTI</b>    | Bias Temperature Instability                           | <b>NBTI</b> | Negative Bias Temperature Instability     |

| <b>CDDLTS</b> | Constant-Capacitance Deep-Level Transient Spectroscopy | <b>NMP</b>  | Non-Radiative Multi-Phonon                |

| <b>CET</b>    | Capture Emission Time                                  | <b>PBTI</b> | Positive Bias Temperature Instability     |

| <b>DFT</b>    | Density Functional Theory                              | <b>POA</b>  | Post Oxidation Annealing                  |

| <b>EELS</b>   | Electron Energy Loss Spectroscopy                      | <b>RTN</b>  | Random Telegraph Noise                    |

| <b>eMSM</b>   | extended Measure Stress Measure                        | <b>SiC</b>  | Silicon Carbide                           |

| <b>GSI</b>    | Gate Switching Instability                             | <b>SIMS</b> | Secondary Ion Mass Spectroscopy           |

| <b>GSI</b>    | Gate Switching Instability                             | <b>SiPM</b> | Silicon Photomultiplier                   |

| <b>HCD</b>    | Hot Carrier Degradation                                | <b>SRH</b>  | Shockley-Read-Hall                        |

| <b>HTGS</b>   | High-Temperature Gate-bias Stress                      | <b>STEM</b> | Scanning Transmission Electron Microscopy |

| <b>IGBT</b>   | Insulated Gate Bipolar Transistor                      | <b>TCAD</b> | Technology Computer-Aided Design          |

| <b>MOS</b>    | Metal Oxide Semiconductor                              | <b>TDDB</b> | Time-Dependent Dielectric Breakdown       |

| <b>MOSCAP</b> | Metal Oxide Semiconductor Capacitor                    | <b>TDDS</b> | Time-Dependent Defect Spectroscopy        |

| <b>MOSFET</b> | Metal Oxide Semiconductor Field-Effect Transistor      |             |                                           |

# 1. Introduction

In power electronics, an electrical switch is typically implemented using a metal-oxide semiconductor field-effect transistor (MOSFET) or an Insulated Gate Bipolar Transistor (IGBT). With considerable enhancements in the conversion efficiency realized in devices utilizing silicon substrates, inherent limitations in minimizing static and dynamic switching losses owing to the material characteristics of silicon must be resolved. Wide-bandgap semiconductors, such as silicon carbide (4H-SiC) and gallium nitride (GaN), provide enhanced features for power electronics to enhance the conversion efficiency, have been included as substrate materials in commercially accessible devices, and are serious contenders for replacing Si-based power switches in the near future [1], [2]. Commercial planar and trench 4H-SiC MOSFETs are promising candidates for use in power electronics. However, thermally grown silicon dioxide ( $\text{SiO}_2$ ) on SiC surfaces remains a major research topic owing to the high defect density at the  $\text{SiO}_2/\text{SiC}$  interface compared with that at the  $\text{SiO}_2/\text{Si}$  interface. This became more pronounced because the devices used different 4H-SiC faces, which influenced the reliability of the electrically active border and interface traps on the reliability of circuit operation. Investigating these defects using  $I_d - V_{gs}$  with  $C - V$  curve toughener and accurate modeling of the trap kinetics allows us to better understand the origin of the hysteresis and other instability phenomena and reduce the density of interface states using special technology steps such as post-oxidation annealing.

## 1.1. Silicon Carbide Material Properties

In the late 1980s, it became evident that silicon power-switching devices exceeded their theoretical limits, which could be substantially extended by manufacturing power devices using materials with higher breakdown electric fields such as silicon carbide (4H-SiC) or semiconducting diamond [3]. For vertically oriented devices, the theoretical minimum value of the specific resistance (in  $\Omega \text{ cm}^2$ ) is

$$R_{SP} = \left(\frac{3}{2}\right)^3 \frac{V_B^2}{\mu_N \varepsilon_S E_C^3} = \frac{3.375 V_B^2}{\mu_N \varepsilon_S E_C^3} \quad (1.1)$$

where  $\mu_N$  is the electron mobility perpendicular to the surface,  $\varepsilon_S$  is the permittivity of the semiconductor,  $E_C$  is the critical field for the avalanche breakdown perpendicular to the surface, and  $V_B$  is the designed blocking voltage in the drift region. where  $(\mu_N \varepsilon_S E_C)$  is the Baliga figure of merit (BFOM) [4].

The critical field in SiC is almost an order of magnitude higher than that in Si, as shown in Table 1.1.

Table 1.1: Semiconductor material parameters. [5], [6]

| Material                                                   | 4H-SiC | GaN | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> | Diamond   | Si   |

|------------------------------------------------------------|--------|-----|-----------------------------------------|-----------|------|

| $E_g$ (eV)                                                 | 3.26   | 3.4 | 4.7-4.9                                 | 5.5       | 1.1  |

| $\varepsilon_s$                                            | 9.7    | 9.0 | 10                                      | 5.5       | 13.1 |

| $E_C$ (MV cm <sup>-1</sup> )                               | 3.0    | 3.3 | 8                                       | 10        | 0.3  |

| $\mu_N$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 900    | 900 | 300                                     | 1900      | 1438 |

| Relative BFOM                                              | 517    | 854 | 3371                                    | 22937     | 1    |

| $\lambda$ (W cm <sup>-1</sup> K <sup>-1</sup> )            | 4.9    | 1.3 | 0.24                                    | 22        | 1.5  |

| $v_g$ (10 <sup>7</sup> cm s <sup>-1</sup> )                | 2.0    | 2.5 | 2                                       | 1 (holes) | 1.0  |

In addition, the thermal conductivity  $\lambda$  of 4H-SiC and saturation carrier velocity  $v_g$  are higher than those of Si.

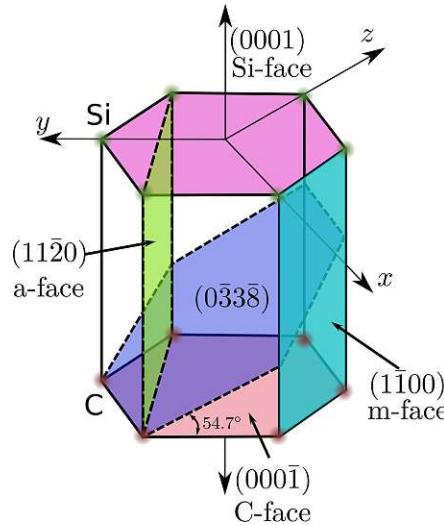

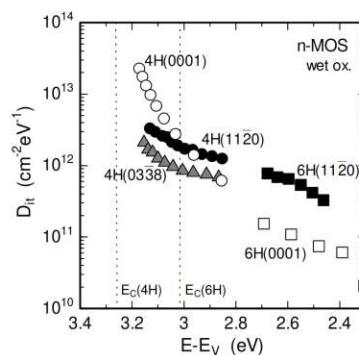

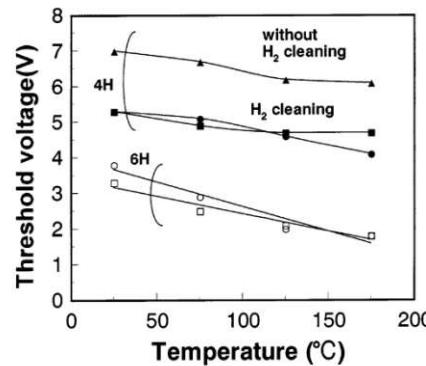

## 1.2. 4H-SiC/SiO<sub>2</sub> Interface Properties. Crystal Faces

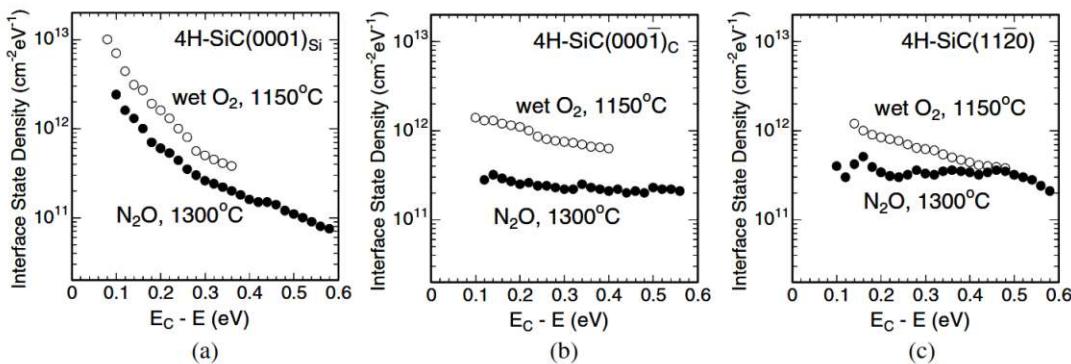

The first planar and lateral 4H-SiC MOSCAPs and MOSFETs had (0001)-Si faces. Nevertheless, alternative face options are available, such as the nonpolar (11 $\bar{2}$ 0) a-face (which is mostly used in trench devices), (1 $\bar{1}$ 00) m-face, and polar (000 $\bar{1}$ ) C-face (see Fig. 1.1). The (03 $\bar{3}$ 8) in 4H-SiC is the face was tilted by 54.7° toward <01330> from the (0001) face [7]. The atomic structure of a surface differs from face to face. Si atoms determine the Si-face of SiC, whereas C atoms terminate the C-face; the non-polar faces have equal amounts of Si and C atoms. The various surface structures exhibit unique characteristics. For example, the a-face has a higher channel mobility than the Si-face and alternative faces even after post-oxidation annealing. This corresponds to the different defect densities at the 4H-SiC/SiO<sub>2</sub> interface. Alternatively, there are different oxidation rates at 1150 °C. In addition, the a-face and C-face have the highest oxidation rates compared to the Si-face, which has the lowest rate.

A specialized POA is required to enhance the interface quality owing to the different defect densities across different faces. For Si-face devices, wet oxidation and/or H<sub>2</sub> annealing may enhance channel mobility.

The a-face channel mobility was improved using the hydrogen POA process or wet annealing. NO annealing of the (03 $\bar{3}$ 8) face also enhanced the channel mobility. The preferred POA is the nitrogen NO base method for creating a-face and m-face devices. Dry oxidation and/or NO annealing are employed for the Si-face and non-polar faces; however, they are less effective on the C-face in terms of reducing the interface trap density and enhancing mobility. In conclusion, devices with nonpolar faces exhibit a higher threshold voltage than those with Si faces, which is particularly advantageous for power-device applications [5], [8].

Figure 1.1.: Crystal faces in 4H-SiC. The Si-face ends with Si atoms (large green balls), whereas the C-face ends with C atoms (small black balls). Non-polar faces, such as the a-face and m-face, possess an equal number of silicon and carbon atoms. Adapted from [5].

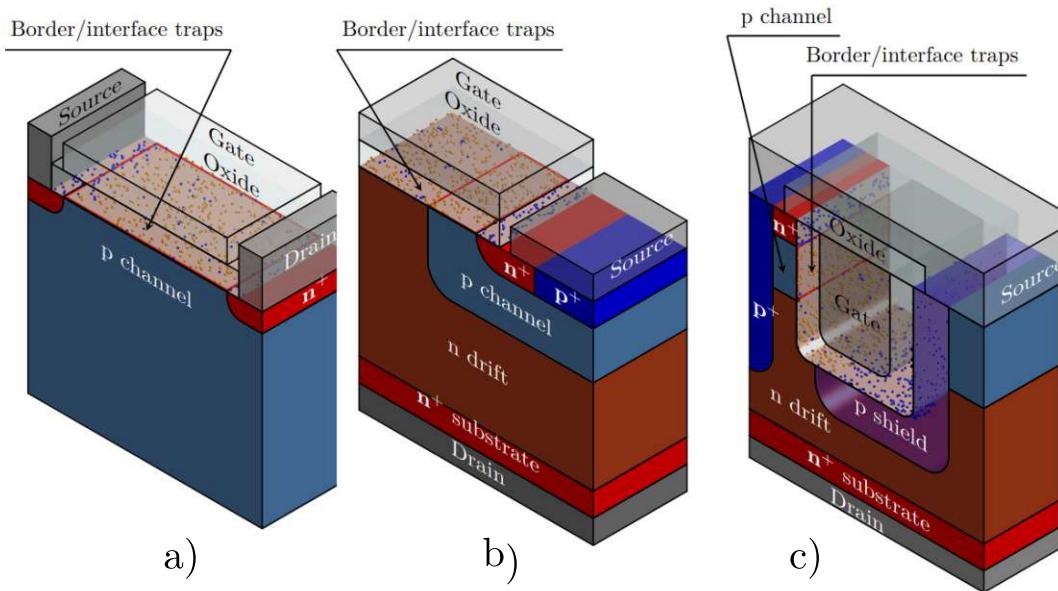

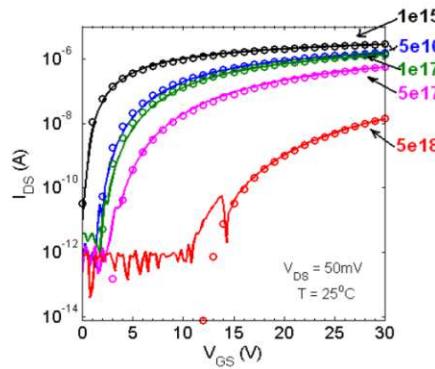

### 1.3. 4H-SiC MOSFET and MOSCAP Structures

Depending on the design, two primary crystal orientations where the oxide is grounded are used: the Si-face for the lateral and DMOSFETs and the a-face for the asymmetric trench 4H-SiC nMOSFET, as illustrated in Fig. 1.2. In our investigation, a lateral 4H-SiC nMOSFETs with an  $n^+$  poly gate is used. An oxide thickness of 50 nm and a gate length of 7.5  $\mu\text{m}$  were assumed, see Fig. 1.2, a. This oxide layer was formed on a Si-face substrate via chemical vapor deposition. Next, a commercial discrete asymmetric trench 4H-SiC nMOSFET, and assumed that the intended oxide thickness was 60 nm were used. A trench was fabricated using plasma-etched surfaces. The n-channel a-face MOSFETs received  $\text{SiO}_2$  deposited via chemical vapor deposition with subsequent post-oxidation annealing in NO ambient, see Fig. 1.2, c [1], [2], [9], [10]. In this study, only test lateral MOSFETs were examined because the trap system is identical to that of DMOSFETs (Fig. 1.2, b), which have the same crystal face as the lateral devices (Fig. 1.2, a).

It is assumed that the fast interface traps are located directly at the  $\text{SiC}/\text{SiO}_2$  interface, whereas the slow border traps are positioned at a depth of 1 nm from the interface. Only traps placed directly above the channel were involved in the trapping kinetics. This behavior depends on its parameters, which can either capture or emit electrons or holes, leading to distortions in the measured curves (see Fig. 1.2).

Figure 1.2.: a) Lateral 4H-SiC transistor. The possible defects leading to the distortion of the  $C - V$  and  $I_d - V_{gs}$  curves are shown. b) Planar DMOSFET c) Asymmetric trench 4H-SiC MOSFET (the very light grey marks the oxide).

## 2. Overview of Reliability Concerns

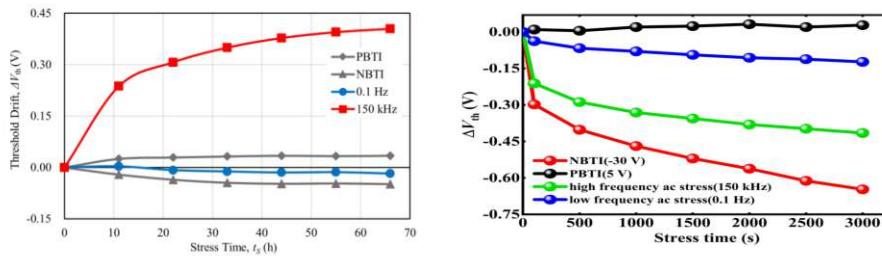

Time-dependent threshold voltage instability, also known as Bias Temperature Instability (BTI), occurs under a static gate bias. A positive gate bias induces a positive threshold voltage shift, commonly referred to as Positive Bias Temperature Instability (PBTI), whereas a negative gate bias results in a negative threshold voltage shift, known as Negative Bias Temperature Instability (NBTI) [11], [12], [13]. The permanent BTI is almost unrecoverable on a timescale of hours. Regardless of how the threshold voltage drifts, static BTI can be treated as low risk in circuit operation and can be managed by interface passivation and correctly selecting the gate voltage. However, because the gate stress applied to the SiC MOSFET is usually dynamic rather than static, the threshold voltage instability under dynamic gate stress, which is referred to as the dynamic BTI, is more important [14]. Similar to the case of a static BTI, the threshold voltage in a dynamic BTI drifts positively under positive gate bias and negatively under negative gate bias. However, unlike the static BTI, the dynamic threshold voltage drift, which is mostly induced by the interface traps, is believed to recover within one device switching period. Dynamic BTI, also known as threshold hysteresis, is often regarded harmless [15], [16]. As silicon carbide SiC epitaxy technology advances [17], they experience fewer crystalline defects, resulting in longer carrier lifetimes and, for example, a low  $R_{on}$ . However, the main degradation effects arise from the interfaces between SiC and the oxides because of their amorphous nature. This leads to dangling bonds and defects in the oxides. Hence, we can observe that in MOSFETs, effects such as channel mobility degradation,  $1/f$  noise, random telegraph noise (RTN) [18], hot carrier degradation (HCD) [19], positive- and negative-bias temperature instability (PBTI and NBTI), and hysteresis [20].

It is shown that the different behaviors of MOSFETs during positive and negative gate voltage stress and temperature variations originate from the different trap parameters. Understanding and predicting the charging and discharging kinetics of oxide and interface defects is important for improving the reliability of 4H-SiC MOSFET reliability or controlling BTI to investigate state-of-the-art devices based on trap kinetics. Eventually, significant progress was made using the nonradiative multiphon NMP model with modifications and how the trap parameters influence the capture emission regime, resulting in the occupation of these traps and reliability issues such as BTI and hysteresis [18], [21].

The first review paper, which presented a synthesis of theoretical and experimental results, was presented by Wang *et al.* in 2006 [22]. The asymmetry in the measurement results, which has been observed by various scientists, was described by the different types of traps, owing to the amphoteric nature of  $P_b$  centers and hydrogen bridges (Si–H–Si), which have been considered the main culprit for BTI [23], [24], [25], [26].

When the 4H-SiC MOSFET is stressed by applying high gate voltages at elevated temperatures, we can observe the threshold voltage shift  $\Delta V_{th}$  which is called bias temperature instability. During the stress time at room temperature, the dynamic nature of  $V_{th}$  did not degrade the device because the effects were recoverable and repeatable.  $V_{th}$  drift is non-destructive, non-permanent, and reversible owing to a transient charge-trapping phenomenon [16]. However, in a pseudo-D CMOS inverter circuit with 4H-SiC MOSFETs, the impact of charge trapping leads to performance degradation and increases circuit delay [27]. For example, if  $V_{th}$  shifts in the negative direction, it might result in a substantial increase in the device leakage current, even when the device is supposed to be in an off or blocking state, and the positive  $V_{th}$  shift tends to increase the on-state resistance and degrade performance [16], [28], [29].

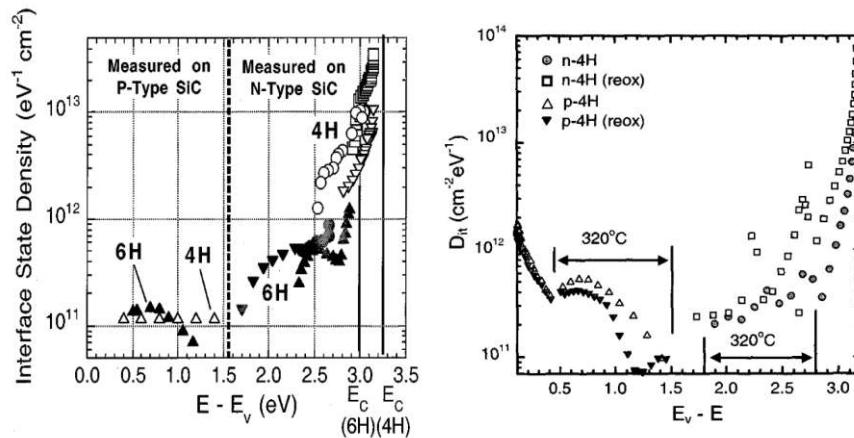

The progress made in enhancing the properties of the 4H silicon carbide (4H-SiC) epitaxial layer has provided a significant boost for its application in high-power electronics, owing to its unique attributes compared to silicon (Si). The ability to grow native oxides on the surface of a 4H-SiC substrate enables the creation of MOSFETs without requiring substantial modifications to the manufacturing process employed for silicon Si MOSFETs [30]. The wider bandgap of 4H-SiC results in an increased number of active traps and defects caused by imperfect manufacturing processes and contamination, as well as the different band alignment compared to Si. Consequently, the initial investigations focused mostly on studying the mechanisms occurring at the interface between SiC and  $\text{SiO}_2$ , specifically in different crystal structures and surface orientations, and their subsequent enhancements. Early studies, such as the one conducted by Afanas'ev *et al.* [8], [31], [32], [33], [34], [35], [36], [37], [38], [39] Lelis *et al.* [16], [28], [29], [40], [41], [42], [43], [44], [45], [46], [47], [48], Aichinger *et al.* [49], [50], [51], [52], [53], [54], [55], [56], [57], [58], [59], [60], [61], [62], [63], [64], [65], [66], [67], [68], [69], [70], [71], [72], [73], [74], [75], [76], Kimoto *et al.* [7], [17], [36], [38], [39], [77], [78], [79], [80], [81], [82], [83], [84], [85], [86], [87], [88] and another authors have examined the impact of border, oxide, and interface traps in MOSCap and MOSFETs structures. These studies focused on the effects of these traps on voltage shifting and hysteresis using techniques such as  $I_d - V_{gs}$  and  $C - V$  measurements. Subsequently, initial techniques for passivation in various environments were suggested, including annealing and stress testing.

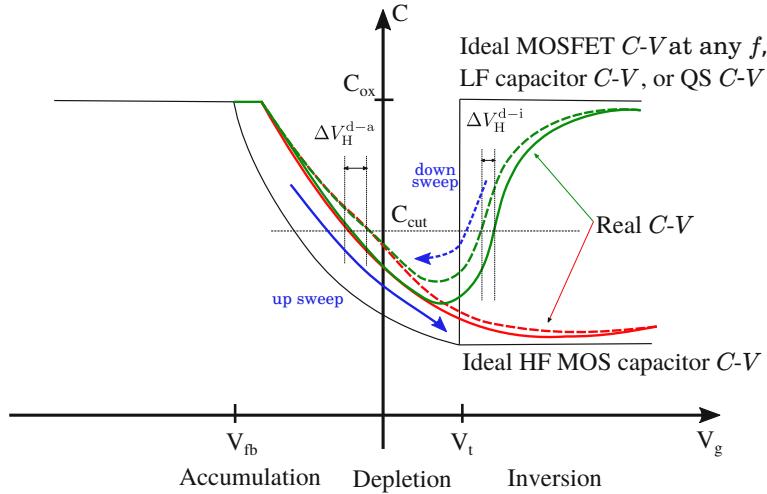

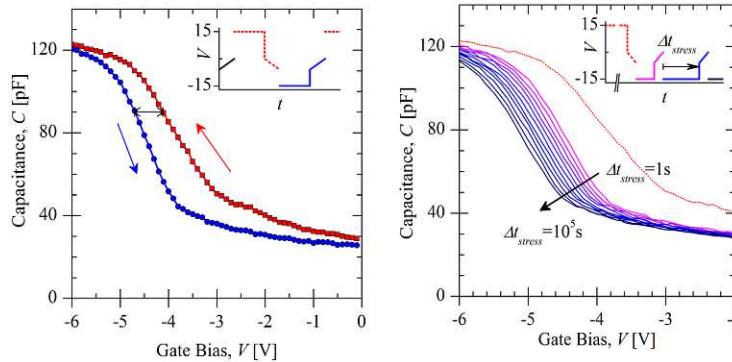

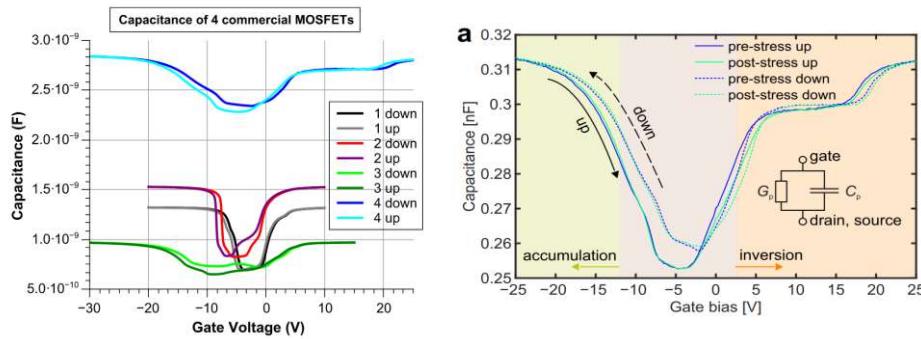

## 2.1. Hysteresis in the $C - V$ Characteristics of MOSCAPs and MOSFETs Devices

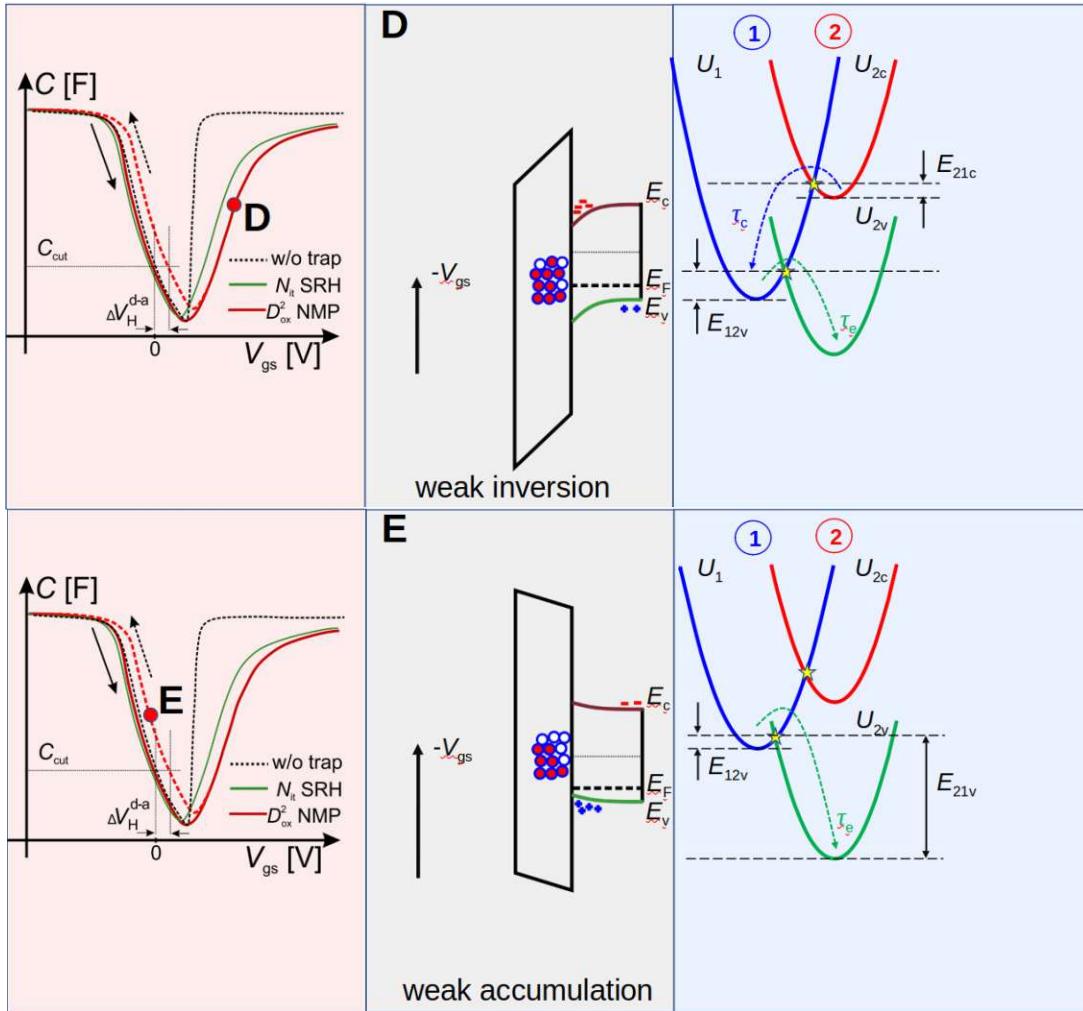

Capacitance - voltage ( $C - V$ ) curves are one of the most common methods used to investigate the 4H-SiC/ $\text{SiO}_2$  interface properties, owing to the visibility of trap states during the depletion and accumulation regimes in the shifted or stretched-out  $C - V$  curves.  $C - V$  measurements can be performed on both MOSCAP and MOSFET structures. Fig. 2.1 illustrates the ideal and real  $C - V$  curves during both up and down gate voltage sweeps. In the ideal case, the high-frequency MOSCAP  $C - V$  (HF  $C - V$ ) follows the lower curve in Fig. 2.1. In contrast, at a low frequency or

quasi-static (QS), even MOSCAPs  $C - V$  would follow the upper curve. When an up-gate voltage is applied, the Fermi level moves, leading to a change in the occupation of the interface or border traps. The "stretch out" effect (or  $\Delta V_{th}$  and  $\Delta V_{fb}$  shifts) at high-frequency  $C - V$  curves corresponds to fast interface traps, while the hysteresis width (calculated as the difference between down and up voltage shifts for depletion to accumulation and to inversion regions) corresponds to slow border traps. These shifts depend on the number of trap states and their energy levels. The fixed oxide traps contributed to the parallel shift of  $C - V$  curves, without any hysteresis effect.

Figure 2.1.: Ideal  $C - V$  curves (black line) and shifted  $C - V$  curves (green and red lines). The solid colored lines represent the up-gate voltage sweep, and the dashed line represents the down-gate voltage sweep. Hysteresis widths  $\Delta V_{H}^{d-a}$  and  $\Delta V_{H}^{d-i}$  are the differences between the up and down curves at the corresponding capacitance  $C_{cut}$ . It was assumed that the flatland voltage  $\Delta V_{fb}$  and threshold voltage  $\Delta V_{th}$  shifts, together with the hysteresis  $\Delta V_{H}$ , were due to charge trap kinetics at the 4H-SiC/SiO<sub>2</sub> interface and in the oxide.

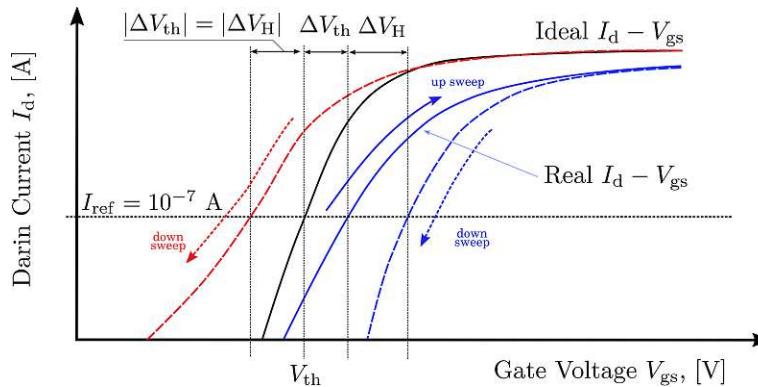

## 2.2. Hysteresis in the $I_d - V_{gs}$ Characteristics of MOSFETs Devices

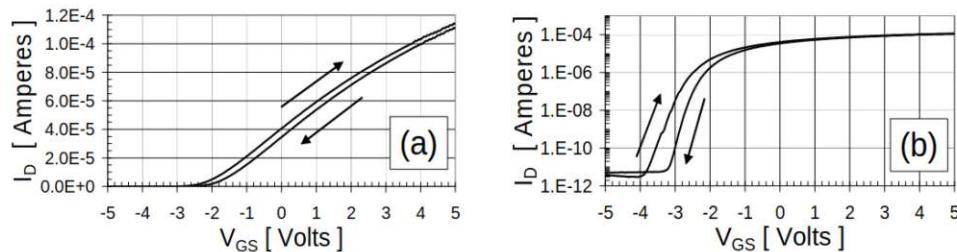

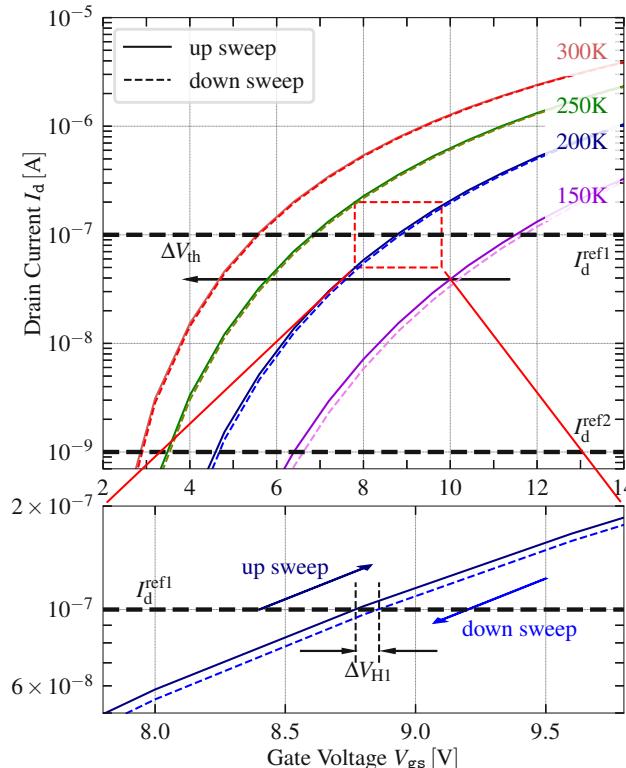

The fast and ultrafast  $I_d - V_{gs}$  up- and down- (or back-and-forth) characteristics may have a hysteresis effect (see Fig. 2.2). As in  $C - V$  curves, this was due to the oxide-trap charging effect [12], [40].  $\Delta V_{th}$  and  $\Delta V_{H}$  depend on the trap type and measurement conditions, such as the sweep rate, sweep gate voltage range, and temperature. If the up-gate voltage sweeps in the positive direction, we have a positive  $V_{th}$  or positive-bias temperature instability (PBTI) in the nMOSFET. Conversely, if has a more negative starting gate voltage, we have a negative bias temperature instability or NBTI when  $V_{th}$  shifts toward lower gate voltages. The absolute hysteresis width was calculated as the difference between the downward and upward absolute voltage shifts of the reference drain currents.

Figure 2.2.: Ideal  $I_d - V_{gs}$  curves (black line) and shifted  $I_d - V_{gs}$  curves (blue and red lines). The absolute hysteresis width  $|\Delta V_H|$  was calculated as the difference between the down- (dashed line) and up- (solid line) absolute voltage shifts  $|\Delta V_{th}|$  at the reference drain current ( $I_{ref} = 10^{-7} \text{ A}$ ). For NBTI,  $\Delta V_{th}$  is negligibly small (not plotted) and  $|\Delta V_{th}| \approx |\Delta V_H|$ .

For the PBTI, the hysteresis is due to acceptor-like traps located close to the conduction band. For NBTI, the charge trapping kinetics are more complicated, and it is assumed that this is due to neutral traps with energy levels in the middle of the 4H-SiC bandgap, which can capture or emit electrons or holes. The final hysteresis width depends on the net charges in the occupied acceptor- or donor-like defects under PBTI and NBTI conditions [89]. The subthreshold slope  $SS = \partial V_{gs} / \partial \log(I_d)$  is another critical parameter for switching between the ON and OFF states within a small gate bias range.

### 2.3. Hysteresis at Fast Bipolar Switching

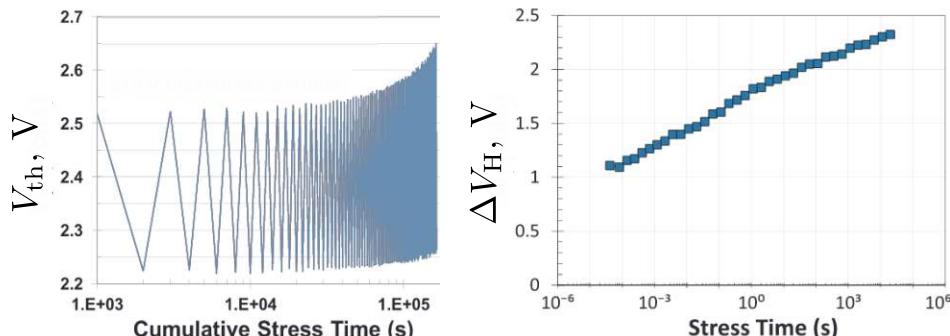

Figure 2.3.: Right: The constant back-and-forth bias-temperature stress under positive gate bias (+15 V), followed by 1000 s under negative gate bias (-15 V), repeated over and over, at 150 °C.  $V_{th}$  slowly increases and drifts in the positive direction because of the activation of additional near-interface oxide traps.  $V_{th}$  was calculated by determining the change in voltage for a constant current. Left: Example of increasing the hysteresis width at stress time owing to a back-and-forth gate bias stress sequence. From Lelis A. J., et al. "SiC MOSFET threshold-stability issues." *Materials Science in Semiconductor Processing* (2018), 78, pp.32-37 [90].

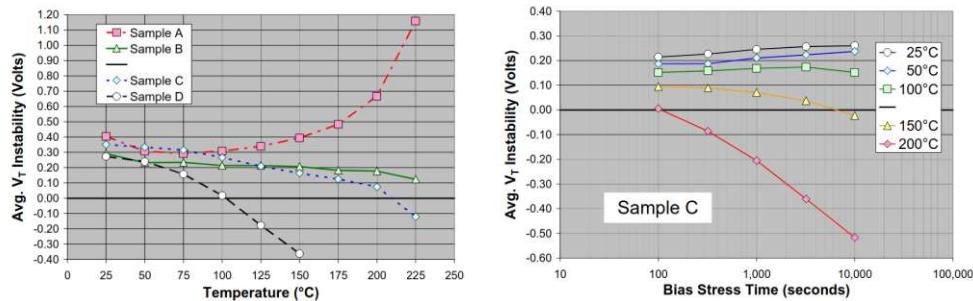

The hysteresis width at back-and-forth, or bi-polar stress, increases in comparison with the stress at one polarity (see Fig. 2.3, left [90]). It also increases for two different  $V_{\text{high}}$  and  $V_{\text{low}}$  combinations of the AC signal (as in gate switching instability (GSI)) [91]. The magnitude of this  $V_{\text{th}}$  instability also increased with increasing applied gate bias stress (see Fig. 2.3, right). Because the devices have different faces,  $\Delta V_{\text{th}}$  may behave differently over time. For example,  $\Delta V_{\text{th}}$  shifts more with an increasing magnitude of the positive gate bias stress, whereas  $\Delta V_{\text{th}}$  quickly saturates with an increasing magnitude of the applied gate bias during negative bias stress. This process is generally reproducible [90].

## 2.4. Correlation Between Bias Temperature Instability and Hysteresis

BTI is an important degradation effect in 4H-SiC devices. This phenomenon manifests as the capture of charges at both pre-existing and newly formed defects within the oxide layer or the interface of MOS devices when subjected to elevated bias voltage and temperature conditions [92]. At BTI, the device threshold voltage  $|\Delta V_{\text{th}}|$  (or  $|\Delta V_{\text{fb}}|$  in  $C - V$ ) increases, whereas the gate leakage is enhanced, resulting in an increase in circuit power consumption [16]. The positive shift in  $\Delta V_{\text{th}}$  is expected to increase the on-state resistance and degrade performance. [16], [28], [29].

The hysteresis phenomenon is attributed to the same charge-trapping mechanism observed in BTI. This is because not all charges are emitted during the reverse- or down-gate voltage sweeps. Similar to the BTI, the hysteresis width is influenced by measurement parameters such as the sweep rate, temperature, and sweep range.

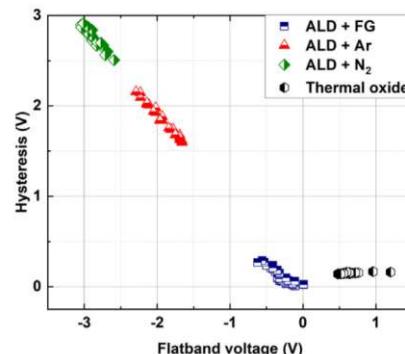

The hysteresis width and threshold voltage/flat band shifts were fully correlated, even under different conditions, as shown in Fig. 2.4 [93], [94].

Figure 2.4.: Example of the correlation between  $\Delta V_{\text{H}}$  and  $\Delta V_{\text{fb}}$  plotted for 50 MOSCAPs per different sample and different POA. Based on Renz A. B., et al. "The improvement of atomic layer deposited  $\text{SiO}_2/4\text{H-SiC}$  interfaces via a high temperature forming gas anneal." *Materials Science in Semiconductor Processing* (2021), 122, p.105527 [93].

However, it should be noted that the observed hysteresis differs from the classical BTI and should not be classified as a degradation. This phenomenon is both reversible and reproducible, and does not increase after the end of life [91], [95].

## 2.5. State of the Art and Thesis Outline

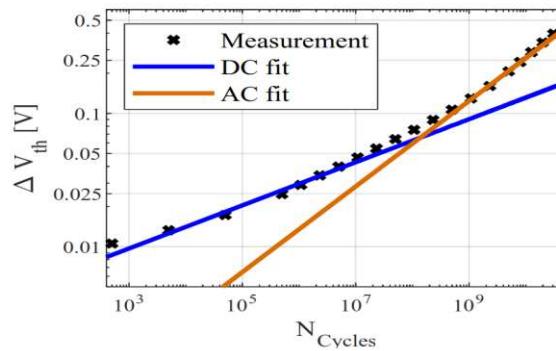

Utilizing the NMP theory for oxide and interface defects, along with the SRH theory for interface defects in lateral and trench 4H-SiC MOSFETs, combined with device simulation in modern TCAD frameworks, charge trapping has been recognized as the principal mechanism responsible for hysteresis width and BTI.

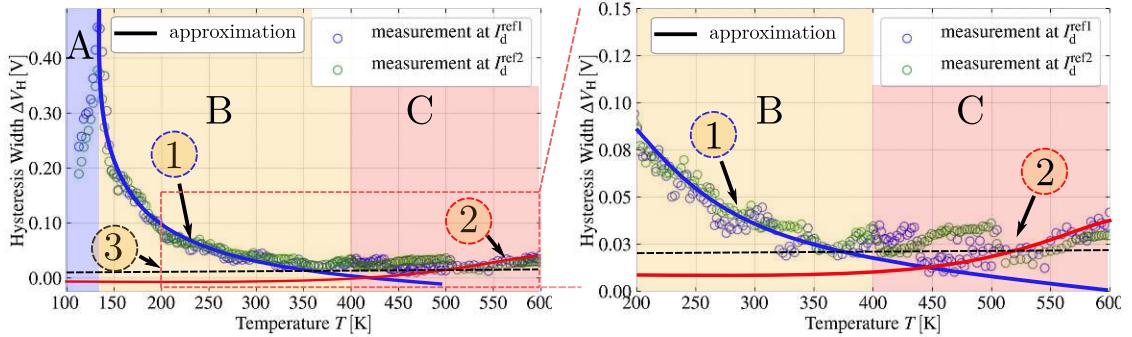

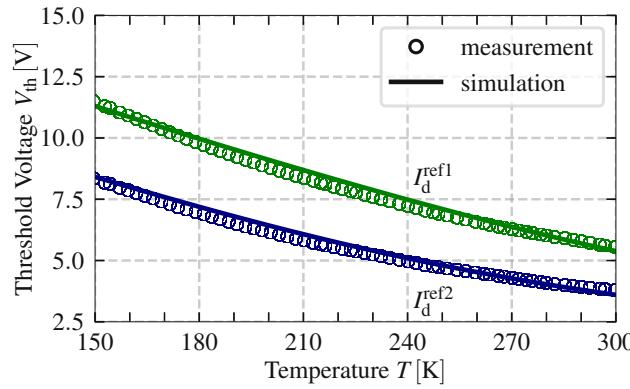

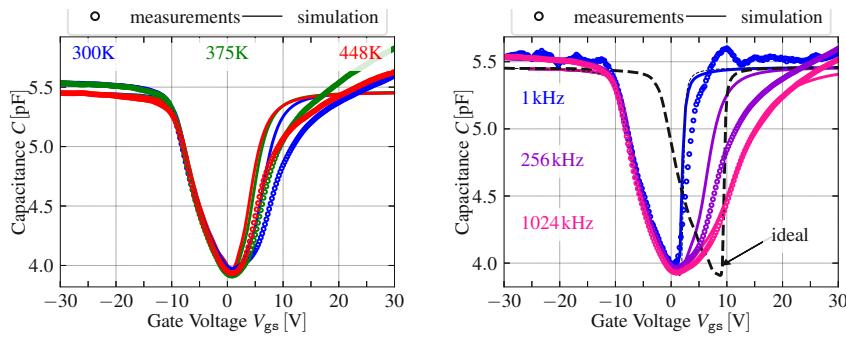

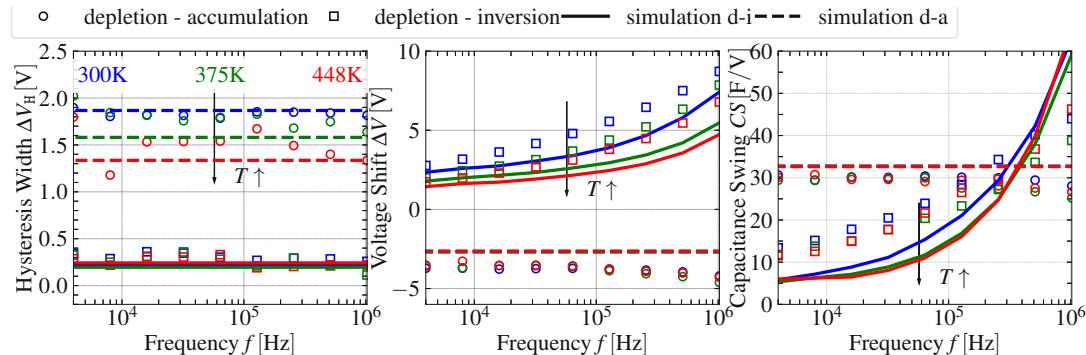

Existing models assume that the fluctuation of current-voltage characteristics is predominantly influenced by interface traps. However, the hysteresis width was not accurately simulated over a wide temperature range. Simultaneously, they depict the experimental curves and BTI for ambient and higher temperatures, specifically within the region 300–500 K. In this study, we extended the temperature range from 100 K to 600 K to compare the measured hysteresis widths in the  $I_d - V_{gs}$  curves with those of the simulations. At the same time, a comprehensive study of the hysteresis width in the  $C - V$  curves of lateral MOSFETs has not yet been conducted.

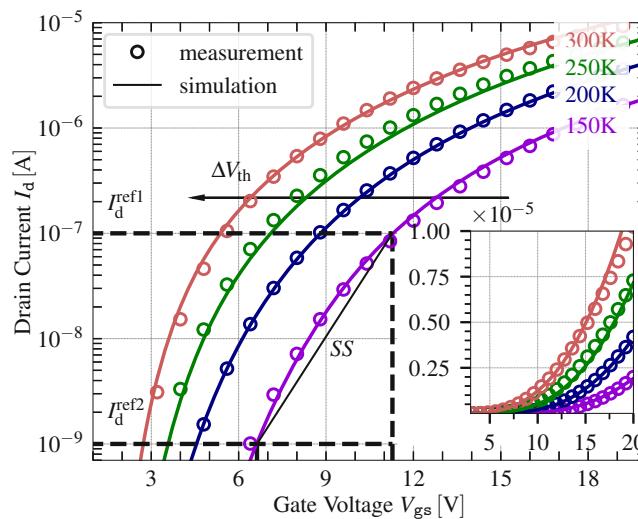

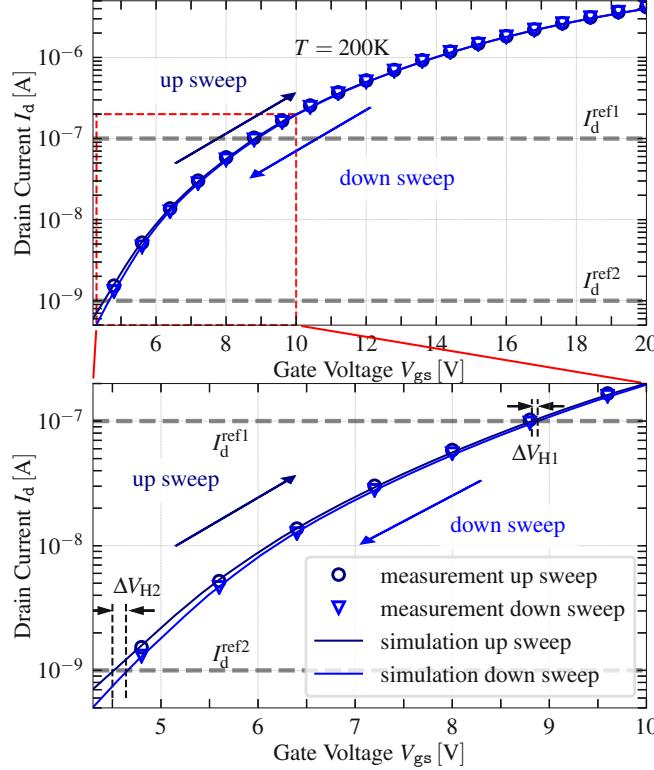

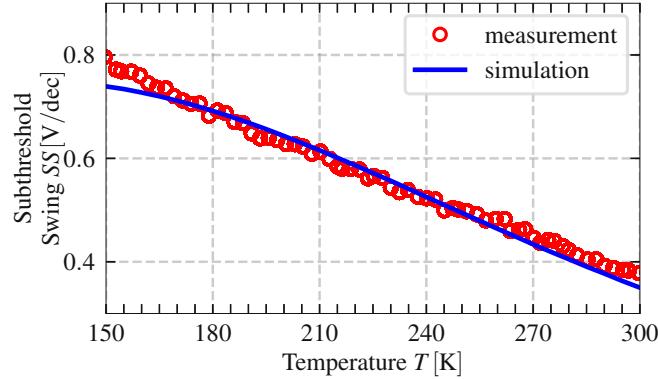

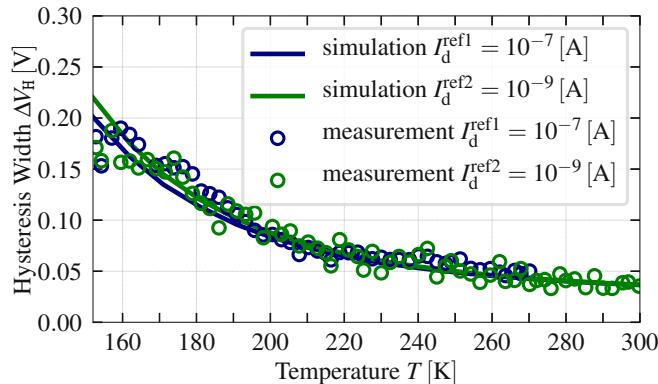

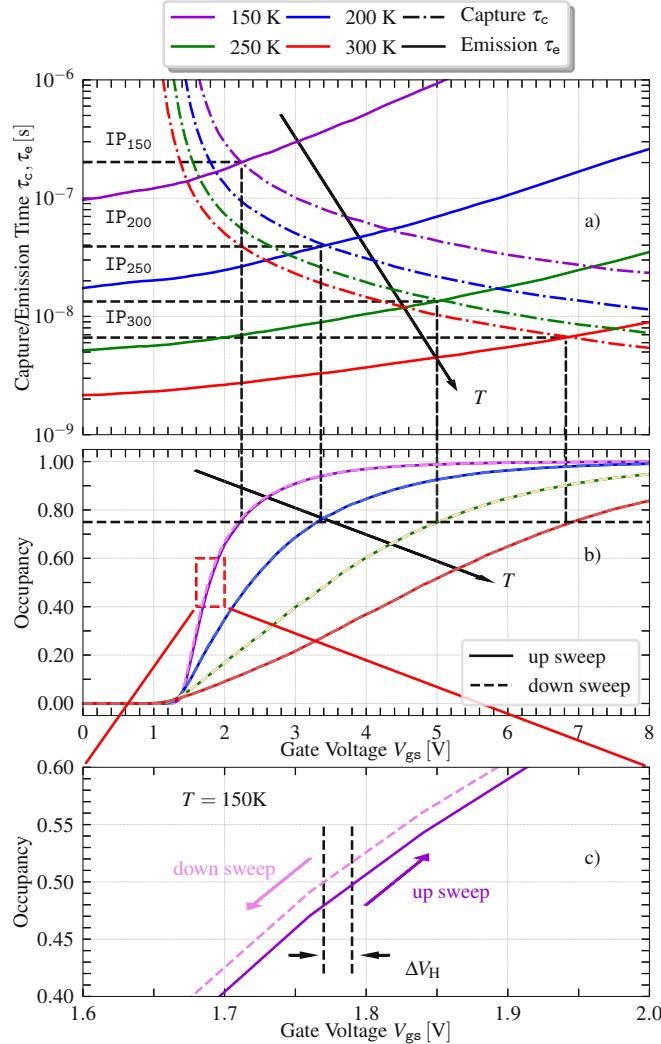

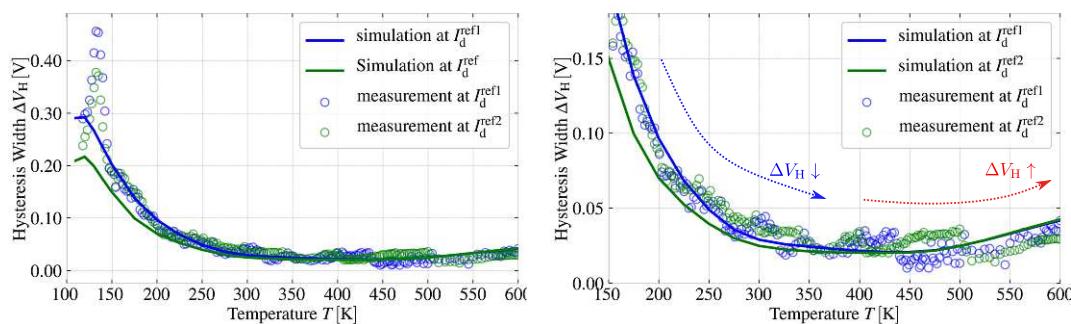

In this study, the hysteresis width, BTI, and subthreshold voltage slope of the  $I_d - V_{gs}$  characteristics of lateral 4H-SiC MOSFETs across a temperature range of 150–300 K and the hysteresis width from 100 K to 600 K, incorporating an additional amphoteric  $P_b$  or  $P_{bC}$  trap type, were investigated. The hysteresis width and stretch-out effect of  $C - V$  were simulated across a broad frequency range from 1 kHz to 1024 kHz and at elevated temperatures of 300 K, 373 K, and 448 K, incorporating an acceptor-like trap type at the mid-gap. To fit the  $I_d - V_{gs}$  curves of the 4H-SiC MOSFETs across multiple cycles at room temperature, a unique trap system featuring donor-like traps was positioned slightly below the mid-gap. This system was further adapted to simulate the  $C - V$  curves by including a high concentration of donor-like traps exponentially distributed from the valence band. The trap concentrations are lower than those in the conduction band, resulting in a higher channel mobility for trench devices; however, the hysteresis width is wider because of the larger concentrations of border traps positioned below the mid-gap compared with lateral devices.

Chapter 1 presents an overview of the advantages of using SiC as a substrate material in power MOSFETs, by detailing its material features. The latest SiC MOSFET structures are briefly explored, followed by an introduction of various SiC/SiO<sub>2</sub> interface properties resulting from different crystal orientations.

Chapter 2 presents an overview of reliability concerns. Specifically, the hysteresis width, BTI, and GSI in the  $I_d - V_{gs}$  curves and their interrelations, as well as the hysteresis width and stretch-out effect of the  $C - V$  curves.

Chapter 3 contains an overview of the measurement techniques used to investigate SiC/SiO<sub>2</sub> interface properties.

Chapter 4 defines the many reliability concerns observed in MOSCAP across planar, lateral, and trench MOSFETs, considering different facets, substrate types, measurement settings, oxide thicknesses, and POAs. Preliminary hypotheses regarding the trap type, density of states, and anomalous hysteresis width at high temperatures were reviewed.

Chapter 5 provides an overview of trap kinetics modeling approaches addressing reliability concerns related to pure SiC/SiO<sub>2</sub> interface quality is described in depth.

The two-state NMP model, which is extensively utilized for characterizing charge transfer reactions at defects, was employed and compared with alternative models. The specific impact of the hysteresis width on each NMP parameter was examined.

Finally, Chapter 6 describes the findings of the investigations conducted in this study. First, the hysteresis width, BTI, and subthreshold slope of the lateral MOSFETs within the temperature range of 150–300 K were reported using the NMP model for slow traps and the SRH models for fast traps. Second, the simulation of the hysteresis width of lateral MOSFETs across the temperature range of 100 K to 600 K was expanded and effectively modeled using the addition trap type. Third, the hysteresis width and stretch-out effect on the capacitance-voltage characteristics of the lateral MOSFETs were analyzed across different frequencies and temperatures. The incorporation of slower acceptor-like border traps along the  $\text{SiO}_2/\text{SiC}$  interface located at the midpoint of the 4H-SiC bandgap was implemented. In addition, the hysteresis in  $I_d - V_{gs}$  of the trench MOSFETs across numerous cycles and in the  $C - V$  curve was examined by investigating a unique trap system resulting from varying crystal faces.

Finally, the conclusions and outlook are presented. The potential uses and extensions of the proposed modeling method are described.

### 3. Measurement Techniques for Investigating SiC/SiO<sub>2</sub> interface Properties

Various measurement techniques and instruments have been developed to investigate the reliability of 4H-SiC MOSFETs. Many measurement parameters, including timing (measurement speed and delay), biasing range and polarity, and temperature, strongly influence the observed  $V_{th}$  shift. This indicated that the approach used in the measurements played a significant role in our investigation. These measurements can yield contradictory results when the initial state of the trap system is unknown. 4H-SiC, a wide-bandgap semiconductor, is well-suited for power applications that require operation at elevated temperatures, and the process of turning latent defects into active traps is accelerated.  $V_{th}$  in 4H-SiC MOSFETs at positive gate bias stress shifts positively, whereas it shifts negatively at negative gate bias stress. It follows that in most cases, these shifts are reversible and impermanent.

Because we have interface traps, fixed charges, oxide traps, near interface traps, or mobile ions of traps, separating the types of charges is difficult using conventional analysis techniques, such as  $C - V$  and  $I_d - V_{gs}$ . For example, all types of charges will shift the flatband and threshold voltages, but the oxide and interface traps will also stretch the  $C - V$  curve and subthreshold slope characteristics of the MOSFET  $I_d - V_{gs}$ . To directly analyze the number of switching oxide traps, the stretch out of the subthreshold  $I_d - V_{gs}$  characteristics of the MOSFET during the up- and down-stress threshold voltage instability was measured [96]. To investigate the significant threshold voltage shift and increasing hysteresis width due to fast sweeping down, fast switching (typically faster than 15  $\mu$ s) was used. In this section, we discuss and compare the most widely used schemes.

#### 3.1. Fast and Ultra-fast $I_d - V_{gs}$ Measurement Techniques

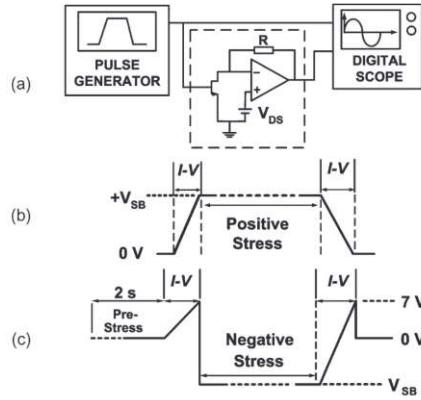

Initially, adapted fast  $I_d - V_{gs}$  measurement techniques for investigating SiC MOSFET were used by M. Gurfinkel, A.J. Lelis *et al.* [12], [89], [97], [98]. In the measurement scheme, the drain current was measured using an oscilloscope and generator, as shown in Fig. 3.1. The hysteresis width of  $I_d - V_{gs}$  can be measured as the difference between the down- and up-gate-voltage sweeps. The fast  $I_d - V_{gs}$  measured curves depend on the  $V_{gs}$  speed ramp and the bipolar DC stress.

Figure 3.1: . (a) Schematic of the fast  $I-V$  measurement setup. (b) Positive-bias stress pattern. (c) Negative-bias stress pattern. Based on Gurfinkel et al. "Characterization of Transient Gate Oxide Trapping in SiC MOSFETs Using Fast  $I - V$  Techniques." IEEE Trans. Electron Devices (2008), p 2005 [98].

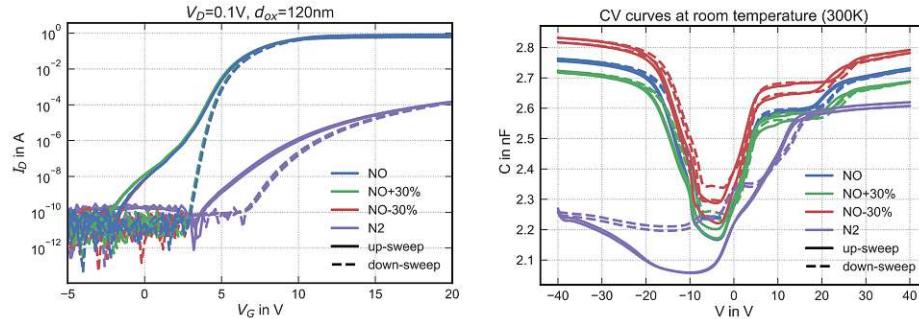

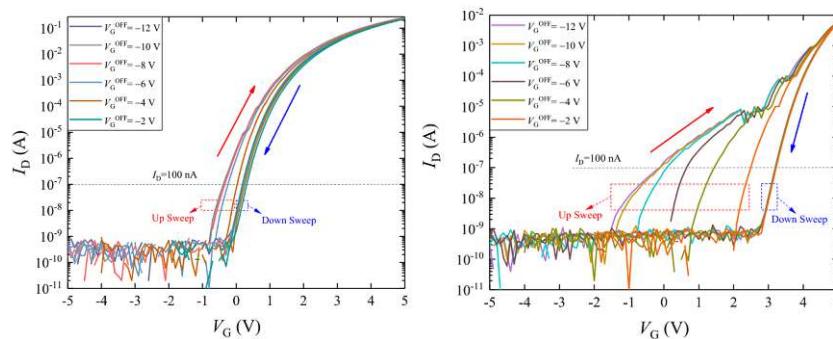

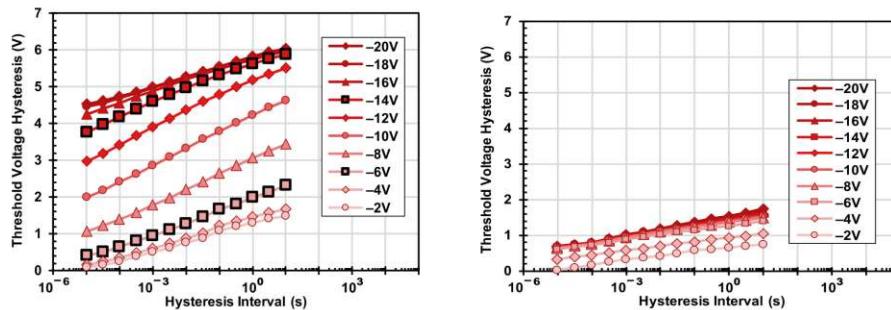

### 3.2. Hysteresis Measurements at $I_d - V_{gs}$

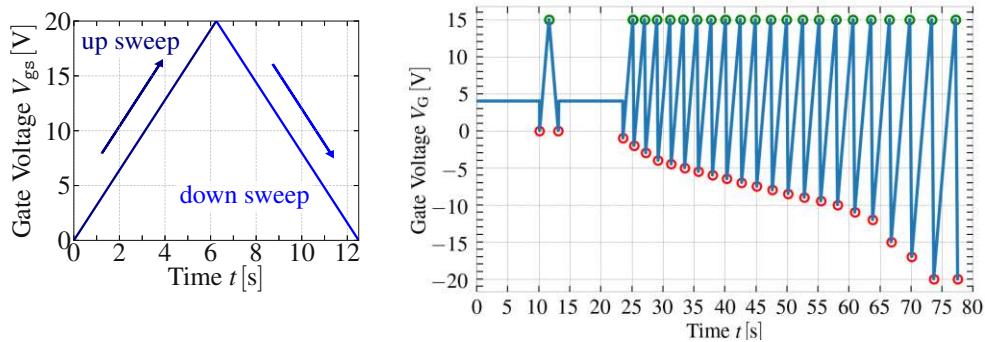

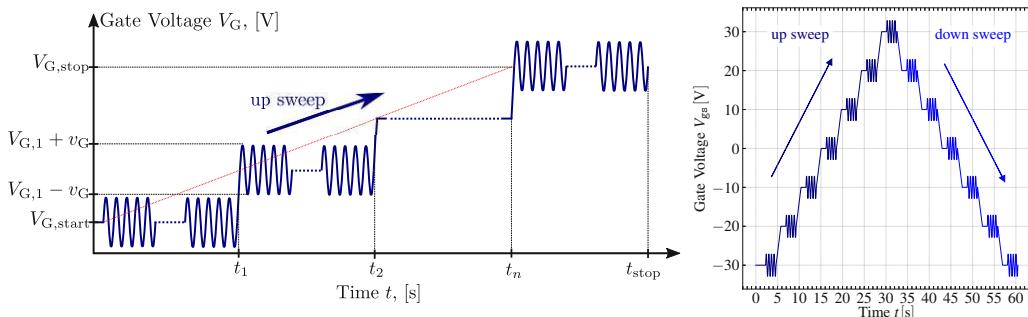

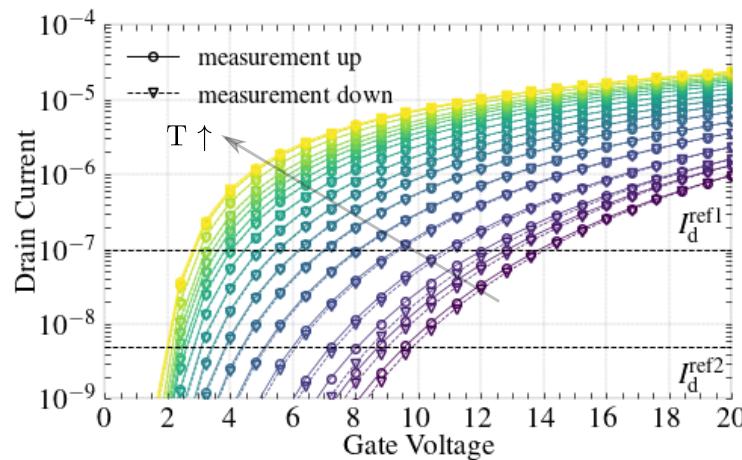

Using this device characterization method, the gate voltage was swept up and down during the recording of  $I_d$ . Typically, one sweep cycle is used with long precondition pulses to avoid a cumulative effect and significant distortion, as shown on the left in Fig. 3.2. However, to understand the long-term trap behavior, several sweep cycles were applied (see Fig. 3.2, right). The one cycle  $I_d - V_{gs}$  curves were measured at a fixed drain voltage of  $V_{ds} = 0.1$  V while  $V_{gs}$  is swept up and down within the range of 0 to 20 V at a sweep rate of 3.2 V/s, see Fig. 3.2, left. A constant step width of 0.8 V was used for the gate bias.

Figure 3.2: Left: A method for sweeping the gate voltage during  $I_d - V_{gs}$  measurements of planar 4H-SiC MOSFETs. The up sweep curve (dark blue) starts at 0 V. Right: An extended gate voltage up and down sweep of 21 cycles with an initial pre-stress signal was used for trench 4H-SiC MOSFET  $I_d - V_{gs}$  measurements. The final gate voltage was -20 V and the starting voltage became more negative in each cycle [99].

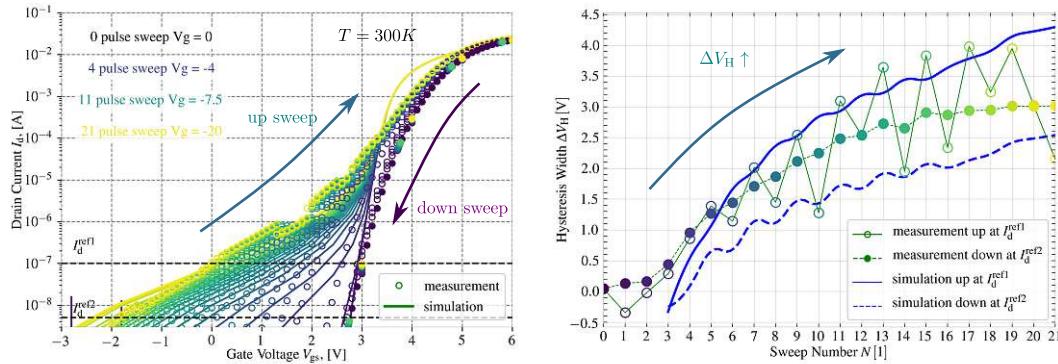

Two hysteresis widths,  $\Delta V_{H1}$  and  $\Delta V_{H2}$ , are defined as the difference between up and down  $\Delta V_{th}$  values corresponding to the two reference drain currents ( $I_d^{\text{ref1}} = 10^{-7}\text{ A}$  and  $I_d^{\text{ref2}} = 10^{-9}\text{ A}$ , see Fig. 6.1). The hysteresis width was extracted for operating temperatures between 100 and 600 K [99].

At multiple cycles, the gate voltage  $V_{gs}$  sweep started at a positive gate bias stress of 4 V during 10 s (see Fig. 3.2, right). We then applied a zero pulse with a sweep rate of  $1\text{ V s}^{-1}$  for up- and down-gate voltages within the range of 0–15 V. After the second stress period, we applied the next 21 pulses with a sweep rate of  $1\text{ V s}^{-1}$  for up and  $10\text{ V s}^{-1}$  for down gate voltages, and every period changed the starting negative gate voltage to the same final positive gate voltage.

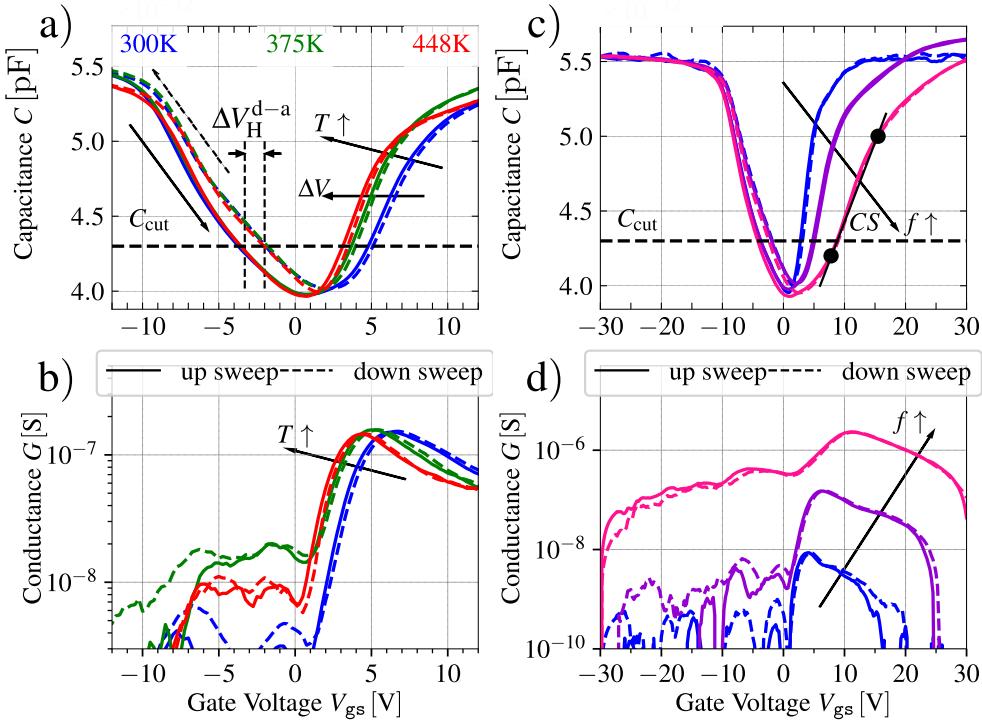

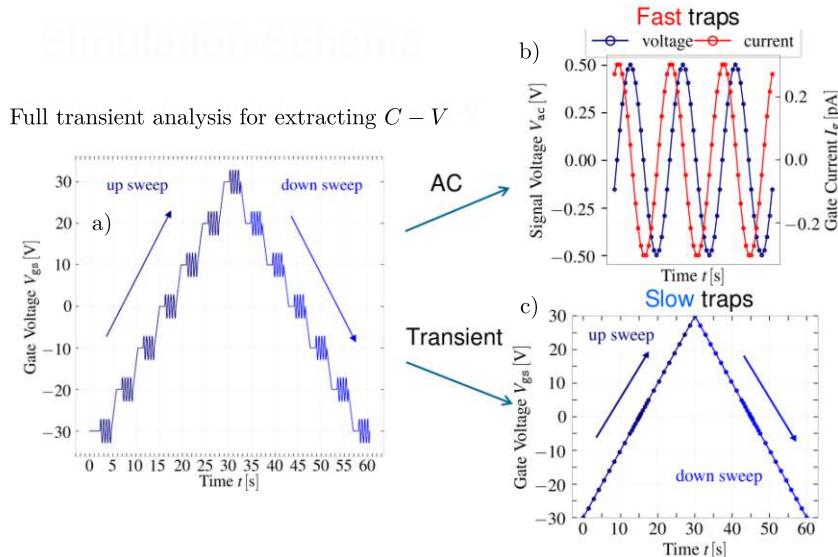

### 3.3. “Up-and-Down” $C - V$ Measurement and Impedance Analysis

$C - V$  measurements are widely used to investigate the defect properties of MOS capacitance. An alternating current (AC) voltage of small amplitude, typically approximately 50 mV at a frequency of 100 kHz, was superimposed on a gradually varying direct current (DC) bias. Significant information can be derived from the  $C - V$  characteristics, including the flat-band voltage ( $V_{fb}$ ), threshold voltage ( $V_{th}$ ), bulk doping, and surface potential ( $\phi_s$ ). This information can be obtained either by measuring the displacement current during a gate voltage sweep (ramp-up method) or by superimposing a small AC signal onto the DC gate bias and measuring the AC current (impedance method), as shown in Fig. 3.3. Both MOSCAP and MOSFET devices can be used for  $C - V$  measurements.

Figure 3.3.: Left: Depiction of  $V_G$  waveform applied to the gate for  $C_{gb}$ . An up  $V_G$  sweep signal was applied to the gate to establish the MOS capacitor, followed by a high-frequency (10 kHz to 10 MHz) and low-amplitude  $v_g$  (50 mV). The AC signals were superimposed onto each  $V_G$  level, after which the AC current ( $i_B$ ) through the capacitor was measured to calculate capacitance. The same procedure was repeated during the downward  $V_G$  sweep (not plotted). The dashed red line represents sweep rate  $V_{G,n}/t_n$ . Right: Schematic of the gate voltage applied during impedance measurement. Both the small-signal and the gate voltage sweep are used in the transient analysis to investigate traps dynamics [100].

When MOSFETs are used, the source and drain contacts are typically grounded or

linked to the bulk. The main difference between MOSCAP and MOSFET devices is that in MOSFETs, the minority carriers necessary for inversion can be rapidly provided by the source and drain regions. This facilitates faster gate bias sweeps, in contrast to MOSCAP systems. The drawbacks of MOSFETs include supplementary parasitics resulting from the overlap between the source and drain areas with the gate, or other geometrical issues. MOSCAP structures have the added benefit of being predominantly one-dimensional, facilitating the use of easily understood and precise models for characterization. In up- and down- (or "back-and-forth" [101]) impedance measurements, full information regarding slow and fast traps can be investigated [102].

The small-signal method was employed for the measurement of the  $C - V$  and conductance-voltage ( $G - V$ ) curves. Equivalent circuit capacitance and conductance were configured in parallel. A sinusoidal small signal for each bias step, along with the gate voltage up and down sweeps, was employed to examine the trapping dynamics, as illustrated in Fig. 3.3, right [103], [104]. Gate voltage  $V_{\text{gs}}$  varied between  $-30 \text{ V}$  and  $30 \text{ V}$  at a rate of  $2.0 \text{ V s}^{-1}$ , as illustrated in Fig. 3.3. The measured small-signal amplitude was  $50 \text{ mV}$ , with a frequency range extending from  $4 \text{ kHz}$  to  $1024 \text{ kHz}$ . The time interval for each gate bias was  $0.13 \text{ s}$  and the delay between the upward and downward sweeps was  $12 \text{ ms}$ . The hysteresis width was determined for operating temperatures  $300 \text{ K}$ ,  $373 \text{ K}$ , and  $448 \text{ K}$  [100].

### Impedance Extraction

Detecting fast states necessitates very high-frequency measurements, which complicates the identification of defects owing to the series resistance and inductance [78].

The small signal impedance  $Z$  is given by the division of the complex values of the AC gate voltage  $v_g$  and bulk current  $i_B$ : [102]

$$Z = \frac{v_g}{i_B} \quad (3.1)$$

$$|Z| = \frac{|v_g|}{|i_B|} \quad (3.2)$$

$$\arg(Z) = \arg(v_g) - \arg(i_B) \quad (3.3)$$

Commercial impedance analyzers or  $C - V$  meters often give the impedance as values of an effective parallel or series  $R - C$  circuit:

$$Z = R_s + \frac{1}{jwC_s} \quad (3.4)$$

$$1/Z = 1/R_p + jwC_p \quad (3.5)$$

When the equivalent circuits accurately represent the setting, it is advisable to identify the complex impedance and thereafter compute the required  $C - V$  curves by utilizing the most appropriate equivalent circuit for a specific combination of the experimental setup, operating conditions, and device [102].

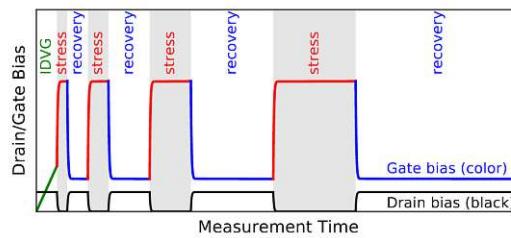

### 3.4. Measure-Stress-Measure Technique

The measureure-stress-measure technique or MSM is used for  $V_{th}$  shift measurement and is typically not used for hysteresis extraction. This method consists of a three phase: first, where the fresh device is measured; second, the voltage stress is applied; and third, the final measurements after stress. The stress and measurement phases can be repeated several times, often under severe conditions. In the extended MSM (eMSM) scheme during the measurement phase, additional important device characteristics are controlled, such as  $V_{th}$ , mobility, and channel conductivity, as shown in Fig. 3.4 [57], [102], [105], [106]. The measurements can also be performed at various temperatures.

Figure 3.4.: Typical for an eMSM sequence are the repeatedly applied phases of stress and recovery bias. After each cycle, the stress and recovery times were increased. It should be noted that the initial  $I_d - V_{gs}$  affects the charge state of the number of traps. From Waltl M. "Defect Spectroscopy in SiC Devices." IRPS (2020) [105].

### 3.5. The Fast $I_d$ Measurement Technique

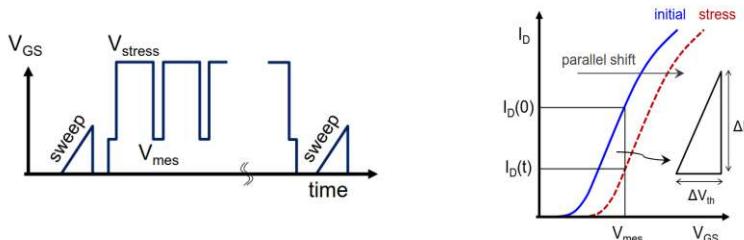

Using the fast  $I_d$  method,  $I_d$  was measured at  $V_{mes}$  as quickly as possible with no stress-off time, as shown in Fig. 3.5, right. The  $V_{th}$  shifts were extracted from the parallel  $I_d - V_{gs}$ .  $\Delta V_{th}$  can be simply computed from the  $I_d$  shifts in the linear area with the initial transfer conductance  $g_m$ , which represents the slope of  $I_d - V_{gs}$ , as shown in Fig. 3.5, left.

Figure 3.5.: Left: Schematic  $V_{gs}$  patterns of the fast  $I_d$  method in the PBTI tests. Right: Schematic of  $I_d - V_{gs}$  before and after PBTS and the calculation of the  $V_{th}$  shift in the fast  $I_d$  method. From Okunishi T., et al. "Reliability study on positive bias temperature instability in SiC MOSFETs by fast drain current measurement." Jpn. J. Appl. Phys., (2017) p. 04CR01-2 [107].

$$\Delta V_{\text{th}} = \frac{I_D(0) - I_D(t)}{g_m} \quad (3.6)$$

The fast  $I_d$  method is more precise than the standard method because of its ability to reduce measurement time. Nevertheless, this method is not infallible, as it allows for a measurement delay of several milliseconds [107]. The fast  $I_d$  method was used to investigate PBTI at different temperatures [107].

### 3.6. Bipolar AC Gate Bias Stress Test

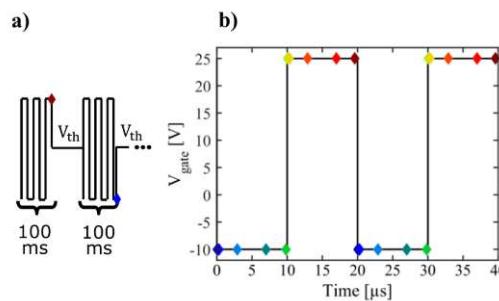

This measurement technique was used to measure the threshold voltage shift and hysteresis width at various temperatures during a bipolar AC signal in the range of 50 kHz [91], [108]. As described in [108] the measurement delay should be shorter than the period time; for measuring  $V_{\text{th}}$  the AC signal must be interrupted at several points, and the shortest possible measurement delay with our setup is  $t_d = 1 \mu\text{s}$ , see Fig. 3.6.

Figure 3.6.: a) The AC stress was interrupted at different points for the threshold voltage measured from  $1 \mu\text{s}$  to  $10 \text{ ms}$  recovery times. (b) Example of a  $50 \text{ kHz}$  bipolar AC signal with different points of interruption, as described in (a). From Puschkarsky K., et al. "Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability." TED, (2019) p. 4609 [91].

### 3.7. Charge-Pumping Technique

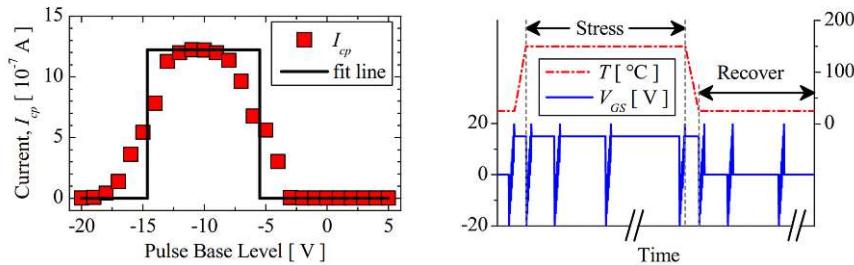

The standard charge-pumping method uses a constant pulse amplitude while sweeping the base level. The maximum charge pumping current  $I_{\text{cp}}$  was measured, and  $V_{\text{th}}$  and  $V_{\text{fb}}$  were estimated by the positions of the rising and falling edges of the signal, respectively. The typical pulse frequency was 500 kHz, where the measured  $I_{\text{cp}}$  was primarily due to the fast interface traps, as shown in Fig. 3.7. This method was employed to investigate the kinetics of the interface traps and their impact on the  $\Delta V_{\text{th}}$  shift during BTS. At a gate bias of  $150^\circ\text{C}$ , an increase in the charge-pumping current

over time indicates the formation of acceptor-like interface traps (or near-interface oxide traps) responsible for the positive drift under these conditions [44].

Figure 3.7.: Left: Charge pumping current  $I_{cp}$  versus the pulse base level (red squares), along with a fit line used to determine the number of charge pumping states  $N_{cp}$ ,  $V_{th}$ , and  $V_{fb}$  (solid black line). Right: Schematic of the stress-and-measure sequence showing profiles of temperature (dashed red line) and gate bias (solid blue line) as a function of time. From Habersat D.B., et al. "Evaluation of PBTS and NBTS in SiC MOS Using In Situ Charge Pumping Measurements." *MSF*, (2013) p. 546 [44].

### 3.8. The Pump-Probe Measurement

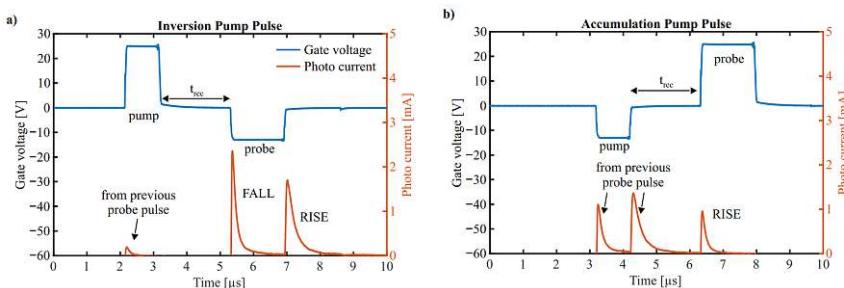

The pump-probe measurement investigates the correlation between the threshold voltage shift recovery and the number of emitted photons.

Figure 3.8.: Measured photocurrent in response to a pump-probe pulse scheme at the gate for inversion (a) and accumulation (b) pump pulses, respectively. A pump pulse provokes charge trapping at defects, whereas the probe pulse provides opposite charge carriers, leading to trap-assisted recombination and emission of photons. From Feil M.W., et al. "Optical Emission Correlated to Bias Temperature Instability in SiC MOSFETs." *IRPS*, (2022) p. 3B.1-4. [109].

Using a silicon photomultiplier (SiPM) in the bipolar AC gate bias stress test, photon emission was measured at both the rising and falling edges of the gate signal, represented by the SiPM current. The field effect at the semiconductor-insulator interface induces out-of-equilibrium occupancy of defects by applying a 1  $\mu\text{s}$  pump pulse to the gate. The pump pulse can be positive (inversion) or negative (accumulation). The pump pulse is succeeded by a recovery phase of duration  $t_{rec}$ , during which the out-of-equilibrium state may return to equilibrium at a gate voltage of 0 V, as shown in Fig. 3.8 [109], [110].

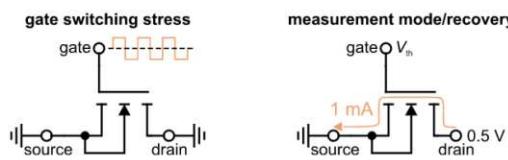

### 3.9. Gate-Switching-Stress Test

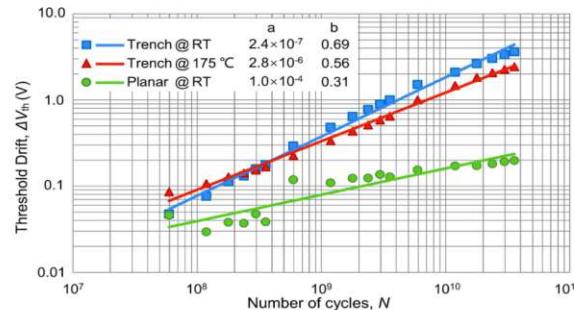

A recent study (Puschkarsky *et al.*, Feile *et al.* [55], [56], [59], [111], [112]) explained gate switching instability (GSI), a phenomenon in which bipolar alternating gate voltages induce an increased threshold voltage drift compared with static gate voltage measurements (DC-BTI/DC-HTGS) [14], [15], [76], [113]. In certain applications, 4H-SiC MOSFETs require continuous gate-voltage switching at frequencies of hundreds of kilohertz. In this operational mode, the positive gate bias significantly exceeded the threshold voltage during the high phase ( $V_{GH} \gg V_{th}$ ), whereas the negative gate bias substantially fell below the flat-band voltage in the low phase ( $V_{GL} \ll V_{fb}$ ). For this, an alternating current high-temperature gate-bias stress (AC-HTGS) test or gate switching stress (GSS) test, which covers all gate oxide drift phenomena, was created, as shown in Fig. 3.9 [55].

Figure 3.9.: Schematic illustration of GSS and the measurement of  $V_{th}$  via a feedback loop. During stress, the MOSFET is switched in bipolar mode while keeping both the drain and source terminals grounded. When measuring the  $V_{th}$ , a feedback loop forces a constant drain-source current ( $I_{DS}$ ) by regulating the gate voltage. From Feil M.W., et al. "Gate Switching Instability in Silicon Carbide MOSFETs—Part I: Experimental." TED, (2024) p. 4211. [114].

Both BTI and GSI occur and superimpose on the total  $\Delta V_{th}$ :

$$\Delta V_{th} = \Delta V_{th}^{\text{BTI}}(t_{\text{stress}}) + \Delta V_{th}^{\text{GSI}}(n); n = t_{\text{stress}} \cdot f_{\text{SW}} \quad (3.7)$$

where  $n$  is the switching cycle,  $t_{\text{stress}}$  is the fixed stress time. The GSI component depends on the cumulative number of switching cycles  $n$ , whereas the frequency-independent BTI component still depends on  $t_{\text{stress}}$  [114].

### 3.10. Summary

This chapter presents typical techniques for MOSFET parameter extraction, emphasizing the characterization of the hysteresis width, bias temperature instability, and gate-switching instability in large-area transistors. In this research, two main measurement techniques have been employed: "up-and-down"  $C - V$  measurement and impedance analysis and hysteresis measurements at  $I_d - V_{gs}$ .

## 4. Instability of 4H-SiC MOSCAPs and MOSFETs

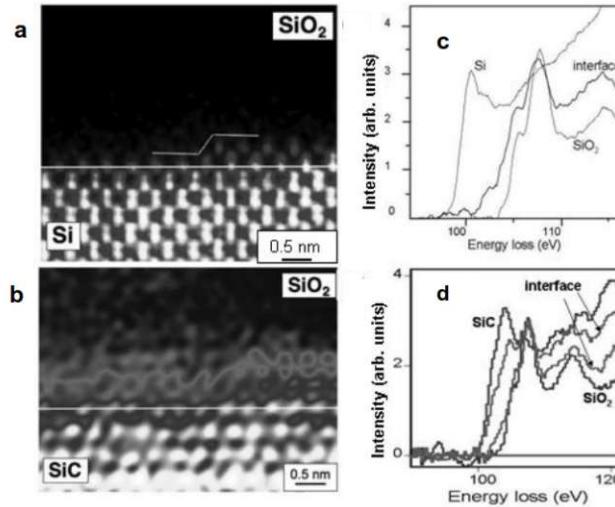

In this chapter, a review of previous investigations on the measured instability of MOS capacitors (MOSCAPs) and MOSFETs found in the literature is presented. Since 1996, investigations on SiC/SiO<sub>2</sub> interfaces have grown rapidly. The  $C - V$  analysis of MOSCAPs was used to identify the trap density of states (DOS) responsible for the "stretch-out" effect, shift in  $V_{fb}$ , and hysteresis phenomenon. The different interface properties were dependent on the SiC polytypes and crystal faces upon which the oxide was deposited. The technique of growth and post-oxidation annealing, along with channel properties such as the concentration and conduction type, contribute to the variation in the trap DOS. In addition to electrical measurements, optical measurements, such as photoemission of electrons and spectral analysis, were used to examine the trap system. With the possibility of manufacturing the first SiC MOSFETs, the instability of the transient  $I_d - V_{gs}$  characteristics, such as  $V_{th}$  shift and hysteresis width, was investigated. The effective operation of both n-channel and p-channel MOSFETs is significantly influenced by Bias Temperature Instabilities (BTI), which represent a critical reliability issue. By applying bipolar stress, both positive and negative BTI values were obtained. With increasing switching frequency of the AC signal, extra Gate Switching Instability (GSI) plays a significant role. The instability in the measured data from identical devices using different methods should be consistent for the same trap types and DOS. Differences may arise in the sensitivity of the measurement techniques. This indicates that all phenomena, such as BTI, HCD, hysteresis, and GSI, should be correlated, because the device under testing exhibits identical traps. Simultaneously, measurement parameters such as temperature, sweep rate, sweep range, high- and low-voltage levels, frequency, delay time, and preconditions significantly influence the measured data, and these effects must be clearly identified and considered. In addition, a transition layer at the border of SiC/SiO<sub>2</sub> was detected to investigate the spatial trap distribution and impurities in the oxide.

### 4.1. Hysteresis at MOSCAPs

MOSCAPs are essential in research and development as they provide a direct, dependable, and easy to use method to investigate the electrical characteristics of the SiC/SiO<sub>2</sub> interface, which is crucial for the performance and scaling of MOS devices. These fundamental structures usually include metal, oxide, and semiconductor layers. Their simplicity removes multiple complex variables and additional distortions, which makes them optimal for investigating the intrinsic characteristics of the interface.

The fundamental contribution of the SiC/SiO<sub>2</sub> interface investigations was made by Afanasév V.V. *et al.* [32], Kimoto T. *et al.* [83], Lelis A. *et al.* [101] and numerous other researchers and groups. In 2011 D. Habersat *et al.* and A. Lelis *et al.* improved the observation of SiC/SiO<sub>2</sub> oxide charge traps. Measurements utilizing the "back-and-forth"  $C - V$  technique exhibit more overall instability than  $I_d - V_{gs}$  and may correlate with measurements conducted using fast  $I_d - V_{gs}$ .  $C - V$  measurements are sensitive to traps situated within the midgap, thereby enabling this method to be more precise for evaluating the actual density of the trap states. "One-way negative bias-stress"  $C - V$  measurements indicate considerable instability when compared to one-way bias stress  $I_d - V_{gs}$  measurements. The net bias – stress shift or hysteresis is the difference between the up and down gate voltage sweeps at the reference flat-band capacitance for  $V_{fb}$  ( $C - V$ ) or current for  $V_t$  ( $I_d - V_{gs}$ ) [101]. Multiple studies have been conducted on samples with different properties.

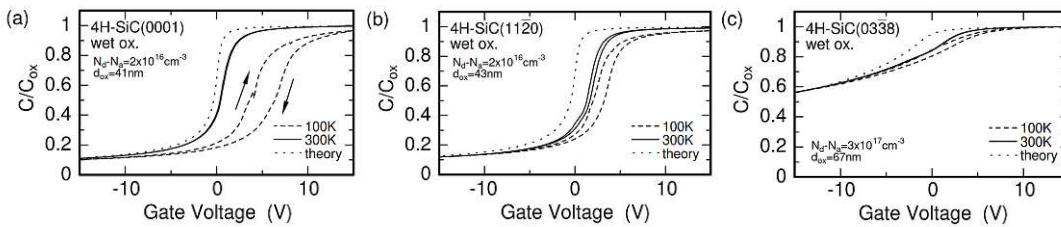

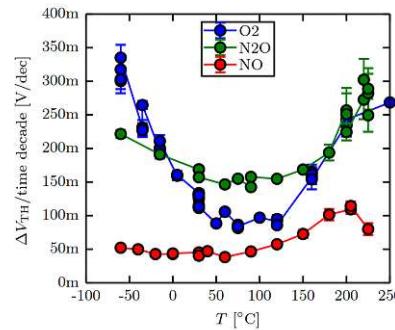

#### 4.1.1. Temperature Dependence of the Hysteresis Width at Various Faces

As mentioned before, there are various faces in 4H-SiC that have different properties. The hysteresis widths at different temperatures are shown in Fig. 4.1. Based on Yano H. *et al.*, the hysteresis for (0001) and (0338) was minimal (< 0.1 V), whereas 0.4 V was observed for (1120). At a low temperature of 100 K, both the flatband voltage shift  $\Delta V_{fb}$  and hysteresis  $\Delta V_H$  increase because of the interface states at shallow energy levels [7]. The shallow interface states located near the conduction band induce a positive flatband voltage shift owing to the electrons being trapped in these states, which remain for a long time and act as negative fixed charges. Some trapped electrons were slowly emitted throughout the voltage sweep in the capacitance-voltage measurements, even at low temperatures, resulting in hysteresis.

Figure 4.1.: High-frequency  $C - V$  characteristics of n-type 4H-SiC MOS capacitors on (a) (0001), (b) (1120), and (c) (0338) faces. Solid and broken curves are obtained at 300 and 100 K, respectively. The dotted curves indicate theoretical calculations. Injection-type hysteresis was observed. Note that the gentle slopes of the  $C - V$  curves for (0338) are due to a higher net donor concentration and thicker oxide than for (0001) and (1120). From Yano H., *et al.* "SiO<sub>2</sub>/SiC Interface Properties on Various Surface Orientations." *Mat. Res. Soc. Symp. Proc.*, (2003) p. K4.5.3 [7].

At room temperature, the emission time decreased, whereas the flatband voltage and hysteresis remained constant, indicating that defects were located close to the conduction band. The two additional faces demonstrated an increased flatband voltage shift of approximately 4.9 V and 4.4 V for (1120) and (0338), respectively. The increase

in the hysteresis was also dependent on the surface orientation. At 100 K, the hysteresis for (0001) increased to 2.4 V, whereas it remained negligible at 300 K. The hysteresis measured at 100 K for the (1120) and (0338) orientations was recorded as 0.9 V and 0.4 V, respectively, at 100 K [7], [36], [77].

With almost little hysteresis and a minor stretch out, the  $C - V$  curve for the (0001) face at 300 K indicates a low interface state density. In contrast, a significant increase in the stretch out near the accumulation region was also evident in the  $C - V$  curves measured at 77 K. With a maximum positive accumulation bias of 10 to 40 V in 5 V, the hysteresis increased; however, this was not observed at 300 K. The 4H-SiC bandgap is reduced from 3.3 eV to 3.2 eV from 80 to 300 K. A significant number of  $N_{it}$  shifts energetically above the conduction band as the bandgap shrinks, making it impossible for electrons to occupy at 300 K [34], [35], [115], [116], [117]. However, at low temperatures, the carrier concentration is reduced because of incomplete deep dopant ionization, and the semiconductor changes from a doped to intrinsic material [118] which leads to a reduction in the voltage shift [119].

Particularly for (0001) close to the conduction band edge,  $\Delta V_{fb}$  and hysteresis  $\Delta V_H$  are correlated with an increase in the interface state density (see Fig. 4.1). The trap parameters are provided in Table A.1 and explained in the relevant section.

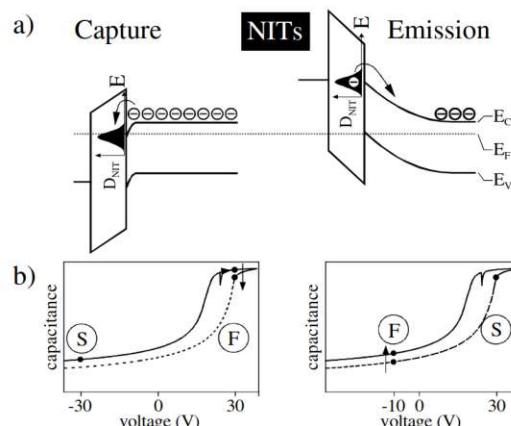

A preliminary schematic of the capture and emission processes of electrons and their influence on the hysteresis width in the  $C - V$  measurements is shown in Fig. 4.2.

Figure 4.2.: a) Band diagrams and b)  $C - V$  characteristics demonstrating the experimental situation for the capture and emission process of electrons. From Pensl G., et al. "Traps at the SiC/SiO<sub>2</sub>-Interface." *Mat. Res. Soc. Symp. Proc.*, (2001) p. H3.2.8 [36].

A sketch of the  $C - V$  diagram with the corresponding band diagram for the starting (S) and final (F) is presented in Fig. 4.2 (a) and (b), respectively. To determine  $\tau_c$  the voltage sweeps from the depletion (S) (which depends on the threshold voltage of the device) to the accumulation (F), and the number of charged electrons in  $N_{it}$  is measured. To determine  $\tau_e$  the voltage sweeps from accumulation (S) to depletion (F) and the emission of electrons from  $N_{it}$  are monitored. These measurements resulted in two time constants for emission and capture ( $\tau_e^1 = 59$  s,  $\tau_e^2 = 7.3$  s, and  $\tau_c^1 = 63$  s,  $\tau_c^2 = 6.8$  s), which means that two different distributions of  $N_{it}$  contributed to  $D_{it}$  [36].

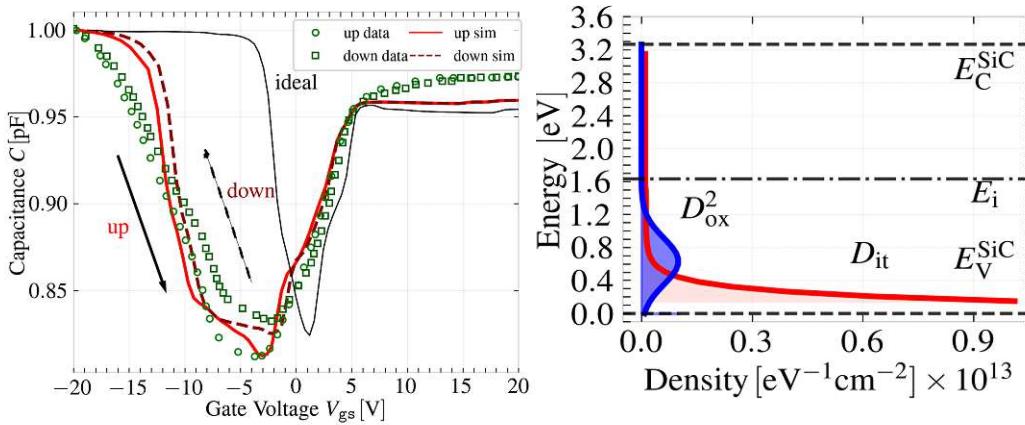

### 4.1.2. Anomalous Hysteresis Width at High Temperatures

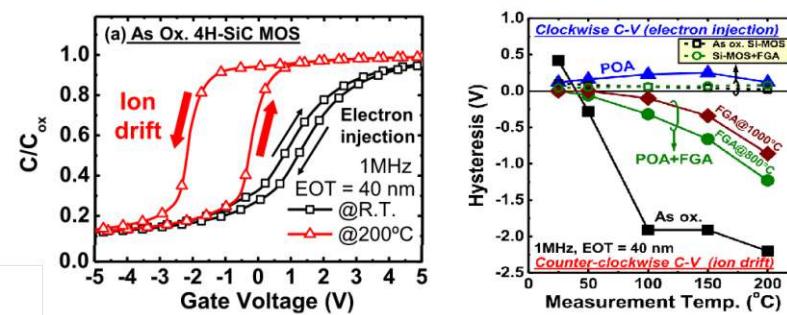

In 2012 Chanthaphan A. *et al.* [120] investigated the unusual intrinsic positive mobile ion effects of the 4H-SiC (0001) Si-face MOSCAPs. These phenomena have been observed mostly in MOSFET structures, leading to  $V_{th}$  shift and decrease in the hysteresis width at elevated temperatures [48], [121]. However, at some point, the hysteresis width increases, especially at very high temperatures [122], particularly at the Si face. The electron injection and ion drift effects were hypothesized to explain the clockwise (positive) and counterclockwise (negative) behaviors, respectively. Fig. 4.3 shows this bidirectional  $C - V$  curves measured at room temperature (black open squares) and 200 °C (red open triangles). When the measurement temperature was increased to 200 °C, the orientation of the  $C - V$  hysteresis reversed counterclockwise.

Figure 4.3.: Left: Bidirectional  $C - V$  curves obtained from a SiC-MOS capacitor with an as-oxidized thermal oxide.  $C - V$  measurements were performed at room temperature (black open squares) and 200 °C (red open triangles). The measurement frequency was 1 MHz for all the cases. Right: The temperature-dependent  $C - V$  hysteresis of the SiC-MOS capacitors (solid lines with filled symbols) depends on different POA and high-temperature forming gas annealing (FGA) conditions in comparison with the as-oxidized SiC capacitor (As ox.). From Chanthaphan A., *et al.* "Investigation of unusual mobile ion effects in thermally grown  $\text{SiO}_2$  on 4H-SiC(0001) at high temperatures." *Appl. Phys. Lett.*, (2012) p. 252103-3 [123].

Upon cooling to the normal temperature, the bidirectional  $C - V$  curve obtained for the exact capacitor reverted entirely to a clockwise orientation, indicating that the influence of mobile ions is significant only at elevated temperatures [120], [123].

The SiC MOSCAPs that received PBTS before wet etching exhibited a marked negative  $V_{fb}$  shift and counterclockwise  $C - V$  hysteresis, comparable to that of the as-fabricated capacitor at 200 °C. In contrast, no hysteresis at NBTI was observed at 200 °C. This effect depends on the defect passivation and is comparable to the effect of hydrogen treatment. Forming gas annealing (FGA) induces positive mobile ions in oxides [124], [125].

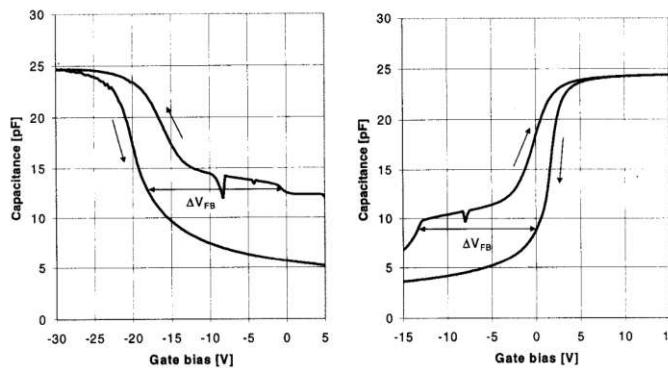

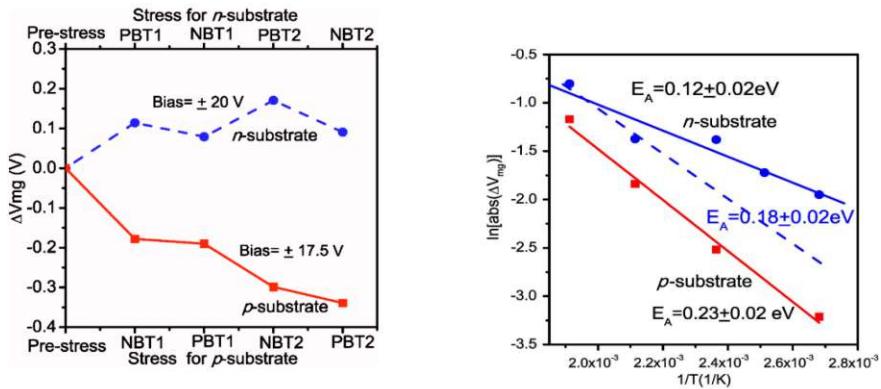

### 4.1.3. Hysteresis Phenomena in *n*-Type and *p*-Type MOSCAPs

E. Danielsson *et al.* [126] in 1998 employed MOS structures with TiN as a metal on n- and p- 4H-SiC in comparison with Al using  $C - V$  measurements. They observed that the hysteresis and interface states were comparable for the two gate types. Leakage on the n-type substrate was lower than that on the p-type substrate. The high flatband voltage  $V_{fb}$  of the p-type samples was due to the high density of the interface states. In the flatband region, these states were uncharged for the n-type samples and positively charged for the p-type samples, leading to a larger voltage shift in the p-type samples, as shown in Fig. 4.4. This result is not correlated with Fig. 4.8, where  $D_{it}$  is higher for the n-substrate, but may depend on the measurement conditions.