# UBIQUITOUS RELAXATION IN BTI STRESSING—NEW EVALUATION AND INSIGHTS

B. Kaczer, T. Grasser<sup>1</sup>, Ph. J. Roussel, J. Martin-Martinez<sup>2</sup>, R. O'Connor, B. J. O'Sullivan, G. Groeseneken<sup>3</sup> IMEC, Kapeldreef 75, B-3001 Leuven, Belgium

<sup>1</sup> CDL for TCAD, IμE, TU Wien, Austria; <sup>2</sup> visiting from UA Barcelona, Spain; <sup>3</sup> also ESAT Department, KU Leuven, Belgium phone: +32 (16) 281-557, fax: +32 (16) 281-706, e-mail: Ben.Kaczer@imec.be

#### ABSTRACT

The ubiquity of threshold voltage relaxation is demonstrated in samples with both conventional and high-k dielectrics following various stress conditions. A technique based on recording short traces of relaxation during each measurement phase of a standard measure-stress-measure sequence allows monitoring and correcting for the otherwise-unknown relaxation component. The properties of relaxation are discussed in detail for pFET with SiON dielectric subjected to NBTI stress. Based on similarities with dielectric relaxation, a physical picture and an equivalent circuit are proposed.

### Introduction

Bias-temperature instabilities (BTI) in CMOS technologies with advanced gate stacks are currently at the forefront of reliability concerns. Accurate evaluation of BTI degradation, necessary for correct lifetime extrapolation, is proving far from straightforward. On one hand, on-the-fly techniques are hampered by experimental difficulties with recording the initial (time = 0 s) state of the stressed device under test (DUT) and with deconvoluting FET parameter (mobility and threshold voltage  $V_{th}$ ) shifts [1]. On the other hand, standard measure-stress-measure (MSM) techniques used by most in industry, give hard-to-compare results due to ignored or unknown relaxation of the measured parameters, such as the FET threshold voltage shift  $\Delta V_{th}$ .

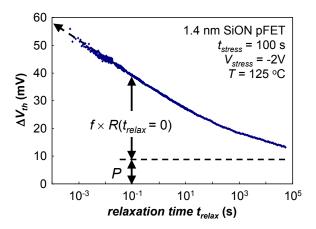

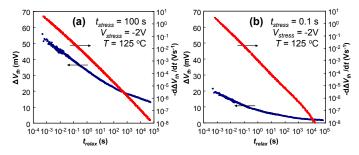

The  $\Delta V_{th}$  relaxation is typically observed to span many decades in time, from microseconds or possibly less [2,3] to days (Fig. 1) [4-6] indicating an underlying dispersive mechanism [7]. In an early attempt to circumvent the problem of  $V_{th}$  relaxation, we have designed a technique to speed up the evaluation of  $\Delta V_{th}$  [6,8]. This measurement technique, now considered for a JEDEC standard, is based on a rapid, single-point measurement of  $I_{D,lin}$  at  $\sim V_{th}$ . As is apparent from Fig. 1, however, achieving full correction of  $V_{th}$ relaxation with this technique is literally an uphill battle. This is because typical standard semiconductor analyzer equipment, capable of taking a current measurement in ~0.1 s, will only measure an unknown fraction of the recovery already in full progress. Extrapolation of thus-obtained data is then less than meaningful. Circumventing this problem is potentially possible with ultra-fast measurement setups [9], which at the moment, however, are still highly custom-specific and used by a few research groups only.

In this work we focus on MSM measurements with commonly-available off-the-shelf semiconductor analysis equipment. We show that far more insight into the BTI processes can be gained by abandoning the as-fast-as-possible approach and instead recording a short portion of recovery during every measurement phase. Then, by making an assumption about the behavior of BTI recovery [10,11], these short individual traces can be fitted together and the recoverable *R* and permanent *P* components of BTI degradation can

be separated, *independently* evaluated and extrapolated to operating conditions.

The subject of lifetime extrapolation *per se* is not elaborated on in this work [12,13]. Here we underline the importance of  $\Delta V_{th}$  relaxation (i.e., the R component) on lifetime projection and we discuss its properties. Using the described measurement technique we have found that the relaxation of  $\Delta V_{th}$  is prevalent in all studied systems so far (e.g., SiON pFET and nFET, NBTI and PBTI, AC NBTI, high-k pFET NBTI, substrate hot-carrier stress, etc.). Furthermore, based on more extensive evaluation of relaxation in ultrathin SiON pFETs, we show that  $\Delta V_{th}$  relaxation has some properties similar to dielectric relaxation [14,15]. We emphasize that these similarities are *purely phenomenological*, stemming solely from both mechanisms being dispersive in nature. However, we show that lessons learnt from the analogies could be useful both for circuit simulation of  $\Delta V_{th}$  relaxation and its microscopic modeling.

#### MEASUREMENT TECHNIQUE

Experimental considerations and technique description

Standard FETs with preferably short gate length L ( $\sim 0.13$  to 0.5  $\mu$ m) and wide gate width W ( $\sim 10~\mu$ m) to maximize FET current are used. The DUT is biased with small  $V_D$  (typically  $\pm 50~{\rm mV}$ ) and  $V_S$  =

Fig. 1: Relaxation of  $\Delta V_{th}$  in PFET with 1.4 nm SiON, measured as illustrated in Figs. 2b, c, and d. The logarithmic transient spans 8 decades and most likely starts already well below 1 ms. Conventional equipment capable of taking a reading in ~0.1 s measures the sum of an unknown fraction  ${\it F}$  of the recoverable component  ${\it R}$  on top of the permanent degradation component  ${\it P}$ . Any extrapolation using thus extracted  $\Delta V_{th}$  is questionable.

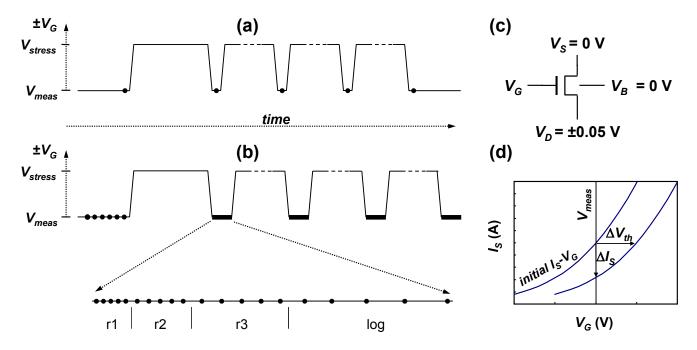

Fig. 2: (a) Previous "fast" and (b) the new BTI evaluation techniques. Unlike the "fast" technique (a), each "measure" phase is now designed to collect maximum information about relaxation in a short interval (b). "r1", "r2", "r3", and "log" represent different sampling rates to efficiently cover logarithmic time scale. (c) DUT bias during measurement and (d) an illustration of the post-stress FET current-to- $\Delta V_{th}$  conversion.

0V (Fig. 2c). This ensures that the stress voltage applied across the gate dielectric is approximately uniform. As in the case of the "fast" NBTI evaluation technique (Fig. 2a) [6], an initial I-V<sub>G</sub> characteristic (Fig. 2d) is first recorded to obtain a conversion "table" for all subsequent FET current (I<sub>S</sub> or I<sub>D</sub>) measurements. To minimize any unaccounted stressing of the DUT, care should be taken to measure this I-V<sub>G</sub> curve only up to  $\sim V$ <sub>meas</sub>. The value of V<sub>meas</sub> is typically chosen around V<sub>th</sub> of the unstressed DUT [1], where the FET current is sufficiently high ( $\sim$ 50— $100\times W$ /L nA) so that the measurement equipment can discern fractional changes in this current [16].

The DUT is then subjected to a preprogrammed MSM sequence of gate voltages  $V_G$ , comprising of alternating stress phases at  $V_{stress}$  and measure (or "relaxation") phases at  $V_{meas}$  (Figs. 2a and b). Small  $V_D$  remains applied and the FET current is recorded during the entire sequence. The additional data collected during the stress phases are equivalent to on-the-fly measurements for the respective phases and can provide further information about the DUT behavior [17]. We also found it beneficial to monitor the initial FET current for  $\sim 100$  s before  $V_{stress}$  is applied (see Fig. 2b) to ascertain the DUT is stable at  $V_{meas}$ . As is typical in most BTI experiments, the duration of stress phases is geometrically increased to cover several decades.

The new  $V_G$  waveform (Fig. 2b) differs in the design of the measure phase. In the previous "fast" BTI evaluation technique, each measure phase was performed as fast as possible ( $\sim$ 0.2 s on HP4156) and typically only one current point was recorded (see Fig. 2a). In the new measurement scheme (Fig. 2b), each measure phase is designed to collect maximum amount of information about relaxation in the short interval. A fixed time of  $\sim$  12 s is used in this work; a fixed fraction (e.g. 1/100) of the next stress phase duration is also possible [13, 16].

Direct-to-buffer functionality of grouped Keithley 2602 digital multi-meters (DMM's) is employed in our setup to capture data at short times. The data-sampling rate is sequentially reduced ("r1",

"r2", "r3" in Fig. 2b) by a script running directly on the DMM to cover the 12 s interval approx. uniformly on a logarithmic scale, resulting in efficient use of the DMM memory. Long-integration time DMM measurements with exponentially distributed delays ("log" in Fig. 2b) are added to the fast-buffer sequence for long relaxation measurements, typically the last measure phase of the MSM sequence.

The measurement sequence is concluded with a final I- $V_G$  characteristic to check the DUT. Finally, the FET current data recorded during the MSM sequence are converted to  $\Delta V_{th}$  using the initial I- $V_G$ , as illustrated in Fig. 2d [6].

The entire experiment (Keithley 2602 DMMs, Süss PA300 probe station, thermo chuck) is in our case controlled over GPIB from a PC using a framework of perl script subroutines. The use of high level programming language facilitates simple tasks, such as reformatting low-level GPIB data and processing results, but also allows e.g. preprogramming long experiments on many DUTs and even making decisions (e.g. "skipping" faulty devices) while running unattended.

## Measurement technique advantages

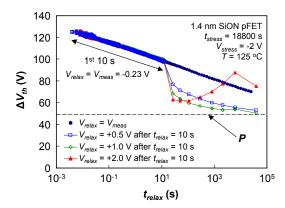

Once the FET has been exposed to BTI stress, its out-of-equilibrium parameters will relax over many time scales, from microseconds (or less) to days (or more). These distributed-time-scales parameter transients cannot be therefore "waited out" during reasonable time (see Fig. 1). Due to the same property of the relaxation component, also the "obvious" solution to accelerate relaxation before sensing is far from trivial. As it is shown in Fig. 3, relaxation can be accelerated by applying opposite (positive for pFET) voltage after stress is removed. Even after such acceleration, the relaxation takes  $10^3 - 10^4$  s to approach within 10% of the final P value [13]. Choosing the acceleration voltage is also problematic—applying too high opposite voltage results in BTI stress and defect creation of its own (see the  $V_{relax} = +2$  V curve in Fig. 3).

Fig. 3: Due to the dispersive nature of the relaxation component, application of opposite voltage ( $\pm 0.5$  and  $\pm 1$  V on a pFET) does not result in immediate recovery. Further increase in recovery-accelating voltage ( $\pm 2$  V) leads to BTI stressing of the device.

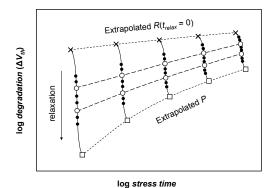

Fig. 4: Schematic illustration of the effect of relaxation on BTI MSM measurements. Due to immediate relaxation of  $\Delta V_{th}$  degradation at the end of each stress phase (cf. Fig. 1), a single-point "fast" (Fig. 2a), or slower I- $V_G$  measurements (open circles) of the degradation will give approximately power-law dependence on stress time. When the relaxation trend at each stress time (solid circles) is recorded, the

RECOVERABLE COMPONENT CAN BE EXTRAPOLATED TO  $t_{relax} = 0$  or  $t_{relax} = \infty$  ( i.e., P ).

The dispersive property of the parameter relaxation is the crux of the problem of MSM BTI characterization. The main advantage of the new MSM measurement scheme is its ability to record not only the  $\Delta V_{th}$  shift, but also the *relaxation trends at each point of stress*, which constitute *additional information* about the system in a "constant state of motion" [18]. Provided the transient behavior is understood, the "full" recoverable component at  $t_{relax}=0$  can be extrapolated and separated from the permanent damage. The comparison of the technique with previous MSM techniques recording a single point per sensing phase is schematically depicted in Fig. 4.

Measurement technique caveats and drawbacks

Before we discuss experimental results obtained using the described technique, namely the properties of the relaxing component, we briefly summarize possible experimental caveats and drawbacks of the technique.

Firstly, it is essential that the technique is only applied to devices showing stable FET current when  $V_{meas}$  is applied before the application of stress. This is checked by monitoring each DUT at  $V_{meas}$  for 100 s (see Fig. 2b).

The pivotal assumption of the measurement technique is that at  $V_{meas}$ , all changes in the recorded FET current are due to  $\Delta V_{th}$  only. Choosing  $V_{meas} \sim V_{th}$  minimizes influences of both subthreshold slope and mobility changes [1]. Other factors potentially influencing the FET current during measurement include changes in gate oxide leakage (SILC and soft breakdown) and in drain junction leakage (since  $V_D \neq 0$ V). The latter issue, occurring e.g. in FETs with small-band gap Ge substrates [19] can be reduced by monitoring the source current, since  $V_S = V_B = 0$ V. Presence of all other current perturbations should be checked by comparing the shapes and magnitudes of all currents of the initial and final I- $V_G$  characteristics.

Finally, it is crucial to check the *actual* waveform (Fig. 2b) applied on the gate of the DUT with an oscilloscope. For example, some measurement setups can momentarily dwell at 0V *during each voltage transition*. The degradation at measure voltage then appears smaller due to the inadvertently accelerated relaxation, as illustrated in Fig. 3.

# RESULTS AND DISCUSSION

#### Examples of relaxation ubiquity

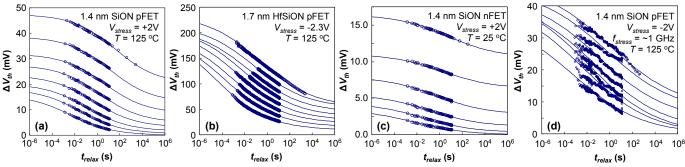

Fig. 5 shows examples of data collected on both SiON and high-k samples under various stress conditions. In all cases, relaxation of  $\Delta V_{th}$  is apparent, underlying the need to record and evaluate the recovery in detail. Also note that on all samples the (final topmost) relaxation is observed to stretch over 6 decades in time, with no apparent sign of saturation at either the short or long relaxation times. In contrast to that, the 1-exp(-t/ $\tau$ ) discharge of traps with a single  $\tau$  occurs over ~1.4 decades in time (assuming transition from 10% to 90%), while the Reaction-Diffusion (RD) model [20] relaxation is expected to occur over ~3.8 decades in time (10%—90%) [10]. From this we conclude that in all cases in Fig. 5 the relaxation is most likely controlled by a dispersive mechanism with widely distributed time scales [7, 11].

We have noticed that while the relaxation is always present, its relative magnitude compared to the overall degradation can vary among samples and stress conditions. While the relaxation is dominant after both NBTI and PBTI in pFETs with both SiON and high-k gate oxides, in some cases, such as hot channel electron injection (HCI) in SiON nFET's, it could be less pronounced (not shown). In such a system [21], relaxation can likely be ignored in the first approximation.

#### Properties of the recoverable component

The ubiquitous recoverable component is studied in more detail on pFET's with 1.4 nm EOT SiON dielectrics subjected to NBT stress (unless otherwise noted). In particular we discuss its following properties: universality and relaxation time, stress time, voltage, temperature, and AC stress duty cycle dependences.

Relaxation time dependence—universality of relaxation

Previously we have noticed [6,13] that the long, log-like BTI relaxation transients can be well described by

FIG. 5: EXAMPLES OF UBIQUITY OF  $\Delta V_{th}$  RELAXATION: (A) SION PFET AFTER PBTI STRESS, (B) PFET WITH METAL GATE/HIGH-K STACK AFTER NBTI STRESS (NOTE STRONG RECOVERY DURING EACH MEASUREMENT), (C) SION NFET AFTER SUBSTRATE HOT CARRIER STRESS AT ROOM  $T(V_B = -1.5 \text{ V}, I_{INJ} = 5 \text{ mA}; \text{NOTE ENHANCED "OFFSET"}$  DUE TO PERMANENT COMPONENT GENERATION), (D) SHORT  $L = 0.13 \text{ } \mu \text{m}$  SION PFET AFTER ~1 GHZ AC NBTI STRESS (NOTE DISTINCT STEPS LIKELY CORRESPONDING TO RECOVERY OF INDIVIDUAL STATES). EXPERIMENTAL DATA (SYMBOLS) ARE FITTED WITH EQS. 1-3 (LINES).

$$r(\xi) = \frac{1}{1 + B\xi^{\beta}},\tag{1}$$

where  $\xi = t_{relax}/t_{stress}$  is the *universal* (dimensionless) relaxation time. Here,  $t_{stress}$  is the *total* (*cumulative*) stress time, while  $t_{relax}$  is measured from the end of the last stress phase; B is a scaling parameter. The functional form of Eq. 1 has properties similar to a stretched exponential, which is often invoked to describe relaxation of dispersive systems, and  $\beta$  has the attributes of a dispersion parameter [7].

The *universality* of BTI relaxation, i.e. its property of scaling with the universal relaxation time  $\xi$ , is the intrinsic property of the RD model. Universality of BTI relaxation was also observed and discussed in Ref. [22].

The assumption of universality of BTI relaxation allows us to fit all short relaxation transient "snapshots" measured during each measure phase with a single set of parameters B and  $\beta$  for each MSM sequence [13]. The fitting procedure further assumes

$$\Delta V_{th}(t_{stress}, t_{relax}) = R(t_{stress}, t_{relax}) + P(t_{stress}), \qquad (2)$$

and

$$R(t_{stress}, t_{relax}) = R(t_{stress}, t_{relax} = 0) r(\xi).$$

(3)

In Eq. 3,  $R(t_{stress}, t_{relax} = 0)$  represents the "full" recoverable component extrapolated to  $t_{relax} = 0$ .

The fits for a diverse combination of samples and stressing conditions are shown in Fig. 5. In all the cases, Eq. 3 fits the relaxation data well.  $\beta$  is typically between 0.14 and 0.20 for all pFET samples (both SiON and Hf-based high-k dielectrics) subjected to NBTI stress.

While we observe the universality of relaxation in most production-quality gate stacks (with either SiON or Hf-based dielectrics on Si substrates), we have noticed that relaxation does not fully follow Eq. 3 in some very experimental gate stacks, such as those based on Ge substrates [19], dielectrics containing Dy and La, etc. [23,24]. In those systems, an *additional* mechanism, such a strong trap level in the dielectric, is suspected to be active during relaxation. Recording the relaxation transients in such cases is still beneficial, as it exposes processes in the sample that would be otherwise overlooked during standard BTI analysis [24].

#### Stress time dependence

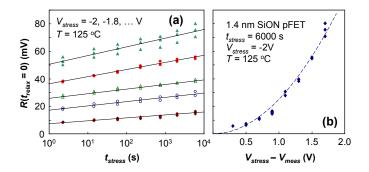

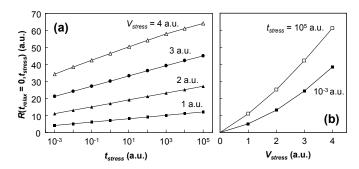

The above-described fitting procedure is now applied to extract the recoverable component for every measure phase of the NBTI MSM sequence. The semi-log plot in Fig. 6a shows  $R(t_{stress}, t_{relax} = 0)$  as function of the cumulative stress time  $t_{stress}$ .  $R(t_{stress}, 0)$  appears to scale as log of  $t_{stress}$  [2,22].

We note that because of the relatively small increase of  $R(t_{stress}, 0)$  in the measured range of  $t_{stress}$ , the same data will also appear to follow a power law in a log-log plot, however, with a very small exponent of 0.04—0.06. This is consistent with  $\Delta V_{th}$  data extracted in some ultra-fast measurements [9], which observe exponents < ~0.1. Ultra-fast measurements are able to capture a much larger part of the relaxing component (see Figs. 1 and 4) and consequently, the measured  $\Delta V_{th}$  dependence will be dominated by this component.

FIG. 6: DEPENDENCE OF THE RECOVERABLE COMPONENT R ON (A) STRESS TIME AND (B) STRESS VOLTAGE. R APPEARS TO INCREASE LOGARITHMICALLY WITH STRESS TIME (A) AND SUPERLINEARLY ON  $V_{stress} - V_{meas}$  (B). DASHED LINE: FIT ASSUMING ( $V_{stress} - V_{meas}$ )<sup>2</sup>.

#### Voltage dependence

Voltage dependence of the recoverable component is studied by plotting  $R(t_{stress} = 6000 \text{ s}, 0)$  from Fig. 6a versus the  $V_{stress} - V_{meas}$ , i.e. the voltage increase applied during stressing. Since  $V_{meas}$  was chosen  $\sim V_{th}$  of the fresh device (see above),  $V_{stress} - V_{meas}$  is approximately proportional to the electric field in the oxide during stress. Scaling of the BTI mechanism with the oxide electric field has been generally accepted [25]. In Fig. 6b it is observed that the dependence of  $R(t_{stress}, 0)$  on this quantity is superlinear, close to the second power [26].

#### Temperature dependence

100

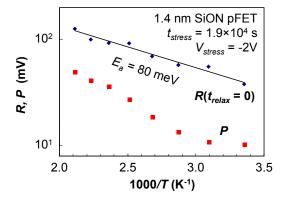

$R(t_{stress}, 0)$  is weakly temperature dependent, with activation energy  $\sim 80$  meV, as shown in Fig. 7. Interestingly, the "dispersion parameter"  $\beta$  (extracted at different temperatures, not shown) is seen to be *independent of temperature*, which contrasts with the predictions of dispersive hydrogen transport models [6,10].

Fig. 7: Temperature dependence of the R and P components. The recoverable component R changes by a factor of  $\sim$  3 in the measured T range of 25 - 200  $^{\rm o}$ C. P appears to be non-arrhenius [13]

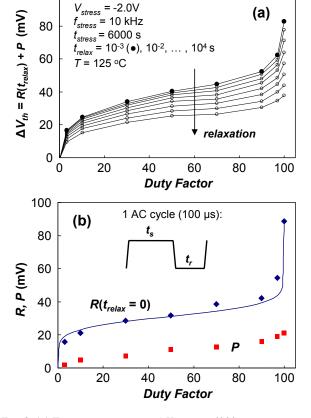

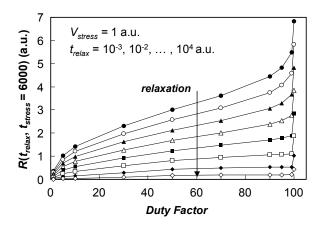

FIG. 8: (A) TOTAL DEGRADATION  $\Delta V_{th}$  AFTER 6000 s of UNIPOLAR NBTI STRESS SHOWS A DISTINCTIVE DEPENDENCE ON THE DUTY FACTOR DF. Data at different relaxation times are shown. (B) Recoverable R and permanent P components extracted from data in (a). Plateau-like shape of DF dependence is due to R and can be qualitatively explained by Eq. 1 with  $\xi = 1/DF$ -1 (Eq. 6) acting on the time scale of a single AC stress pulse.

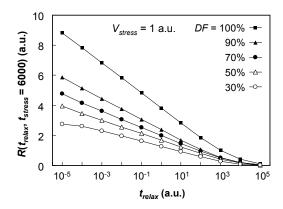

#### AC stress duty cycle dependence

Although the properties of degradation after constant (static or DC) BTI stress are important, they are of limited use for digital CMOS applications with continuously switching FET devices. It has been generally observed that dynamic (i.e., AC) unipolar NBTI stress with 50% duty cycle results in about ½ degradation of the equivalent static stress [20]. The dependence on the duty cycle (called duty *factor* or DF here), however, has been seldom studied. In Ref. [27] we have reported for the first time a  $\Delta V_{th}$ -DF dependence with an inflection point around DF  $\sim$  50%. Qualitatively identical dependence, re-measured with the new MSM technique is shown in Fig. 8a. We argue that this distinctive shape in Fig. 8a is a fundamental feature of BTI relaxation *and should serve as a touchstone for all proposed NBTI models*.

Fig. 8b shows the full recoverable R and the permanent P components extracted from data in Fig. 8a. As can be seen, the particular shape of the DF dependence is chiefly due to the recoverable component R.

We also note a peculiar property of Eq. 1—when applied on the microsecond scale, it qualitatively explains the *R-DF* dependence in Fig. 8b [28]. Assuming (see inset of Fig. 8b)

$$DF = \frac{t_s}{t_s + t_r} = \frac{1}{1 + t_r / t_s},$$

(4)

where  $t_s$  and  $t_r$  are now the stress and relaxation times within each cycle, we obtain

$$DF = \frac{1}{1+\xi} \tag{5}$$

and hence,

$$\xi = \frac{1}{DE} - 1. \tag{6}$$

Fig. 8b shows the excellent fit of  $const \times r(1/DF-1)$  to the extracted  $R(t_{stress}=6000 \text{ s}, 0)$  component.

#### Curie-von Schweidler-like behavior of BTI relaxation

The ubiquitous recoverable component is studied in more detail by recording  $\Delta V_{th}$  recovery for 8 decades of time. As can be seen in Figs. 9a and b, both the continuous and the pulse-like stress result in a logarithmically decreasing  $\Delta V_{th}$  over the full time range.

Fig. 9:  $\Delta V_{th}$  relaxation after (a) continuous and (b) pulse-like NBTI stress. The first derivatives, corresponding to gate relaxation current, follow  $1/t_{relax}^a$  over 8 decades [a=1.08 and 1.14 in (a) and (b) respectively]. The derivatives were calculated using weighted integral fitting of B-spline sequences through the relaxation data.

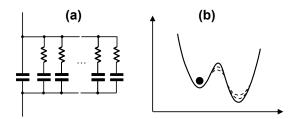

Fig. 10: The behavior of the  $1^{ST}$  derivatives of relaxation transients in Fig. 5, also known as the Curie-von Schweidler Law, suggests applying similar (a) circuit and (b) microscopic models to BTI relaxation.

We now note that a displacement current through a capacitor formed by the FET gate stack is proportional to  $-dV_{th}/dt$ . The calculated 1st derivatives of  $\Delta V_{th}(t)$ , corresponding to a relaxation current, follow almost perfectly  $1/t^a$  dependence with  $a\approx 1$  over the entire wide measurement range. This is not entirely surprising, considering that  $r(\xi) \sim \log(\xi)$  for  $\xi \sim 1$  [6] and  $\mathrm{dlog}(t)/\mathrm{d}t = 1/t$ . Capacitor current decaying as  $1/t^a$  is associated with several mechanisms [29], notably oxide trap discharging and dielectric relaxation (the so-called Curie-von Schweidler law) [14,15]. The latter is typically depicted as a capacitor with parallel exponentially-distributed RC elements for circuit modeling applications (Fig. 10a) [14] or a double-well system with distributed barriers and well depths (Fig. 10b) [15].

#### Implications for physical modeling

Charge trapping and interface state creation (due to hydrogen depassivation) are the mechanisms most frequently invoked to explain BTI. Relaxation of the BTI degradation, i.e., the recoverable component R, is then typically ascribed to interface state hydrogen repassivation [20] or to neutralization of trapped charge [30], while the permanent damage has been related to unpassivated interface states [30] and to deep hole traps [31,32]. This discussion implies it is theoretically possible that i) two independent mechanisms are respectively responsible for the R and P components, but also that ii) a single mechanism is responsible for both degradation components. The microscopic picture suggested in Fig. 10b provides a new impulse for physical modeling of BTI phenomena in general, but also for investigating the possibility of a single common cause for both degradation components [17].

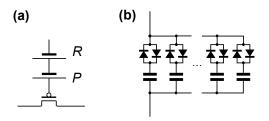

FIG. 11: (A) FOR CIRCUIT MODELING OF A FET UNDER STRESS,  $\Delta V_{th}$  is simulated by voltage sources representing the permanent component P, increasing with cumulative stress, and the recoverable component R, calculated using circuit in (B). (B) Non-Linear conductances (simulated by 2 diodes per element) combined with geometrically distributed capacitances correctly reproduce several properties of the recoverable component discussed in this work.

#### Implications for electrical modeling

In order to study the reliability of CMOS circuits, an equivalent circuit for a FET emulating the effect of an *arbitrary* BTI sequence is needed. In its simplest form, the permanent and recoverable parts of the threshold voltage shift can be introduced as shown in Fig. 11a. We find that most properties of the *recoverable* component discussed above can be reproduced when ohmic resistors in each RC element in Fig. 10a are replaced with a *non-linear* component (simulated by 2 diodes with different parameters, see Fig. 11b). While this non-linear component is fixed for all elements, the capacitor values are varied by a factor of 10 from element to element. 20 elements are used in the calculation, carried out in the C language for speed, but cross-checked in the ADS circuit simulator. The threshold voltage shift at any moment is assumed to be proportional to the simple average of voltages on all capacitors, i.e., no weighting of elements is assumed for simplicity.

The equivalent circuit qualitatively correctly reproduces the logarithmic relaxation after BTI stress (Fig. 12; cf. Fig. 1), logarithmic increase during stress (Fig. 13a; cf. Fig. 6a), and even the superlinear voltage dependence (Fig. 13b; cf. Fig. 6b).

Fig. 12: Calculation with the equvalent circuit in Fig. 8b shows the long, log-like transients of the recoverable component correctly reproduced for both DC (DF = 100%) and AC (DF < 100%) BTI stress (cf. Fig. 1).

FIG. 13: CALCULATION OF THE RECOVERABLE COMPONENT AS PER FIG. 8B CORRECTLY REPRODUCES (A) THE LOG-LIKE INCREASE WITH STRESS TIME (CF. FIG. 6A) AND (B) THE SUPERLINEAR DEPENDENCE ON STRESS VOLTAGE (CF. FIG. 6B).

Fig. 14: The plateau in DF dependence of R is also qualitatively well reproduced, as is the decrease with increasing relaxation time (cf. Fig. 8a, which, however, shows the sum of  $R(t_{stress}, t_{relax})$  and P).

The equivalent circuit in Fig. 11b also reproduces the recoverable component being *independent* of frequency (not shown) [27]. The circuit in the simple form cannot be used to study temperature effects, as the temperature dependence of the diode current results in a trend opposite to the observation in Fig. 7.

Most importantly, however, the equivalent circuit correctly reproduces the distinctive dependence on the duty factor (Fig. 14; cf. Fig. 8) for AC BTI stress. Note also that the value at DF = 50% is about half of the degradation at DC (DF = 100%) for all relaxation times. This could explain why approximately  $\frac{1}{2}$  the degradation in AC stress wrt DC stress is commonly observed by most researchers, independently of the measure (i.e., relaxation) time.

#### **CONCLUSIONS**

$\Delta V_{th}$  relaxation is shown to be prevalent in FETs with both conventional and high-k dielectrics and subjected to various stress conditions. A MSM technique based on recording short traces of  $\Delta V_{th}$  relaxation is introduced, exposing processes in the DUT that would be otherwise overlooked during standard MSM BTI analysis. In samples showing universality of relaxation, this property is used to correct for the otherwise-unknown  $\Delta V_{th}$  relaxation component. Properties of  $\Delta V_{th}$  relaxation following NBTI stress of pFETs with SiON gate dielectric are discussed in detail. Based on similarities with dielectric relaxation, an equivalent circuit and a physical picture are proposed for  $\Delta V_{th}$  relaxation.

#### **ACKNOWLEDGEMENTS**

This work has been partially supported by the Spanish MCyT (TEC2004-00798/MIC).

#### REFERENCES

- [1] T. Grasser, P.-J. Wagner, Ph. Hehenberger, W. Gös, and B. Kaczer, "A Rigorous Study of Measurement Techniques for Negative Bias Temperature Instability," in *IIRW Final Report*, 2007, p. 6.

- [2] H. Reisinger, O. Blank, W. Heinrigs, A. Mühlhoff, W. Gustin, and C. Schlünder, "Analysis of NBTI Degradation- and Recovery-Behavior Based on Ultra Fast V<sub>T</sub>-Measurements," in *Proc. Int. Reliab. Phys. Symp.*, 2006, p. 448.

- [3] T. Yang, C. Shen, M. F. Li, C. H. Ang, C. X. Zhu, Y.-C. Yeo, G. Samudra, S. C. Rustagi, M. B. Yu, and D.-L. Kwong, "Fast DNBTI Components in p-MOSFET With SiON Dielectric," in *IEEE Electron Dev. Lett.* 26, 2005, p. 826.

- [4] G. Chen, K. Y. Chuah, M. F. Li, D. S. H. Chan, C. H. Ang, J. Z. Zheng, Y. Jin, and D. L. Kwong, "Dynamic NBTI of PMOS Transistors and Its Impact on Device Lifetime," in *Proc. Int. Reliab. Phys. Symp.*, 2003, p. 196.

- [5] S. Rangan, N. Mielke, and E. C.C. Yeh, "Universal Recovery Behavior of Negative Bias Temperature Instability," in *IEDM Tech. Digest*, 2003, p. 341.

- [6] B. Kaczer, V. Arkhipov, R. Degraeve, N. Collaert, G. Groeseneken, and M. Goodwin, "Disorder-controlled-kinetics Model for Negative Bias Temperature Instability and Its Experimental Verification," in *Proc. Int. Reliab. Phys. Symp.*, 2005, p. 381.

- [7] B. Kaczer, V. Arkhipov, R. Degraeve, N. Collaert, G. Groeseneken, and M. Goodwin, "Temperature Dependence of the Negative Bias Temperature Instability in the Framework of Dispersive Transport," in *Appl. Phys. Lett.* 86, 2005, p. 143506.

- [8] B. Kaczer, R. Degraeve, V. Arkhipov, N. Collaert, G. Groeseneken, M. Goodwin, "The influence of recovery and temperature on the NBTI power-law exponent," as discussed at the 35th IEEE SISC, San Diego, 2004.

- [9] C. Shen, M.-F. Li, C. E. Foo, T. Yang, D. M. Huang, A. Yap, G. S. Samudra, and Y.-C. Yeo, "Characterization and Physical Origin of Fast V<sub>th</sub> Transient in NBTI of pMOSFETs with SiON Dielectric," in *IEDM Tech. Digest*, 2006, p. 333.

- [10] T. Grasser, W. Gös, V. Sverdlov, and B. Kaczer, "The Universality of NBTI Relaxation and its Implications for Modeling and Characterization," in *Proc. Int. Reliab. Phys.* Symp., 2007, p. 268.

- [11] B. Kaczer, T. Grasser, R. Fernandez, and G. Groeseneken, "Toward Understanding the Wide Distribution of Time Scales in Negative Bias Temperature Instability," in "9<sup>th</sup> Symp. On Silicon Nitride, Silicon Dioxide, and Emerging Dielectrics," editors Sah, Deen, Zhang, Yota, and Kamakura, published by The Electrochemical Society, 2007, p. 265.

- [12] T. Grasser and B. Kaczer, "Negative Bias Temperature Instability: Recoverable versus Permanent Degradation", in *Proc. ESSDERC*, 2007, p. 127.

- [13] T. Grasser, B. Kaczer, P. Hehenberger, W. Gös, R. O'Connor, H. Reisinger, W. Gustin, and C. Schlünder, "Simultaneous Extraction of Recoverable and Permanent Components Contributing to Bias-Temperature Instability," in *IEDM Tech. Digest*, 2007, p. 801.

- [14] H. Reisinger, G. Steinlesberger, S. Jakschik, M. Gutsche, T. Hecht, M. Leonhard, U. Schröder, H. Seidl, and D. Schumann, "A comparative study of dielectric relaxation losses in alternative dielectrics," in *IEDM Tech. Digest*, 2001, p. 267.

- [15] J. R. Jameson, W. Harrison, P. B. Griffin, J. D. Plummer, and Y. Nishi, "A Semiclassical Model of Dielectric Relaxation in Glasses," in *J. Appl. Phys.* 100, 2006, p. 124101.

- [16] H. Reisinger, U. Brunner, W. Heinrigs, W. Gustin, and C. Schlünder, "A Comparison of Fast Methods for Measuring NBTI Degradation," in *IEEE Trans. Dev. Mat. Rel.* 7, 2007, p. 531

- [17] T. Grasser, B. Kaczer, and W. Gös, "An Energy-Level Perspective of Bias Temperature Instability", in *Proc. Int. Reliab. Phys. Symp*, 2008.

- [18] C. R. Parthasarathy, M. Denais, V. Huard, G. Ribes, E. Vincent, and A. Bravaix, "New Insights into Recovery Characteristics Post NBTI Stress," in *Proc. Int. Reliab. Phys. Symp*, 2006, p. 471.

- [19] M. Aoulaiche, B. Kaczer, B. De Jaeger, M. Houssa, K. Martens, R. Degraeve, P. Roussel, J. Mitard, S. De Gendt, H.E. Maes, G. Groeseneken, M. Meuris, and M.M. Heyns, "Negative Bias Temperature Instability on Si-passivated Geinterface," in *Proc. Int. Reliab. Phys. Symp*, 2008.

- [20] M. A. Alam, "A Critical Examination of the Mechanics of Dynamic NBTI for PMOSFETs," in *IEDM Tech. Digest*, 2003, p. 345.

- [21] C. Guérin, V. Huard, and A. Bravaix, "The Energy-Driven Hot-Carrier Degradation Modes of nMOSFETs," in *IEEE Trans. Dev. Mat. Rel.* 7, 2007, p. 225.

- [22] M. Denais, A. Bravaix, V. Huard, C. Parthasarathy, C. Guerin, G. Ribes, F. Perrier, M. Mairy, and D. Roy, "Paradigm Shift for NBTI Characterization in Ultra-Scaled CMOS Technologies," in *Proc. Int. Reliab. Phys. Symp*, 2006, p. 735.

- [23] A. Veloso, L. Witters, M. Demand, I. Ferain, N. J. Son, B. Kaczer, Ph. J. Roussel, E. Simoen, T. Kauerauf, C. Adelmann, S. Brus, O. Richard, H. Bender, T. Conard, R. Vos, R. Rooyackers, S. Van Elshocht, N. Collaert, K. De Meyer, S. Biesemans, and M. Jurczak, "Flexible and Robust Capping-Metal Gate Integration Technology enabling multiple-VT CMOS in MuGFETs," to be presented at VLSI Symp., 2008.

- [24] S. Z. Chang, T. Y. Hoffmann, H. Y. Yu, M. Aoulaiche, E. Rohr, C. Adelmann, B. Kaczer, A. Delabie, P. Favia, S. Van Elshocht, S.Kubicek, T. Scharm, T. Witters, L.-A. Ragnarsson, X. P. Wang, H. -J. Cho, M. Mueller, T. Chiarella, P. Absil, and S. Biesemans, "Low V<sub>T</sub> Metal-gate/High-k nMOSFETs PBTI dependence and V<sub>T</sub> Tuneability on La/Dy-capping layer locations and Laser annealing conditions," to be presented at VLSI Symp., 2008.

- [25] A. E. Islam, H. Kufluoglu, D. Varghese, S. Mahapatra, and M. A. Alam, "Recent Issues in Negative-Bias Temperature Instability: Initial Degradation, Field Dependence of Interface Trap Generation, Hole Trapping Effects, and Relaxation," in *IEEE T. Electron Dev.* 54, 2007, p. 2143.

- [26] J. P. Campbell, K. P. Cheung, J. S. Suehle, A. Oates, "The Fast Initial Threshold Voltage Shift: NBTI or High-Field Stress," in *Proc. Int. Reliab. Phys. Symp*, 2008.

- [27] R. Fernández, B. Kaczer, A. Nackaerts, S. Demuynck, R. Rodríguez, M. Nafría, and G. Groeseneken, "AC NBTI Studied in the 1 Hz 2 GHz Range on Dedicated On-Chip CMOS Circuits," in *IEDM Tech. Digest*, 2006, p. 337.

- [28] A. Haggag, G. Anderson, S. Parihar, D. Burnett, G. Abeln, J. Higman, and M. Moosa, "Understanding SRAM High-Temperature-Operating-Life NBTI: Statistics and Permanent vs Recoverable Damage," in *Proc. Int. Reliab. Phys. Symp.*, 2007, p. 452.

- [29] M. Schumacher, Ph.D. Thesis, RWTH Forschungszentrum Jülich, Germany, 1998.

- [30] V. Huard, M. Denais, and C. Parthasarathy, "NBTI Degradation: From Physical Mechanisms to Modelling," in Microelectr. Reliab. 46, 2006, p. 1.

- [31] D. S. Ang and S. Wang, "Insight Into the Suppressed Recovery of NBTI-Stressed Ultrathin Oxynitride Gate pMOSFET," in *IEEE Electron Dev. Lett.* 27, 2006, p. 755.

- [32] J. F. Zhang, M. H. Chang, and G. Groeseneken, "Effects of Measurement Temperature on NBTI," in *IEEE Electron Dev. Lett.* 28, 2007, p. 298.