# Hot-Electron-Related Degradation in InAlN/GaN High-Electron-Mobility Transistors

Milan Ťapajna, Nicole Killat, Vassil Palankovski, Dagmar Gregušová, Karol Čičo, Jean-Francois Carlin, Nicolas Grandjean, Martin Kuball, and Ján Kuzmík

Abstract—Hot-electron temperature  $(T_e)$  in InAlN/GaN highelectron-mobility transistors (HEMTs) was determined using electroluminescence spectroscopy as a function of gate voltage and correlated with the  $T_e$  distribution determined by hydrodynamic simulations. Good agreement between measurement and simulations suggests that hot electrons can locally reach temperatures of up to 30000 K at  $V_{ds} = 30$  V, i.e., two to three times higher than that typically obtained for similar AlGaN/GaN HEMTs. The consequence of such high  $T_e$  in InAlN/GaN HEMTs is illustrated by electrical stressing in OFF and semi-ON state at  $V_{\rm gd} = 100$  V. Prominent channel degradation was observed for devices stressed in semi-ON state, suggesting hot-electron driven degradation. Threshold voltage and drain current transient analyses indicate that hot electrons increase the density of traps in the GaN channel underneath the gate as well as surface/interface traps located in the gate-to-drain access region.

Index Terms—Electrical stress, electroluminescence (EL), hot electrons, hydrodynamic (HD) simulation, InAlN/GaN high-electron-mobility transistor (HEMT), reliability.

# I. INTRODUCTION

IGH-electron-mobility transistors (HEMTs) based on InAlN/GaN heterostructures [1] represent an extremely promising technology for RF power devices for telecommunication and satellite applications [2]–[5]. InAlN/GaN HEMTs with record current gain cutoff frequency of 400 GHz

Manuscript received December 6, 2013; revised June 16, 2014; accepted June 17, 2014. Date of current version July 21, 2014. This work was supported in part by the Research and Development Operational Program, European Regional Development Fund, through the Project Competence Center for New Materials, Advanced Technologies, and Energy under Grant ITMS 26240220073 (1/2), in part by the European Commission through the MORGAN Project under Contract FP7 NMP IP 214610, and in part by the Slovak Research and Development Agency under Contract APVV-0104010. The review of this paper was arranged by Editor B. Kaczer.

M. Ťapajna, D. Gregušová, K. Čičo, and J. Kuzmík are with the Institute of Electrical Engineering, Slovak Academy of Sciences, Bratislava 841 04, Slovakia (e-mail: milan.tapajna@savba.sk; dagmar.gregusova@savba.sk; karol.cico@savba.sk; jan.kuzmik@savba.sk).

N. Killat and M. Kuball are with the Center for Thremography and Reliability, H. H. Wills Physics Laboratory, University of Bristol, Bristol BS8 1TL, U.K. (e-mail: nicole.killat@bristol.ac.uk; martin.kuball@bristol.ac.uk).

V. Palankovski is with the Institute of Electrical Engineering, Slovak Academy of Sciences, Bratislava 841 04, Slovakia, and also with the Institute for Microelectronics, Vienna University of Technology, Vienna 1040, Austria (e-mail: palankovski@iue.tuwien.ac.at).

J.-F. Carlin and N. Grandjean are with the Institute of Quantum Electronics and Photonics, EPFL, Lausanne CH-1015, Switzerland (e-mail: jean-francois.carlin@epfl.ch; nicolas.grandjean@epfl.ch).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2014.2332235

have been demonstrated [6]. In addition, several promising concepts for normally off switching transistors for power converter applications have been proposed in [7] and [8]. The main advantage of InAlN/GaN HEMTs over those utilizing AlGaN/GaN heterostructure is in almost a three-time higher electron concentration in the channel. This is due to the higher spontaneous polarization at the heterointerface, even in the absence of the piezoelectric polarization component in these devices, in contrast to the piezoelectric polarization inherently present at AlGaN/GaN interface as a result of tensile strain in the AlGaN barrier layer. Although not fully clear up to date, the stress in the AlGaN layer is likely to enhance degradation of the AlGaN/GaN HEMTs, such as surface cracking [9], [10] and more often surface pitting, i.e., amorphous material inclusions into crystalline lattice [11]-[14] at the drain side of the gate edge upon high electrical field. As InAlN can be lattice matched on GaN, enhanced robustness against electromechanical-related degradation modes can be expected. No such degradation mode of InAlN/GaN devices has been reported so far. However, there are only few studies devoted to the analysis of degradation mechanisms in InAlN/GaN HEMTs [15]-[18]. In general, a pronounced degradation of channel resistance upon high-field electrical stressing has been reported and attributed to hot electron [15], [16] or hot-phonon effect [17]. Interestingly, Kuzmik et al. [16] predicted electron temperature  $(T_e)$  as high as 20000 K in the transistor's channel; however, any experimental evidence for such high  $T_e$  is still missing.

In this paper,  $T_e$  in InAlN/GaN HEMTs' channel was experimentally measured using electroluminescence (EL) spectroscopy and analyzed in conjunction with hydrodynamic (HD) simulations. Our analysis indicates that hot electrons can locally reach  $T_e$  of 30 000 K. Therefore, InAlN/GaN HEMTs were stressed in OFF and semi-ON state at  $V_{\rm gd}=100$  V and analyzed by means of electrical characterization. More pronounced degradation of HEMTs submitted to semi-ON state stress compared with OFF state suggests hotelectron driven degradation, which is discussed in relation to dehydrogenation of point defects in the GaN channel.

### II. EXPERIMENTAL AND SIMULATION DETAILS

$In_{0.17}Al_{0.83}N/AlN/GaN$  (13 nm/1 nm/1.2  $\mu$ m) heterostructure with lattice-matched InAlN layer was grown by metalorganic chemical vapor deposition (MOCVD) on sapphire

substrates. Hall measurements yielded an electron mobility of  $\sim$ 560 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and a 2-D electron gas (2-DEG) density of  $\sim 2.2 \times 10^{13}$  cm<sup>-2</sup>. Lower 2-DEG mobility resulted from the application of the AlN seeding layer inserted between the sapphire substrate and GaN buffer. From our experience, the seeding layer ensured lower buffer leakage and higher breakdown voltage compared with InAlN/GaN heterostructures directly grown on the sapphire substrate, on the expense of lower mobility. After mesa etching and Ti/Al/Ni/Au ohmic contact formation, optical lithography was used to define 1.8  $\mu$ m-long and 25  $\mu$ m-wide rectangular-shaped Ni/Au Schottky gate contacts without field plate. Finally, the wafers were passivated by 10-nm-thick Al<sub>2</sub>O<sub>3</sub> layer grown by MOCVD at 600 °C without any postdeposition treatment. Finalized devices showed threshold voltage  $(V_{th})$  and maximum drain current ( $I_{d,max}$ ) of -4.7 V and 0.7 A/mm, respectively.

EL spectroscopy was used to determine  $T_e$  from a highenergy tail of the EL spectrum as a function of  $V_{gs}$  at  $V_{\rm ds} = 30 \text{ V}$  [19]–[21] using a Renishaw inVia spectrometer with a  $50 \times (NA = 0.5)$  objective from the top side of the wafer. All spectra were corrected with the system response function and only devices with negligible yellow luminescence contribution were considered [22], which, if present, could affect a fitting result. To analyze the measured  $T_e$  in more detail, the spatial distribution of  $T_e$  was also determined by the HD simulations performed with the 2-D device simulator Minimos-NT, which is well suited for numerical analysis of GaN HEMTs [23], [24]. The HD transport model is a four-moment energy transport model [25] and provides the best physics-based description of the problem at a reasonable computational cost. Keeping in mind intervalley scattering can notable affect  $T_e$  distribution, a two-valley approach has been employed to approximate intervalley transfer at high fields. Here, a weighted mean of mobility in the lowest  $\Gamma$  valley and higher U valleys (assuming six equivalent valleys) was built with transport parameters (mobility, energy relaxation times, etc.) extracted from own Monte Carlo simulations [24]. A system of six partial differential equations: Poisson, current continuity, energy balance for electrons and holes, and the lattice heat flow (to account for self-heating effects) equations, is solved self-consistently. These equations have materialspecific parameters, such as the bandgap energy, electron mobility, thermal conductivity, and so on. The dependence of these parameters on temperature, carrier energy, and so on is described elsewhere [18]-[24]. InAlN/GaN HEMTs with 6-μm source-to-drain distance and the gate placed symmetrically between source and drain were used for the EL measurements and simulations. For comparison, EL spectra were also measured on commercial AlGaN/GaN HEMTs with 30-nm-thick Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer and 1.8-μm-thick GaN buffer grown on SiC substrate and similar geometry (6-µm sourceto-drain distance and 3- $\mu$ m gate-to-drain distance) operated at  $V_{\rm gs}=0$  V and  $V_{\rm ds}=30$  V. Finally, the channel temperature was investigated by micro-Raman thermography [26] with 488-nm laser excitation source.

HEMTs with 12- $\mu$ m source-to-drain distance (3.1- $\mu$ m source-to-gate and 7.1- $\mu$ m gate-to-drain distance) were

subjected to OFF and semi-ON state stress with  $V_{\rm gs} = -7$ and -3 V, respectively, for 10 h at room temperature. Note that, within the experimental error, similar values of  $T_e$  were determined for devices with 6- and 12- $\mu$ m sourceto-drain opening for the same conditions. It came from the simulations that both devices exhibit almost similar electric field and thus  $T_e$  distribution. A number of devices were stressed at  $V_{\rm gd} = 50$ , 75, and 100 V. However, only negligible permanent changes were observed for the devices stressed at  $V_{\rm gd}$  < 100 V. Therefore, only the results of the representative devices stressed at  $V_{\rm gd} = 100 \text{ V}$  are presented in the following ( $I_d$  during semi-ON state stress was about 160 mA/mm). Output and transfer characteristics in dc and pulsed mode (gate voltage was pulsed from quiescent bias of -5 V to a desired value with 100-ns-long pulse with 0.1% duty cycle, while  $V_{\rm ds}$  was dc biased) together with total resistance and end resistance measurements [16], [27] to determine the intrinsic channel resistance  $(R_{CH})$ , and source  $(R_S)$  and drain  $(R_D)$ resistances, respectively, were used to characterize the devices. Measurements were performed before and one week after the stress, to assess the permanent device degradation. RCH was obtained from the slope of the total resistance  $(R_T)$  measured with varying  $V_{gs}$  at  $V_{ds} = 0.2$  V. The  $R_S$  and  $R_D$  were then determined separately from the end resistance data as  $R_{S(D)} = R_{S(D)}^{\text{end}} - R_{\text{CH}}/2.$

To assess stress-induced trap generation in the devices,  $I_d$ transient analysis similar to [20] and [28] was performed on the fresh and stressed HEMTs at different temperatures. Here,  $I_d$  transients were measured in the logarithmic scale at  $V_{\rm gs}=1$  V and  $V_{\rm ds}=0.5$  V after applying a filling pulse with  $V_{gs,F} = -5$  V and  $V_{ds,F}$  in the range 0-20 V. The measured  $I_d$  transients were fitted with a function given by a sum of 15 exponentials of the form  $A_i \exp(-t/\tau_i)$ , where t denotes time,  $\tau_i$ -S are the time constants logarithmically divided along the measurement time, and  $A_i$ -S are the corresponding pre-exponential factors for i = 1, ..., 15. The fitted transients were then numerically derivated according to  $\log_{10} t$  to visualize the peaks with position giving the characteristic trap time constant and amplitude related to relative trap density. For analyzing bulk traps underneath the gate only,  $V_{\text{th}}$ -transient technique similar to [29] and [30] was applied to the gate contacts of the stressed devices. In this technique,  $V_{\text{th}}$  transients given as  $\Delta V_{\text{th}} = V_{\text{th}}(t)$  $0) - V_{th}(t)$  were determined from the capacitance transients measured in a two-terminal configuration (source and drain contacts grounded) at  $V_g = -5$  V after a filling pulse of  $V_{g,F} = 0$  V application. The  $V_{th}$  transients measured at different temperatures were analyzed in the same way as those of  $I_d$  transients.

# III. RESULTS AND DISCUSSION

### A. Electron Temperature Determination

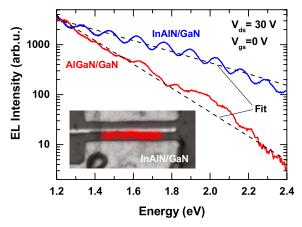

Fig. 1 shows the EL spectra measured on the InAlN/GaN HEMT for different  $V_{\rm gs}$  at the drain side of the gate in the middle of the transistor's finger (see the inset of Fig. 1). The spectra show a typical Maxwellian distribution [19]–[21], consistent with intraband radiative electron

Fig. 1. EL spectra of InAlN/GaN and reference AlGaN/GaN HEMTs operated at  $V_{\rm ds}=30~{\rm V}$  and  $V_{\rm gs}=0~{\rm V}$ . The oscillations in the spectra are related to Fabry–Perot interference fringes and therefore artifacts. Inset shows the overlap of optical and EL image of InAlN/GaN HEMT taken at  $V_{\rm ds}=30~{\rm V}$  and  $V_{\rm gs}=0~{\rm V}$ .

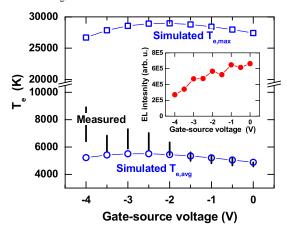

Fig. 2. Comparison between measured and simulated  $T_e - S$  as a function of  $V_{\rm gs}$  obtained at  $V_{\rm ds} = 30$  V. The vertical bars represent  $T_e$  determined from linear fits to the experimental data in the range of 1.2–2.4 and 1.4–2.2 eV. The data calculated using HD simulations (at the same bias conditions) are presented in a form of maximum ( $T_{e,\rm max}$ ) and averaged ( $T_{e,\rm avg}$ ) values.  $T_{e,\rm max}$  represents a peak value of the  $T_e$  distribution extracted along the channel at a distance of 30 nm below the quantum well, while  $T_{e,\rm avg}$  should correspond to the measured  $T_e$  (see the text and Fig. 3). Inset shows the EL intensity as a function of  $V_{\rm gs}$ .

transition [31]. The EL spectra can be thus interpreted using Maxwell–Boltzmann distribution in a form

$$EL \sim [k_B(T_e - T_{lat})]^{3/2} E^{1/2} \exp\left[-\frac{E}{k_B(T_e - T_{lat})}\right]$$

(1)

where E is the photon energy,  $T_{\rm lat}$  is the lattice temperature (determined by the Raman thermography), and  $k_B$  is Boltzmann's constant. It has been pointed out that the complexity of the light emission process in Si-based devices results in more complex relation between hot-electron distribution and photon energy distribution (i.e., EL spectrum) [32]. However, as the mechanism of EL in GaN-based devices is still under debate, hot-carrier energy distribution was assumed to correspond to that of photons.

$T_e$  as a function of  $V_{\rm gs}$  determined using (1) by fitting to the experimental data in the energy range of 1.2–2.4 eV (low values) and 1.4–2.2 eV (high values) is shown in Fig. 2 by vertical bars, illustrating the confidence band of the fitting.

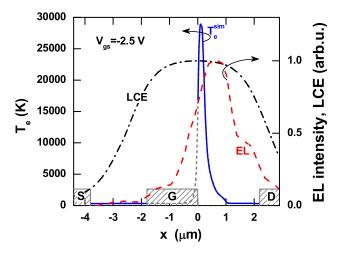

Fig. 3. Illustration of spatial averaging of the simulated  $T_e$  distribution (solid line, extracted along the channel at a distance of 30 nm below the quantum well). In the averaging, the product of the spectrometer LCE (dash-dotted line) and the measured EL intensity profile (dashed line) was used as a weighting function. Gate shadowing was considering by excluding  $T_e$  values laid underneath the gate (dashed area) from the averaging (short dashed line).

As the first approximation, the observed Fabry–Perot oscillation was neglected for the fitting procedure, since the signal spreads evenly across spectrum, assuming negligible impact on extracted  $T_e$ . The inset shows the corresponding EL intensity as a function of the gate bias. The experimentally measured  $T_e$ increases from  $\sim$ 4700 to  $\sim$ 8000 K with decreasing  $V_{\rm gs}$ . This is due to electric field increasing with increasing  $V_{\rm gd}$ , while the total EL intensity decreases as the channel is pinched off with decreasing  $V_{gs}$ . For comparison, AlGaN/GaN HEMT operated at  $V_{\rm ds} = 30$  V and  $V_{\rm gs} = 0$  V yielded  $T_e$  of  $\sim 2600$  K, i.e., nearly two-fold lower value compared with InAlN/GaN HEMTs. A higher  $T_e$  in the InAlN/GaN HEMTs compared with AlGaN/GaN counterparts can be understood as a result of higher polarization field (giving higher 2-DEG concentration) and thinner barrier layer for the former [1], resulting in higher vertical electric field necessary to control the channel [16]. Therefore, upon semi-ON or OFF state operation, a number of channel electrons are deflected toward the buffer with considerable higher energy.

As optical spectroscopy has a finite spatial resolution, the  $T_e$  values extracted from the EL spectra represent electron energy averaged over relatively large area of the GaN channel. A higher  $T_e$  can therefore be expected in the highly localized electric field peak. To analyze this in more detail, HD simulations of  $T_e$  and  $T_{lat}$  were performed for the devices analyzed here, and the summary of the results is given in Fig. 2. Interestingly, for InAlN/GaN HEMTs, maximum  $T_e$ increases from  $\sim$ 27000 to  $\sim$ 29000 K with  $V_{\rm gs}$  decreasing from 0 to -2.5 V, and then it decreases to  $\sim 27000$  K for  $V_{es} = -4$  V. The maximum  $T_e$  values are significantly higher than those measured by EL due to the spatial averaging in the measurement. It was found from the simulation data that, due to monotonic increase of the electric field with  $V_{\rm gd}$ , electron velocity decreases. Electron energy, being proportional to the product of electric field and electron velocity, then results in the bell-shaped electron temperature as a function of  $V_{gs}$ . This trend is in line with the Monte Carlo simulations of hot

electrons in AlGaN/GaN HEMTs [33], where a larger portion of electrons exceeded energies of 2.5 eV in device operated in semi-ON state compared with OFF state. The maximum  $T_e$  for the reference AlGaN/GaN HEMT at  $V_{gs} = 0$  V was found to be 11400 K (not shown). We note that our 2-D simulations did not account for the virtual gate effect that can mitigate electric field peak at the gate edge. However, in the steady-state saturation regime of the device reached during the EL measurements, most of trapping states located in the gate-to-drain access region can be expected to be detrapped, thus having less important impact on the resulting  $T_e$ .

To test the validity of the simulation, we considered the spatial averaging in the  $T_e$  measurement compared with very narrow distribution of hot electrons [full-width at halfmaximum (FWHM) ~250 nm] from simulations. In addition, part of the light emission is screened by the gate contact, which needs to be considered as well. To quantitatively account for these effects, the simulated  $T_e$  profiles were averaged in the access region parts of the transistor (top-view measurements) with a weighting function given by the product of normalized light collection efficiency (LCE) of the spectrometer and EL intensity profile measured at a given  $V_{gs}$ , as shown in Fig. 3 for  $V_{\rm gs} = -2.5$  V. LCE was determined from the convolution between charge-coupled device image area (five pixels corresponding to  $\sim$ 5.3  $\mu$ m) and the optical resolution (given by Voigt distribution with FWHM  $\sim 0.6 \mu m$ ). Such weighting function considers both the actual spatial distribution of the emitted light together with the collection efficiency of the spectrometer. The averaged  $T_e$  values are shown in Fig. 2, and a very good agreement between the measured values and those obtained from the simulations can be inferred, in particular, when the EL signal was large and error bars therefore small. Discrepancy between the experimental and simulated data obtained for  $V_{gs} = -4$  V can be understood as a consequence of the simplifications introduced in the model mentioned above, neglected hot electrons injected from the gate, and lower light intensity at low-current levels resulting into a larger error in the measurement, as illustrated by the vertical bars in Fig. 2. The averaging of the simulated T<sub>e</sub> distribution for AlGaN/GaN HEMT resulted in a value of 2300 K (not shown), i.e., similar to the experimental value (2600 K).

Regarding the extracted  $T_e$  from EL measurements, to our knowledge, there are no experimental data reported in the literature for InAlN/GaN HEMTs, in contrast to the many results for AlGaN/GaN devices. Shigekawa et al. [19] extracted T<sub>e</sub> of 2000–2400 K at  $V_{gd} = 30$  V, while in [21]–[34] and [35], similar  $T_e$  of 1700 K was reported at  $V_{gd} = 40, 28.5$ , and 10 V, respectively. A substantially higher  $T_e$  of 5000 K at  $V_{\rm gd}$  = 30 V was determined in [20] from backside wafer EL measurement, thus without gate shadowing. Measurement performed here on the commercial AlGaN/GaN HEMTs yielded T<sub>e</sub> of 2600 K at  $V_{\rm gd} = 30$  V, agreeing reasonably well with those measured by EL collected from the top side [19], [21], [34], [35]. As T<sub>e</sub> determined here for InAlN/GaN HEMTs is two to three times higher compared with that for AlGaN/GaN devices, hot-electron degradation can be expected to be the major concern for InAlN/GaN devices. The analysis

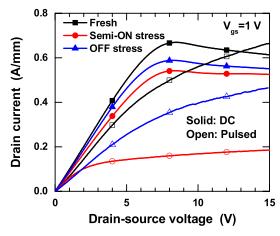

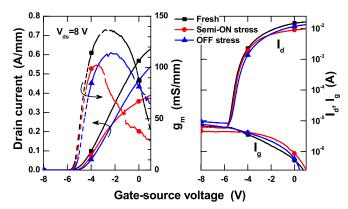

Fig. 4. Output characteristics of InAlN/GaN HEMTs measured in dc (solid symbols) and pulsed (open symbols) mode before and one week after OFF and semi-ON state stress performed at  $V_{\rm gd}=100$  V. For clarity, only characteristics for  $V_{\rm gs}=1$  V are shown. For pulsed measurements, gate voltage was pulsed for 100 ns from quiescent bias of -5 V while the drain was dc biased.

Fig. 5. DC transfer (solid lines) and transconductance (dashed lines) characteristics of InAlN/GaN HEMTs in linear (left) and semilog (right) scale, measured at  $V_{\rm ds}=8$  V before and one week after OFF and semi-ON state stress. Note negligible increase in the gate leakage (left) after stressing in both bias conditions.

suggests that  $T_e$  as high as 30 000 K can be locally reached at  $V_{\rm gd}=33$  V, corresponding to electron energy similar to 2.6 eV.

### B. Electrical Stressing

Fig. 4 shows the output characteristics measured in dc and pulsed mode before and after OFF and semi-ON state stress. Regarding the dc measurements, maximum  $I_d$  decreased by about 14% and 19% after OFF and semi-ON state stressing, respectively. Stronger degradation after semi-ON state stressing was observed also for static ON state resistance ( $R_{\rm ON}$ , determined from the linear part of the output characteristics), where  $R_{\rm ON}$  decreased by about 9% and 12% after stressing in OFF and semi-ON state stressing, respectively. Output characteristics measured in the pulsed mode also shown in Fig. 5 suggest strongest degradation after semi-ON state stressing, indicating trap generation in the intrinsic region of the transistor [36].

The transfer characteristics before and after stressing are shown in Fig. 5. Much stronger degradation in the

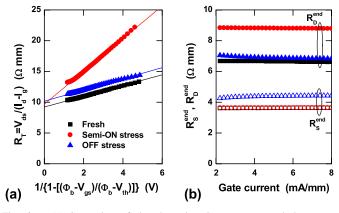

Fig. 6. (a) Separation of the channel resistance  $R_{\rm CH}$  and the access resistances  $R_S + R_D$ , proportional to the slope and intercept of the linear fit to the data, respectively. (b) Direct measurement of the source and drain end resistances as a function of gate current, performed before and one week after OFF and semi-ON state stressing.

$\label{thm:constraint} TABLE\ I$  Summary of the Electrical Parameters of InAlN/GaN HEMTs Before and After off and Semi-on State Stress

| Parameter                                                    | Fresh | OFF stress | Semi-ON stress |

|--------------------------------------------------------------|-------|------------|----------------|

| $R_{\mathrm{CH}}\left(\Omega\mathrm{mm}\right)$              | 0.8   | 0.9        | 2.7            |

| $R_{\rm S}\left(\Omega { m mm}\right)$                       | 3.2   | 4.0        | 2.3            |

| $R_{\rm D}\left(\Omega{ m mm}\right)$                        | 6.2   | 6.2        | 7.5            |

| $R_{\mathrm{ON}}\left(\Omega\mathrm{mm}\right)^{\mathrm{a}}$ | 10.3  | 11.2       | 12.1           |

| $V_{th}$ $(V)$                                               | -4.7  | -4.4       | -4.7           |

| $I_{d,max} \left( A/mm \right)^{b}$                          | 0.67  | 0.58       | 0.54           |

<sup>&</sup>lt;sup>a</sup>Determined from the linear part of the output characteristics.

transconductance  $(g_m)$  took place after stressing in semi-ON state compared with OFF state; as apart from the maximum value degradation, a strong decrease in  $g_m$  for higher  $V_{gs}$ was observed. In contrast, a similar trend of  $g_m$  dependence on  $V_{\rm gs}$  can be inferred from Fig. 5 for fresh and OFF-state stressed devices. On the other hand, a notable  $V_{\rm th}$  shift from -4.7 to -4.4 V took place only for devices stressed in the OFF state, while it remained the same after semi-ON stressing. As apparent from the semilog plot of the transfer and input characteristics, the gate leakage current  $(I_g)$  did not degrade for neither of the here considered stress conditions. These results suggest a stronger degradation of HEMTs stressed in semi-ON state. Moreover, the difference in  $g_m - V_{gs}$  trend and  $V_{\rm th}$  shift suggest distinct differences in the degradation mechanisms for HEMTs submitted to OFF and semi-ON state stressing. Note the slightly lower saturation  $I_d$  measured by the transfer characteristic compared with that from the output characteristic for HEMT stressed in semi-ON state. This can be attributed to increased trapping in the device after the stressing.

To analyze the location of the degradation,  $R_{\rm CH}$ ,  $R_S$ , and  $R_D$  were measured before and after stress, as shown in Fig. 6. The results are summarized in Table I together with  $V_{\rm th}$ , maximum  $I_d$ , and  $R_{\rm ON}$ . A good agreement between  $R_S + R_{\rm CH} + R_D$  and  $R_{\rm ON}$  determined independently can be inferred from Table I, validating the performed analysis.  $R_{\rm CH}$  was found to increase significantly from 0.8 for fresh device

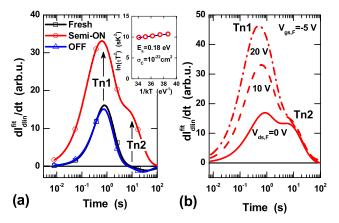

Fig. 7. (a) Analysis of the  $I_d$  transients measured on InAlN/GaN HEMTs at room temperature before and one week after OFF and semi-ON state stressing, showing dominant peak labeled as Tn1 with activation energy of 0.18 eV (inset,  $T=25-65\,^{\circ}\text{C}$ ). A new peak labeled as Tn2 became apparent for semi-ON stressed device only. (b) Analysis of the  $I_d$  transients measured on the device stressed in semi-ON state with different  $V_{ds}$  applied during the filling pulse  $(V_{ds},F)$  and keeping  $V_{gs},F=-5\,$  V. While Tn1 amplitude strongly increases with  $V_{ds},F$  increase, Tn2 amplitude remains invariant of  $V_{ds},F$ .

to 2.7  $\Omega$  mm (by more than 200%) after semi-ON stressing. This was accompanied with a slight increase in  $R_D$  (by 30%) and slight decrease in  $R_S$ . However, decrease in  $R_S$  could be an artifact originated from the  $R_{\rm CH}$  extraction, e.g., stronger degradation of the intrinsic region close to the drain side would lead to  $R_S$  underestimation. In contrast, only negligible change in  $R_{\rm CH}$  took place for OFF state stress, and slight increase in  $R_S$  from 3.2 for fresh device to 4  $\Omega$  mm for stressed device was observed, while  $R_D$  remained unchanged after OFF state stressing.

To correlate intrinsic and access resistances degradation with stress-induced trap generation,  $I_d$  and  $V_{th}$  transients were measured and analyzed on fresh and stressed devices. Fig. 7(a) shows the analysis of  $I_d$  transients of fresh and stressed HEMTs measured at room temperature. In all devices, a dominant electron-like detrapping process with time constant  $(\tau)$  of  $\sim$ 800 ms can be inferred from the analysis (labeled as Tn1 in the following). Almost the same trapping signature was determined for fresh and OFF state stressed device, suggesting negligible Tn1 trap generation. In contrast, semi-ON state stressing resulted in strong increase in Tn1 amplitude (by  $\sim$ 100%), suggesting increase in Tn1 trap density. In addition, a new electron-like detrapping process labeled as Tn2 became visible after semi-ON state stressing, manifesting itself as a shoulder of Tn1 with time constant similar to 10 s.

The activation energy ( $E_a$ ) and capture cross section ( $\sigma_C$ ) of Tn1 determined from the Arrhenius plot [see the inset of Fig. 8(a)] was found to be 0.18 eV and  $\sim 10^{-22}$  cm<sup>2</sup>, respectively, for all devices. Such small  $E_a$  and  $\sigma_C$  suggest that Tn1 does not represent a bulk trap emission process. Instead, it can be assigned to the electron emission from the surface/interface traps in the transistor access region, governed by the hopping process, as proposed in [37] and [38]. To support this interpretation,  $I_d$  transients of the device stressed in semi-ON state were measured after applying a filling pulse with  $V_{\rm ds, \it F} = 0$ , 10, and 20 V ( $V_{\rm gs, \it F} = -5$  V), and the results are shown in Fig. 7(b). The amplitude of

<sup>&</sup>lt;sup>a</sup>Extracted at  $V_{ds}$ =8 V and  $V_{gs}$ =1 V.

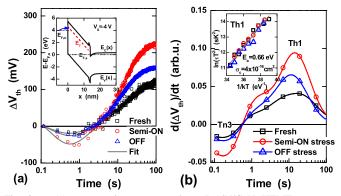

Fig. 8. (a)  $V_{\rm th}$  transients measured on InAlN/GaN HEMTs at room temperature before and one week after OFF and semi-ON state stressing. (b) Corresponding analyses show similar dominant hole-like emission process (Th1) and electron-like emission process (Tn3) in devices before and after stressing, with stress-induced changes in the peak amplitudes. Inset of (a) depicts the interpretation of Th1 process as trapping of electrons in the InAlN barrier. Electrons are supposed to be injected from the gate via thermionic field emission. Arrhenius plot of the Th1 emission process [inset of (b), T=25–65 °C] yielded the same  $E_a$  of 0.66 eV for fresh and stressed devices.

Tn1 was found to increase linearly with the  $V_{ds,F}$  amplitude, i.e., increasing the lateral electric field during the trap filling. This behavior is consistent with hopping-driven emission from surface/interface traps located in the gate-to-drain region that are filled ever further away from the drain side of the gate edge with increasing  $V_{ds,F}$ . The data in Fig. 7(a) therefore indicate that semi-ON state stress results in increased density of pre-existing surface/interface traps located in the gate-todrain access region. In contrast, generation of such traps is negligible during OFF-state stress. This is consistent with the  $R_D$  data (Table I) and, to some extent, also with pulsed output characteristics, as  $R_D$  was found to increase only after semi-ON stressing. Note that generation of faster traps ( $\tau$  < 10 ms) during OFF-state stress can be attributed to some knee voltage walkout of the pulsed output characteristics (Fig. 4), while this effect was not observable by the  $I_d$  transient and end resistance measurements. Due to dominant Tn1 process, it was not possible to extract trap signature of Tn2 process, therefore it is not discussed in the following.

Unlike  $I_d$  transient,  $V_{th}$  transients are mostly sensitive to traps located underneath the gate, i.e., also those potentially affecting  $R_{CH}$  via mobility degradation. The  $V_{th}$  transients measured on fresh and stressed devices at 25 °C are shown in Fig. 8 together with the corresponding analyses. As can be inferred from Fig. 8(b), two emission processes were identified in all devices: 1) an electron-like detrapping process with  $\tau$  of  $\sim$ 100 ms labeled as Tn3 and 2) a broad hole-like emission process with  $\tau$  centered at about 20 s labeled as Th1. While only negligible increase in Tn3 amplitude was observed after OFF state stressing, it increased significantly (by 150%) after semi-ON state stressing. The amplitude of Th1 increased by about 60% and 130% after OFF and semi-ON state stressing, respectively.

Unfortunately, it was not possible to determine  $E_a$  and  $\sigma_C$  of Tn3 due to a limited time response of the standard capacitance meter. Nevertheless, this process could be assigned to electron emission of bulk traps located in the GaN buffer, as it was

filled even with  $V_g = 0$  filling pulse. Note that  $V_{gs} > 0$  V would be necessary to fill traps near the conduction band of the InAlN barrier layer. Th1 process showed well-defined  $E_a$  and  $\sigma_C$  of 0.66 eV and  $4 \times 10^{-16}$  cm<sup>2</sup>, respectively, for fresh as well as stressed devices. Hole trap feature has been reported for InAlN/GaN HEMTs using gate controlled constant- $I_d$  deep-level transient spectroscopy [39]. The holelike emission process observed here is, however, unlikely to be related to a real hole emission. Even though generation of holes in InAlN can be expected already at  $V_{\rm gs} = -4$  V [as deduced from the Poisson-Schrödinger calculation of the band diagram shown in the inset of Fig. 8(a)], generated holes would be immediately injected into the metal. Instead, holelike emission process can be attributed to electron trapping in the InAlN barrier. The electrons injected from the gate by thermionic field emission can be captured by traps, as shown in the inset of Fig. 8(a). Similar effect has been recently reported for Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS HEMTs [30]. In contrast to monotonic increase of  $V_{\rm th}$  with time observed in [30], the faster electron emission observed here affects the trapping process at the beginning of the transient. The measured  $E_a$  can be then interpreted as a difference between the metal Fermi level and the trap level in InAlN.

$V_{\rm th}$  transient analysis therefore indicates prominent generation of pre-existing type of traps in the GaN buffer after semi-ON state stress, while both OFF state and semi-ON state stresses are likely to increase the density of pre-existing traps in the InAlN barrier layer. This is consistent with the stress-induced  $R_{\rm CH}$  changes, assuming stronger effect of GaN bulk traps located close to the channel compared with those located at the InAlN surface. Finally, we note that even though dc transfer characteristics showed similar  $V_{\rm th}$  for devices before and after semi-ON state stress,  $V_{\rm th}$  transient analysis revealed more profound  $V_{\rm th}$  drift for the stressed device. However, counteracting Tn3 and Th1 processes can effectively cancel out each other at a steady-state condition reached during the dc measurement.

### C. Hot-Electron Degradation

Strong degradation of  $R_{CH}$  and saturation  $I_d$  measured in the pulsed mode in the devices submitted to semi-ON stressing together with no degradation of the gate leakage current suggest hot-electron driven degradation in InAlN/GaN HEMTs. This is consistent with stress-induced degradation of  $R_{\rm CH}$  in InAlN/GaN devices reported in [15]–[17], keeping in mind possible punchthrough effect in short-channel devices analyzed in [16], explaining faster onset of  $R_{CH}$  degradation upon OFF state compared with semi-ON state stressing. Following the assignment of the trapping processes in the previous section, R<sub>CH</sub> degradation can be related to Tn3 electron emission in the GaN bulk deduced from the  $V_{th}$ transient analysis, keeping in mind a good correlation between the stress-induced changes in the magnitude of  $R_{CH}$  and Tn3 amplitude. Ionized donor levels responsible for Tn3 emission could serve as efficient scattering centers in the transistor's channel. On the other hand, generation of preexisting (Tn1) and new surface/interface traps in the gate-to-drain (Tn2) can be related to less dominant  $R_{\rm D}$  degradation, whereas possible trapping in the InAlN barrier can be related to both hotelectron related trap generation as well as gate electron injection at large  $V_{\rm gd}=100$  V. Therefore, in terms of hot-electron trap generation in GaN HEMTs, the emission process Tn3, ascribed to GaN bulk trap emission, is likely to represent the most relevant trap. Work toward characterizing the trap level signature is ongoing.

Regarding the physical mechanism under hot-electron degradation in the GaN buffer, a release of hydrogen by hot electrons from a pre-existing defect, such as hydrogenated Ga vacancy, N antisite, or divacancy, has been proposed in [40]–[42]. The energy necessary for hydrogen removal from triply hydrogenated Ga vacancy and divacancy and placing the atom into  $H_2$  molecule has been calculated to be 2.2 and 2.0 eV, respectively [42]–[44]. If we assume this mechanism to take place, it comes from the  $T_e$  analysis that hot electrons have enough energy to strip one or more electrons from both defects during stressing, even though other mechanism cannot be ruled out.

### IV. CONCLUSION

Hot-electron temperature was analyzed in InAlN/GaN HEMTs using EL spectroscopy and HD simulations.  $T_e$  in the range of 4700-8000 K was determined for InAlN/GaN HEMTs as a function of  $V_{gs}$  at  $V_{ds} = 30$  V. Similar AlGaN/GaN HEMT yielded  $T_e$  of 2600 K at  $V_{gs} = 0$  and  $V_{\rm ds} = 30$  V. Good agreement between measurement and averaging of the calculated  $T_e$  distribution indicates that hot electrons can locally reach temperature of up to 30000 K. To illustrate the effect of high  $T_e$ , InAlN/GaN HEMTs were stressed at  $V_{\rm gd} = 100$  V. Strong  $R_{\rm CH}$  degradation taking place only upon semi-ON state suggests hot-electron driven degradation. The  $V_{th}$  and  $I_d$  transient analyses revealed four trap emission processes affected by hot-electron degradation. Among them, electron emission with  $\tau \sim 100$  ms at room temperature, ascribed to pre-existing GaN buffer trap, was proposed to be related to the hot-electron-induced  $R_{\rm CH}$  degradation. Possible mechanism for the trap generation via dehydrogenation was discussed.

## REFERENCES

- J. Kuzmik, "Power electronics on InAlN/(In)GaN: Prospect for a record performance," *IEEE Electron Device Lett.*, vol. 22, no. 11, pp. 510–512, Nov. 2001.

- [2] R. Wang et al., "Gate-recessed enhancement-mode InAIN/AIN/GaN HEMTs with 1.9-A/mm drain current density and 800-mS/mm transconductance," IEEE Electron Device Lett., vol. 31, no. 12, pp. 1383–1385, Dec. 2010.

- [3] S. Tirelli et al., "Fully passivated AlInN/GaN HEMTs with f<sub>T</sub>/f<sub>MAX</sub> of 205/220 GHz," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1364–1366, Oct. 2011.

- [4] D. S. Lee, X. Gao, S. Guo, D. Kopp, P. Fay, and T. Palacios, "300-GHz InAlN/GaN HEMTs with InGaN back barrier," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1525–1527, Nov. 2011.

- [5] S. Piotrowicz et al., "160 W InAlN/GaN HEMTs amplifier at 2 GHz with optimized thermal management," in Proc. IEEE Compound Semicond. Integr. Circuit Symp., Oct. 2012, pp. 1–4.

- [6] Y. Yue et al., "Ultrascaled InAlN/GaN high electron mobility transistors with cutoff frequency of 400 GHz," Jpn. J. Appl. Phys., vol. 52, no. 8, p. 08JN14, Aug. 2013.

- [7] B. Lu, M. Sun, and T. Palacios, "An etch-stop barrier structure for GaN high-electron-mobility transistors," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 369–371, Mar. 2013.

- [8] M. Jurkovič et al., "Schottky-barrier normally off GaN/InAlN/AlN/GaN HEMT with selectively etched access region," IEEE Electron Device Lett., vol. 34, no. 3, pp. 432–434, Mar. 2013.

- [9] J. Joh and J. A. del Alamo, "Critical voltage for electrical degradation of GaN high-electron mobility transistors," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 287–289, Apr. 2008.

- [10] J. L. Jimenez and U. Chowdhury, "X-band GaN FET reliability," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr./May 2008, pp. 429–435.

- [11] F. Gao et al., "Role of oxygen in the OFF-state degradation of AlGaN/GaN high electron mobility transistors," Appl. Phys. Lett., vol. 99, no. 22, pp. 223506-1–223506-3, Nov. 2011.

- [12] L. Li, J. Joh, J. A. del Alamo, and C. V. Thompson, "Spatial distribution of structural degradation under high-power stress in AlGaN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, vol. 100, no. 17, pp. 172109-1–172109-3, Apr. 2012.

- [13] M. Ťapajna, U. K. Mishra, and M. Kuball, "Importance of impurity diffusion for early stage degradation in AlGaN/GaN high electron mobility transistors upon electrical stress," *Appl. Phys. Lett.*, vol. 97, no. 2, pp. 023503-1–023503-3, Jul. 2010.

- [14] M. M. Bajo, C. Hodges, M. J. Uren, and M. Kuball, "On the link between electroluminescence, gate current leakage, and surface defects in AlGaN/GaN high electron mobility transistors upon off-state stress," Appl. Phys. Lett., vol. 101, no. 3, pp. 033508-1–033508-4, Jul. 2012.

- [15] J. Kuzmik et al., "Analysis of degradation mechanisms in lattice-matched InAlN/GaN high-electron-mobility transistors," J. Appl. Phys., vol. 106, no. 12 pp. 124503-1–124503-7, Dec. 2009.

- [16] J. Kuzmik et al., "Buffer-related degradation aspects of single and double-heterostructure quantum well InAlN/GaN high-electron-mobility transistors," *Jpn. J. Appl. Phys.*, vol. 51, no. 5R, pp. 054102-1–054102-5, May 2012.

- [17] C. Y. Zhu et al., "Degradation and phase noise of InAlN/AlN/GaN heterojunction field effect transistors: Implications for hot electron/phonon effects," Appl. Phys. Lett., vol. 101, no. 10, pp. 103502-1–103502-4, Sep. 2012.

- [18] V. Palankovski, G. Donnarumma, and J. Kuzmik, "Degradation study of single and double-heterojunction InAlN/GaN HEMTs by two-dimensional simulation," ECS Trans., vol. 50, no. 3, pp. 223–228, 2012.

- [19] N. Shigekawa, K. Shiojima, and T. Suemitsu, "Optical study of high-biased AlGaN/GaN high-electron-mobility transistors," *J. Appl. Phys.*, vol. 92, no. 1, pp. 531–535, Jul. 2002.

- [20] M. Ťapajna, R. J. T. Simms, Y. Pei, U. K. Mishra, and M. Kuball, "Integrated optical and electrical analysis: Identifying location and properties of traps in AlGaN/GaN HEMTs during electrical stress," *IEEE Electron Device Lett.*, vol. 31, no. 7, pp. 662–664, Jul. 2010.

- [21] J. W. Pomeroy, M. Kuball, M. J. Uren, K. P. Hilton, R. S. Balmer, and T. Martin, "Insights into electroluminescent emission from AlGaN/GaN field effect transistors using micro-Raman thermal analysis," *Appl. Phys. Lett.*, vol. 88, no. 2, pp. 023507-1–023507-3, Jan. 2006.

- [22] N. Killat, M. J. Uren, D. J. Wallis, T. Martin, and M. Kuball, "Origin of kink effect in AlGaN/GaN high electron mobility transistors: Yellow luminescence and Fe doping," *Appl. Phys. Lett.*, vol. 101, no. 15, pp. 153505-1–153505-4, Oct. 2012.

- [23] S. Vitanov, V. Palankovski, S. Maroldt, and R. Quay, "High-temperature modeling of AlGaN/GaN HEMTs," *Solid-State Electron.*, vol. 54, no. 10, pp. 1105–1112, Oct. 2010.

- [24] S. Vitanov et al., "Physics-based modeling of GaN HEMTs," IEEE Trans. Electron Devices, vol. 59, no. 3, pp. 685–693, Mar. 2012.

- [25] T. Grasser, T.-W. Tang, H. Kosina, and S. Selberherr, "A review of hydrodynamic and energy-transport models for semiconductor device simulation," *Proc. IEEE*, vol. 91, no. 2, pp. 251–274, Feb. 2003.

- [26] R. J. T. Simms, J. W. Pomeroy, M. J. Uren, T. Martin, and M. Kuball, "Channel temperature determination in high-power AlGaN/GaN HFETs using electrical methods and Raman spectroscopy," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 478–482, Feb. 2008.

- [27] K. Lee, M. Shur, K. W. Lee, T. Vu, P. Roberts, and M. Helix, "A new interpretation of 'End' resistance measurements," *IEEE Electron Device Lett.*, vol. 5, no. 1, pp. 5–7, Jan. 1984.

- [28] J. Joh and J. A. del Alamo, "A current-transient methodology for trap analysis for GaN high electron mobility transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 132–140, Jan. 2011.

- [29] M. Ťapajna et al., "Thermally induced voltage shift in capacitance–voltage characteristics and its relation to oxide/semiconductor interface states in Ni/Al<sub>2</sub>O<sub>3</sub>/InAlN/GaN heterostructures," Semicond. Sci. Technol., vol. 24, no. 3, pp. 035008-1–035008-5, Mar. 2009.

- [30] M. Ťapajna et al., "Bulk and interface trapping in the gate dielectric of GaN based metal-oxide-semiconductor high-electron-mobility transistors," Appl. Phys. Lett., vol. 102, no. 24, pp. 243509-1–243509-4, Jun. 2013.

- [31] F. Gütle et al., "Radiative inter-valley transitions as a dominant emission mechanism in AlGaN/GaN high electron mobility transistors," Semicond. Sci. Technol., vol. 27, no. 12, pp. 125003-1–125003-6, Oct. 2012.

- [32] L. Selmi et al., "Verification of electron distributions in silicon by means of hot carrier luminescence measurements," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 802–808, Apr. 1998.

- [33] S. Mukherjee *et al.*, "Role of bias conditions in the hot carrier degradation of AlGaN/GaN high electron mobility transistors," *Phys. Status Solidi C*, vol. 10, no. 5, pp. 794–798, May 2013.

- [34] E. Zanoni et al., "A review of failure modes and mechanisms of GaN-based HEMTs," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2007, pp. 381–384.

- [35] M. Meneghini et al., "Extensive analysis of the luminescence properties of AlGaN/GaN high electron mobility transistors," Appl. Phys. Lett., vol. 97, no. 6, pp. 063508-1–063508-3, Aug. 2010.

- [36] J. Kuzmik et al., "Gate-lag and drain-lag effects in (GaN)/InAlN/GaN and InAlN/AlN/GaN HEMTs," Phys. Status Solidi A, vol. 204, no. 6, pp. 2019–2022, Jun. 2007.

- [37] G. Meneghesso et al., "Trapping phenomena in AlGaN/GaN HEMTs: A study based on pulsed and transient measurements," Semicond. Sci. Technol., vol. 28, no. 7, pp. 074021-1-074021-8, Jul. 2013.

- [38] M. Ťapajna, J. L. Jimenez, and M. Kuball, "On the discrimination between bulk and surface traps in AlGaN/GaN HEMTs from trapping characteristics," *Phys. Status Solidi A*, vol. 209, no. 2, pp. 386–389, Feb. 2012.

- [39] A. Sasikumar et al., "Direct comparison of traps in InAlN/GaN and AlGaN/GaN high electron mobility transistors using constant drain current deep level transient spectroscopy," Appl. Phys. Lett., vol. 103, no. 3, pp. 033509-1–033509-4, Jul. 2013.

- [40] Y. S. Puzyrev, B. R. Tuttle, R. D. Schrimpf, D. M. Fleetwood, and S. T. Pantelides, "Theory of hot-carrier-induced phenomena in GaN high-electron-mobility transistors," *Appl. Phys. Lett.*, vol. 96, no. 5, pp. 053505-1–053505-3, 2010.

- [41] T. Roy et al., "Electrical-stress-induced degradation in AlGaN/GaN high electron mobility transistors grown under gallium-rich, nitrogen-rich, and ammonia-rich conditions," Appl. Phys. Lett., vol. 96, no. 13, pp. 133503-1–133503-3, Mar. 2010.

- [42] Y. S. Puzyrev et al., "Dehydrogenation of defects and hot-electron degradation in GaN high-electron-mobility transistors," J. Appl. Phys., vol. 109, no. 3, pp. 034501-1–034501-8, Feb. 2011.

- [43] C. G. van de Walle, "Interactions of hydrogen with native defects in GaN," *Phys, Rev. B*, vol. 56, no. 16, p. R10020, Oct. 1997.

- [44] A. F. Wright, "Interaction of hydrogen with gallium vacancies in wurtzite GaN," J. Appl. Phys., vol. 90, no. 3, pp. 1164–1169, Aug. 2001.

Nicole Killat received the Degree from the Ilmenau University of Technology, Ilmenau, Germany, in 2008, and the Ph.D. degree in physics from the University of Bristol, Bristol, U.K., in 2012.

Her current research interests include the thermal and electrical properties of GaN-based devices and the investigation of device reliability issues using micro-Raman and electroluminescence spectroscopy.

Vassil Palankovski received the Dipl.Ing. degree in electronics from Technical University Sofia, Sofia, Bulgaria, in 1993, and the Ph.D. degree in technical sciences from Technische Universität Wien, Wien, Austria, in 2000.

He has been with Technische Universität Wien since 2005, where he established the Advanced Material and Device Analysis Group.

Dagmar Gregušová received the M.S. degree in solid-state physics from the Faculty of Mathematics, Physics and Informatics, Comenius University Bratislava, Bratislava, Slovakia, and the Ph.D. degree in microelectronics engineering from the Slovak Academy of Sciences, Bratislava, in 1995.

She is currently a Senior Researcher with the Institute of Electrical Engineering, Slovak Academy of Sciences.

**Karol Čičo** received the Ph.D. degree in electronics engineering from the Slovak University of Technology, Bratislava, Slovakia, in 2010.

He is currently a Senior Researcher with the Institute of Electrical Engineering, Slovak Academy of Sciences, Bratislava. His current research interests include the processing of semiconductor devices.

He has been in charge of the MOCVD growth facilities for widebandgap nitride semiconductors at EPFL since 2002. His current research interests include GaN-based electronics and optoelectronics, in particular, the development of blue VCSELs.

Milan Ťapajna received the Ph.D. degree in electronics engineering from the Slovak University of Technology, Bratislava, Slovakia, in 2007.

He is currently a Senior Researcher with the Institute of Electrical Engineering, Slovak Academy of Sciences, Bratislava. His current research interests include the electrooptical characterization and reliability of microwave and switching GaN-based devices, in particular, MOS-HEMTs.

**Nicolas Grandjean** received the Ph.D. degree in physics in 1994.

He has been the Director of the Institute of Condensed Matter Physics, Ecole Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, since 2012. His current research interests include the physics and technology of III–V nitride semiconductors, and in particular, microcavities, quantum dots, lasers, and 2-D electron gas heterostructures.

**Martin Kuball** received the Ph.D. degree from the Max-Planck-Institute, Stuttgart, Germany.

He joined the faculty at the University of Bristol, Bristol, U.K., in 1997, where he leads the Center for Device Thermography and Reliability, an interdisciplinary research center between Science and Engineering.

**Ján Kuzmík** received the Ph.D. degree from the Slovak Academy of Sciences (SAS), Bratislava, Slovakia, in 1991.

He is currently a Leading Researcher with the Institute of Electrical Engineering at SAS. He has authored and co-authored more than 80 scientific papers.

Dr. Kuzmík was a Program Committee Member of the 2010 International Workshop on Nitride Semiconductors, Tampa, FL, USA.