|

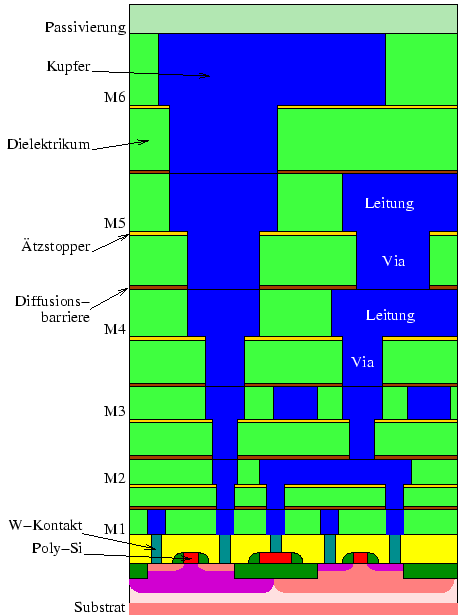

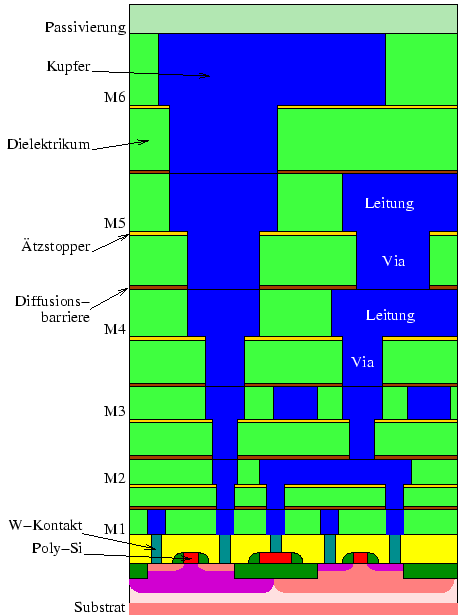

Abbildung 1.1 zeigt einen Querschnitt durch einen typischen CMOS Chip.

|

Die Höhe der Leitungen in den Ebenen M1 und M2 liegt im Bereich von

[500]nm, ihre Breite ist etwas geringer1.1.

Als Leitermaterialien werden Aluminium oder Kupfer verwendet.

Da der Querschnitt sehr klein ist, haben die Leitungen einen hohen Widerstand

je Längeneinheit ([100]![]() mm und darüber).

Gemeinsam mit Leitungen aus Poly-Silizium direkt über dem Substrat

werden sie für kurze lokale Verbindungen genutzt.

Für Leitungen über große und mittlere Distanzen werden die oberen

Metallisierungsebenen in Anspruch genommen, die einen größeren Querschnitt

haben und daher auch geringere Verluste aufweisen.

Die Anzahl der Verbindungsstrukturschichten kann je nach Art der integrierten

Schaltung unterschiedlich sein.

Typischerweise werden in dynamischen Speichern 2-3 Lagen und in

Mikroprozessoren 6-7 Schichten verwendet.

Die Gesamtlänge aller Verbindungsleitungen kann in einem Chip bis über

[1]km betragen.

mm und darüber).

Gemeinsam mit Leitungen aus Poly-Silizium direkt über dem Substrat

werden sie für kurze lokale Verbindungen genutzt.

Für Leitungen über große und mittlere Distanzen werden die oberen

Metallisierungsebenen in Anspruch genommen, die einen größeren Querschnitt

haben und daher auch geringere Verluste aufweisen.

Die Anzahl der Verbindungsstrukturschichten kann je nach Art der integrierten

Schaltung unterschiedlich sein.

Typischerweise werden in dynamischen Speichern 2-3 Lagen und in

Mikroprozessoren 6-7 Schichten verwendet.

Die Gesamtlänge aller Verbindungsleitungen kann in einem Chip bis über

[1]km betragen.

Eine wichtige Rolle spielt auch das Dielektrikum, das den Raum zwischen den

Leitungen füllt. Es soll eine möglichst geringe Dielektrizitätszahl

aufweisen, um kapazitive Kopplungen zwischen den Leitern gering zu halten,

muss aber auch gewisse mechanische und thermische Anforderungen erfüllen.

Es wird dafür hauptsächlich SiO![]() verwendet (

verwendet (

![]() ),

inwieweit andere Materialien mit kleinerer Dielektrizitätszahl geeignet sind,

wird zur Zeit experimentell untersucht (beispielsweise in [2]).

),

inwieweit andere Materialien mit kleinerer Dielektrizitätszahl geeignet sind,

wird zur Zeit experimentell untersucht (beispielsweise in [2]).