|

|

||||

BiographyJakob Michl was born in Freistadt, Austria, in 1993. He received his MSc degree in Physics from the University of Vienna in 2018. He joined the Institute for Microelectronics in January 2019, where he is currently working on his doctoral degree. |

|||||

Charge Trapping at Cryogenic Temperatures

State-of-the-art quantum computers use a small number of qubits that operate in the temperature range of several milli-Kelvin. In order to scale up the number of qubits to solve "real-world" problems, one of the limiting factors is the quantum-classical interface (QCI). Many readout and control components are needed between the qubits, and a classical computer is needed to run quantum algorithms successfully and to perform error correction protocols. To minimize losses due to the large temperature gradients, the QCI should be integrated inside the high-vacuum stage of the cryostat. In order to develop circuits operating at the highest performance at cryogenic temperatures, it is necessary to understand the characteristics and degradation mechanisms of the applicable CMOS technologies under these extreme operating conditions.

Reliability issues, such as hot carrier degradation (HCD), bias temperature instability (BTI) or random telegraph noise (RTN), can be explained by charge trapping using nonradiative multi-phonon (NMP) theory. While charge trapping above room temperature is described as a thermally activated process and can thus be described with an Arrhenius law, it is necessary to include quantum mechanical effects, such as nuclear tunneling at cryogenic temperatures. Nuclear tunneling can be explained by the overlap of the nuclear wave functions below the classical barrier. Even at cryogenic temperatures, the ground-state is occupied and ground-state wave functions can overlap, enabling tunneling. Therefore, BTI and RTN do not freeze-out at low temperatures, as would be classically expected.

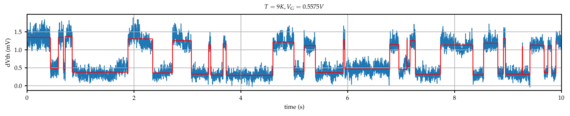

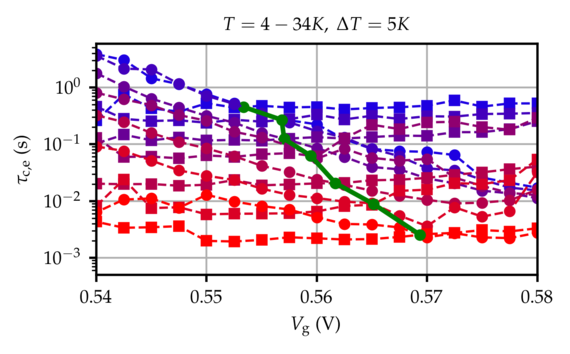

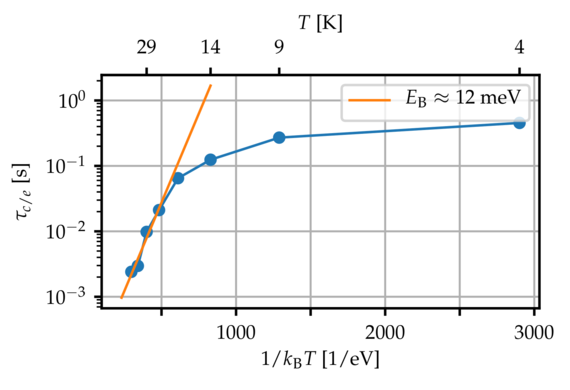

This can be seen in a sample RTN trace in Fig. 1, which was measured at 9 K. By performing RTN measurements between 4K and 34K for a range of gate voltages it is possible to extract the capture (circle) and emission (square) times τc/e as shown in Fig. 2 and to find the points where τc = τe (marked green). These time constants do not follow an Arrhenius-like behavior, as can be seen in Fig. 3, where the τc = τe time constants are plotted for different temperatures.

Towards higher temperatures, the behavior becomes more Arrhenius-like, which would allow the extraction of the classical barrier, EB. However, it is expected that the extracted fit becomes steeper at higher temperatures and that the extracted barrier is still artificially low, due to the impact of tunneling.

These RTN measurements are in good agreement with previous BTI measurements on large-area devices, which show that charge trapping does not freeze-out towards cryogenic temperatures. This must be considered during the operation of CMOS devices at low temperatures since it affects the device degradation and the noise level.

Fig. 1: Sample RTN trace measured at cryogenic temperatures. Charge trapping does not freeze-out but becomes dominated by nuclear tunneling.

Fig. 2: Capture (circle) and emission (square) times for temperatures between 4K and 34K extracted from RTN measurements. The points τc = τe, where the trap level is equal to the Fermi level (green circles), is shifted to higher gate voltages and smaller time constants for higher temperatures.

Fig. 3: The time constants of τc = τe get shifted towards smaller numbers for increasing temperatures. However, the time constants do not follow an Arrhenius law towards 4K, which can be explained by the fact that nuclear tunneling becomes dominant.