|

|

||||

BiographyRittik Ghosh was born in 1998 in Calcutta (Now Kolkata), India. He received his bachelor’s degree in Electronics and Communication Engineering from Meghnad Saha Institute of Technology, India. He then received his Master’s degree in VLSI Design from Vellore Institute of Technology, India where his research focused on field-effect-transistor-based sensors using TCAD simulations. In October 2023, he joined the Institute for Microelectronics to pursue his PhD, where he will be working on gate stack engineering. |

|||||

Modeling the impact of border and interface traps on hysteresis in monolayer MoS2 FETs

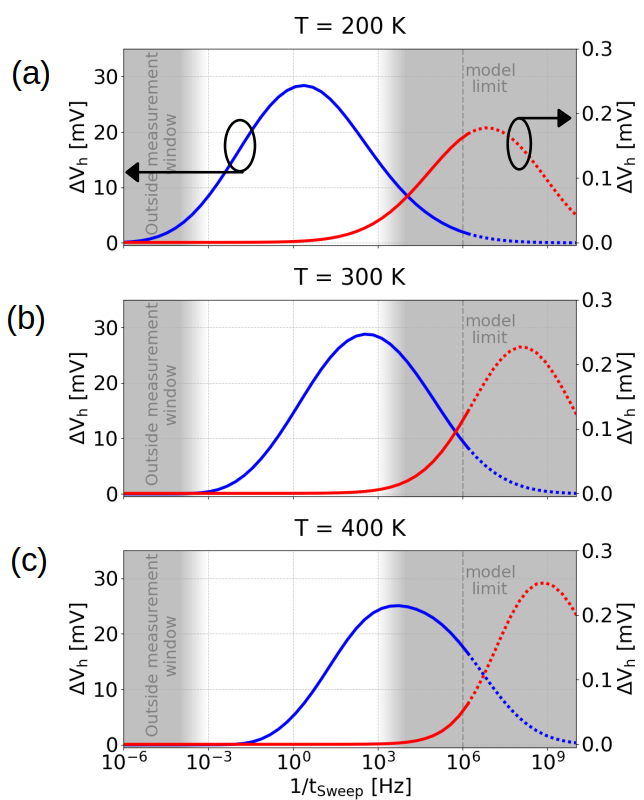

Molybdenum disulfide (MoS2) is widely studied as a promising channel material for atomically scaled transistors. In contrast to conventional silicon technology, monolayer (1-L) MoS2 offers a sizeable mobility at atomic thinness, ideally a clean surface, as well as direct band gap. While they show promising electrical and mechanical properties, their stability and reliability are to yet meet the rigorous standards set by silicon technologies. Due to material quality issues and unfavorable electronic band alignments, they exhibit threshold voltage hysteresis (ΔVh) in the up/down gate voltage sweep originating from charge carriers being trapped at localized trap states. However, ΔVh is sensitive to the spatial and energetic position of these traps within the oxide. In this context, traps can be classified into slow border and fast interface traps. Oxide traps located within a few nanometers from the channel are referred to as border traps. Their energy levels, relaxation energy and spatial distribution results in broad time constant distributions (τ). Particularly in amorphous insulators, these distributions can be exceptionally wide. On the other hand, traps in the channel have a narrow (τ) due to the more crystalline environment. In addition, τ are typically much smaller since the charge carriers are in very close vicinity to the traps. A comprehensive physics-based framework is needed to understand the impact of border and interface traps on the stability of 2D channel/oxide systems. In Fig. 1, we analyzed ΔVh dynamics over a wide range of sweep frequencies (1/tsweep ) for a closer understanding of the intricate trapping/detrapping dynamics. While it is commonly suggested that interface traps are too fast for observable ΔVh, our dynamic simulations show that degradation from some interface traps could be measured at lower temperatures.

Fig. 1: Extracted ΔVh vs. 1/tsweep for slower border (blue) and fast interface (red) traps at (a) 200 K (b) 300 K and (c) 400 K. Shaded regions show the 1/tsweep space outside the measurement window.