|

|

||||

BiographyJoël Kurzweil was born in Graz, Austria. He received his BSc and MSc degrees in Physics from the University of Vienna in 2017 and 2021, respectively. During his master’s thesis, he undertook analytical and numerical studies of turbulent gravitational phenomena related to the instability of Anti-de Sitter (AdS) space. After graduating with distinction, he worked in industry as a data scientist. He joined the Institute for Microelectronics in August 2023, where he is pursuing his doctoral degree. His current research focuses on investigating insulators for 2D materials for next-generation electronic devices, as well as on the modeling of reliability phenomena in 2D material-based field-effect transistors. |

|||||

Modeling the Interplay of Charge Trapping and Polarization Switching in Ferroelectric FETs

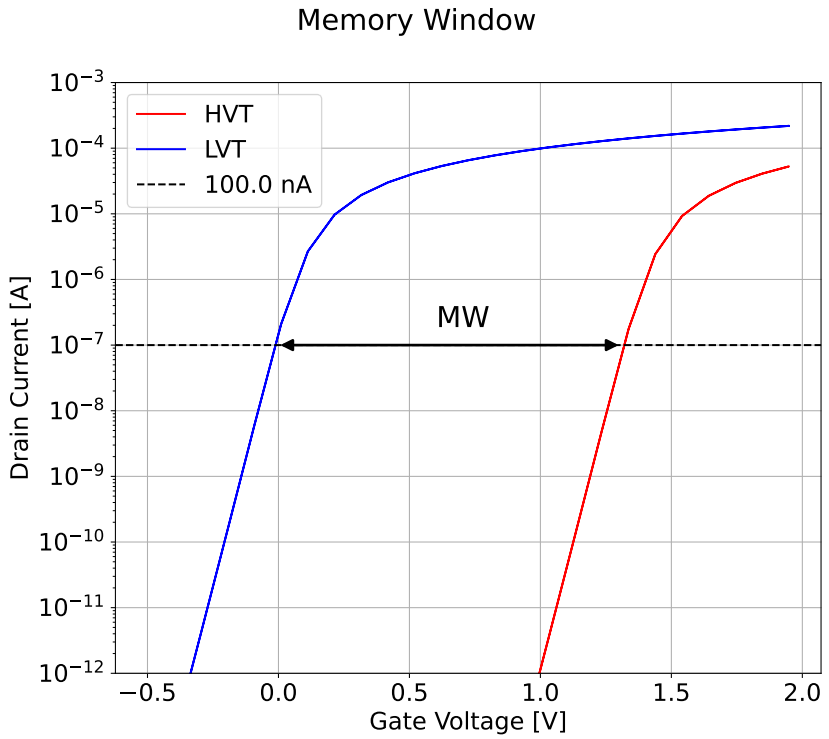

Ferroelectric field-effect transistors (FeFETs) are promising for non-volatile memory, logic-in-memory and neuromorphic computing. The ferroelectric layer in the gate stack enables storing information by applying a coercive voltage, which switches the polarization. The resulting remanent polarization alters the threshold voltage of the device, creating a low-threshold-voltage (LVT) state and a high-threshold-voltage (HVT) state. The two states can be distinguished by measuring the drain current. This so-called memory window of FeFET enables applications for non-volatile memory and is illustrated in Figure 1.

Several reliability phenomena are associated with FeFET operation. One important example is charge trapping, which leads to a voltage shift opposite to that of polarization switching. Consequently, the memory window of the FeFET shrinks and the LVT and HVT states become less distinguishable. Another reliability phenomenon associated with charge trapping is read-after-write delay. As a large voltage is applied during programming, charge trapping occurs. Trapped charges mask the true polarization state, making subsequent reading unreliable. Only after sufficient de-trapping has occurred can the state be reliably read, creating a delay between write and read operations.

Strategies to mitigate these effects invariably require a thorough understanding of the complex interplay of charge trapping and polarization switching during device operation. To this end, we employ simulations using our reliability simulator Comphy. Charge trapping rates are calculated using the non-radiative multi-phonon (NMP) theory, while polarization switching is modeled as a temperature-activated, nucleation-limited process based on Landau free energy theory. Due to the non-linear, coupled nature of these two processes, care must be taken to ensure numerical stability and accuracy. Therefore, both models are handled using a unified time-stepping solver, ensuring a self-consistent update of the electrostatics at each time step.

Fig. 1: Memory window of a FeFET illustrated via its transfer characteristic. Measuring the drain current at LVT enables reading the stored memory state.