|

(3.14) |

Many different failure mechanisms exist in semiconductor devices. For virtually all of them the root cause can be traced back to a relocation or displacement of material or charge. Atoms, ions, electrons, or holes are shifted from their designated to a harmful position. An isolated single movement usually does not cause a device failure. However, in highly down-scaled semiconductor devices, also single defect can lead to device failure. A major problem is the accumulation or depletion around an initially single defect, which consequently leads to further degradation of the device until parameters shift out of their specification or a severe failure occurs.

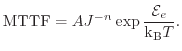

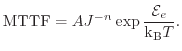

A representative failure mechanism based on transport of material is electromigration. In modern microelectronic devices, interconnect wires are required to carry high current densities. The positively charged metal ions in the interconnects are exposed to two counteracting forces. Due to the positive charge, ions experience a force towards the cathode. On the other hand, the mean velocity of the electrons is oriented towards the anode. A part of their moment is transmitted on to the atoms which also causes a force on the ions. This second force dominates at high current flow conditions which results in an effective force on ions oriented in the same direction as the electron flow. This effect is called electron wind [79]. The major part of the mass transport in interconnects follows grain boundaries and interfaces. This transport produces areas that suffer from material depletion and areas that suffer from material accumulation. The former ones are called voids and can grow until the interconnect is cut. Hence, the resistivity suddenly increases leading to a drop of the current. In areas of material accumulation, the additional atoms form hillocks. Most reliability considerations for electromigration have been done statistically. Commonly, the time until a massive resistivity increase appears. A frequently used estimation for the mean time-to-failure is expressed as [80]

|

(3.14) |

Another example of a reliability issue due to atomistic transport in

semiconductor devices is related to hydrogen transport. In device fabrication

hydrogen is especially important for the passivation of dangling bonds at

silicon/silicon-dioxide (Si/

![]() ) and polysilicon/silicon-dioxide

interfaces. Under stress conditions the hydrogen atoms can break free, leaving

back traps. This hydrogen release and possibly also the transport, is an

important failure mechanism in negative bias temperature instability (NBTI) and

hot-carrier degradation. The former will be briefly described in the next

section. The hot-carrier degradation and related modeling approaches for

hydrogen dissociation are discussed in Chapter 6.

) and polysilicon/silicon-dioxide

interfaces. Under stress conditions the hydrogen atoms can break free, leaving

back traps. This hydrogen release and possibly also the transport, is an

important failure mechanism in negative bias temperature instability (NBTI) and

hot-carrier degradation. The former will be briefly described in the next

section. The hot-carrier degradation and related modeling approaches for

hydrogen dissociation are discussed in Chapter 6.

Semiconductor oxides in electronic devices serve as isolation structures, as

gate dielectrics, and as protection against environmental harms. Especially the

native oxide of silicon, silicon dioxide, forms a stable and reliable interface

on top of silicon surfaces.

![]() is an insulator with a very high bandgap of

about 9eV [32] and with high resistivity, high breakdown voltage,

and an adequate permittivity [81]. It can be grown easily and in a

well-controlled manner with a low defect density. Considering this excellent

behavior in the fabrication process, the wide usage of silicon and its oxide

becomes evident. Green et al. [81] stated, that

is an insulator with a very high bandgap of

about 9eV [32] and with high resistivity, high breakdown voltage,

and an adequate permittivity [81]. It can be grown easily and in a

well-controlled manner with a low defect density. Considering this excellent

behavior in the fabrication process, the wide usage of silicon and its oxide

becomes evident. Green et al. [81] stated, that

![]() is with the

exception of its lower dielectric constant an ideal dielectric material.

is with the

exception of its lower dielectric constant an ideal dielectric material.

Due to the importance of

![]() and the Si/

and the Si/

![]() interface, it is obvious that

its reliability is of crucial significance and a considerable amount of

research has been related to that topic. Like all insulators,

interface, it is obvious that

its reliability is of crucial significance and a considerable amount of

research has been related to that topic. Like all insulators,

![]() loses its

insulating property at certain electric fields, where a breakdown occurs. The

maximum electric field a dielectric material can be used without severe damage

is called dielectric strength. The breakdown can occur because of intrinsic or

extrinsic phenomena, whereas the first ones are due to weaknesses of the

material itself and the latter ones are due to defects at the surface or in the

bulk of the oxide. Because of the extremely down-scaled semiconductor devices,

oxides have to resist enormous electric fields. The operation conditions get

close to the dielectric strength which increases the risk of wearout and its

consequences on device behavior.

loses its

insulating property at certain electric fields, where a breakdown occurs. The

maximum electric field a dielectric material can be used without severe damage

is called dielectric strength. The breakdown can occur because of intrinsic or

extrinsic phenomena, whereas the first ones are due to weaknesses of the

material itself and the latter ones are due to defects at the surface or in the

bulk of the oxide. Because of the extremely down-scaled semiconductor devices,

oxides have to resist enormous electric fields. The operation conditions get

close to the dielectric strength which increases the risk of wearout and its

consequences on device behavior.

During operation various mechanisms can lead to the creation and activation of oxide or interface defects acting as traps. As a consequence, the device degrades and parameters can drift out of their specification. Especially MOSFET devices are affected by oxide degradation. This wearout process during device operation can increase the gate leakage current which is called stress-induced leakage current (SILC) [82]. The ongoing degradation can further lead to breakdown, which is believed to be caused by a critical density of defects [83]. This time-dependent dielectric breakdown (TDDB) is a very important reliability issue [84]. It is still under discussion which physical processes are responsible for oxide deterioration, leading to SILC and TDDB, and in a further consequence how the are interrelated. The defects for the two processes are often assumed to be the same [85], however, there are also opinions against this connection, which claim that different processes and different defects are relevant for the two degradation mechanisms [86].

The monitoring of oxide degradation is based on measurements of different

phenomena. The interface trap creation is commonly assessed using capacity over

voltage and charge pumping experiments [87]. Measurement

techniques like constant-current stress (CCS) and constant-voltage stress (CVS)

are used to analyze the SILC and TDDB degradation. Changes of the voltage

during CCS or the current during CVS suggest that charge trapping in the oxide

leads to changes in the tunnel current density [88]. Another

widely discussed observation is the substrate hole current. It is measured in

n-channel MOS devices with source and drain grounded and a positive voltage

applied to the gate. The hole current which is some orders of magnitude below

the electron current seems to be correlated to the oxide deterioration

[89]. Measurements show that breakdown is observed after a certain

hole fluence through the oxide is reached. One explanation for this is the

Anode Hole Injection (AHI) [90]. Here, electrons tunnel from

the cathode into the anode and transfer their excess energy to holes. These

holes gain high energy and can be injected back into the oxide. With a given

probability they can cause the observed bulk hole current. In this AHI model,

these injected holes create the oxide damage. Estimations of the time to

breakdown (

![]() ) using the AHI model lead to a relation where the logarithm of

) using the AHI model lead to a relation where the logarithm of

![]() depends linearly on the reciprocal oxide field and is therefore called

the `1/E'-model [91]. Early empirical models, however,

suggested a linear dependence of the logarithm of

depends linearly on the reciprocal oxide field and is therefore called

the `1/E'-model [91]. Early empirical models, however,

suggested a linear dependence of the logarithm of

![]() on the electric

field. These models are therefore called the `E'-model. Several physical

explanations have been suggested for this phenomenon, however, none of them

correlates the degradation with the electron tunnel current

[91]. One of the oldest `E'-models, the thermochemical model

[92], for example, gives a physical explanation based on Si-Si

bond breaking in

on the electric

field. These models are therefore called the `E'-model. Several physical

explanations have been suggested for this phenomenon, however, none of them

correlates the degradation with the electron tunnel current

[91]. One of the oldest `E'-models, the thermochemical model

[92], for example, gives a physical explanation based on Si-Si

bond breaking in

![]() . Interestingly, both, the `E'- and the `1/E'-model

allow to fit TDDB data rather well over limited field ranges used in

acceleration tests [92]. Obviously, the extrapolations to low

electric fields give very different lifetime projections. A wide range of

measurements and especially long-term measurements close to normal operating

fields of approximately 5MV/cm are required to clearly distinguish between

the models [92]. However, for low electric fields

. Interestingly, both, the `E'- and the `1/E'-model

allow to fit TDDB data rather well over limited field ranges used in

acceleration tests [92]. Obviously, the extrapolations to low

electric fields give very different lifetime projections. A wide range of

measurements and especially long-term measurements close to normal operating

fields of approximately 5MV/cm are required to clearly distinguish between

the models [92]. However, for low electric fields

![]() increases drastically which makes measurements nearly impossible.

increases drastically which makes measurements nearly impossible.

Breakdown mechanisms due to the accumulation of oxide defects are often explained using the percolation model [70]. Generated electron traps are believed to form a breakdown path from the anode to the cathode. In this model, the traps are represented using spheres, which are randomly placed in the oxide volume (see Fig. 3.7).

![\includegraphics[width=0.49\textwidth]{figures/percolation}](img131.png)

|

If two spheres overlap, conduction is possible between them. An oxide is broken

if a single breakdown path is generated [93]. In oxides thicker

than approximately ![]() nm the heat generated by the localized current

immediately propagates and results in thermal damage. This leads to a highly

conductive short across the oxide, which is called hard breakdown

[81]. However, in thinner oxides a non-destructive or soft

breakdown is observed [94]. Here, a more resistive current path is

created. Therefore, no thermally induced lateral extension of the percolation

path is triggered [81]. Both, hard and soft breakdown can be

described using the percolation model [95]. Good agreement is

found by comparing this model with measurements. By partitioning the oxide

capacity into a row of small independent capacitances, one can empirically

assume that the failure of a single component leads to the failure of the whole

oxide. Therefore, the breakdown mechanism can be explained by the weakest-link

theory, which can be fit using the Weibull distribution [70,95] (see Fig. 3.5).

nm the heat generated by the localized current

immediately propagates and results in thermal damage. This leads to a highly

conductive short across the oxide, which is called hard breakdown

[81]. However, in thinner oxides a non-destructive or soft

breakdown is observed [94]. Here, a more resistive current path is

created. Therefore, no thermally induced lateral extension of the percolation

path is triggered [81]. Both, hard and soft breakdown can be

described using the percolation model [95]. Good agreement is

found by comparing this model with measurements. By partitioning the oxide

capacity into a row of small independent capacitances, one can empirically

assume that the failure of a single component leads to the failure of the whole

oxide. Therefore, the breakdown mechanism can be explained by the weakest-link

theory, which can be fit using the Weibull distribution [70,95] (see Fig. 3.5).

A recently and heavily discussed reliability topic is the negative bias temperature instability (NBTI). It can be observed by applying negative voltages to the gate of a MOSFET with all other contacts connected to ground. Since negative gate voltages are more common in p-MOSFETs, p-type transistors are more susceptible than the n-types. The degradation leads to a shift of the threshold voltage, a change in the subthreshold slope, and a reduction of the mobility. Its underlying mechanism becomes stronger at elevated temperatures and high voltages. In contrast to the other degradation mechanisms discussed so far, a relaxation can be observed as soon as NBTI stress ends. However, a part of the damage remains permanent or at least relaxes only very slowly [96].

NBTI has already been known for forty years and has long been explained and

modeled by the reaction-diffusion (RD) theory [97]. In this model,

the de-passivation of

![]() centers is assumed as the main degradation

mechanism NBTI.

centers is assumed as the main degradation

mechanism NBTI.

![]() centers are dangling bonds at the Si/

centers are dangling bonds at the Si/

![]() interface. During the production of the devices, hydrogen is used to passivate

these bonds and to make them electrically inactive. During stress, this

hydrogen is released causing the device degradation. In the RD model, the

de-passivated hydrogen is assumed to diffuse away from the interface through

the oxide leaving back dangling bonds at the interface. The degradation is

therefore diffusion dominated. In the relaxation phase hydrogen near the

interface can passivate the interface again. Hence, the diffusion process of

hydrogen plays an important role in the RD model. Various NBTI stress

measurements have been fitted successfully with this method. However, modeling

of the relaxation phase shows considerable deviations between measurements and

simulations. The model predicts a retarded relaxation which is not found in

measurement data. Subsequently the tendency changes insofar that the prediction

relaxes too fast. During NBTI stress the forward and the backward reactions

contribute to the degradation. Considering that the relaxation alone is

evidently not described correctly, the correctness of the RD model is

questionable. Hence, extensions to the RD approach have been suggested, that

assumed a dispersive hydrogen transport in the oxide

[98,99]. But this and other variations do not seem to fit

satisfyingly. Additionally, many published approaches seem to be based on

tainted measurement data and it shows that it is very important to consider the

measurement techniques used to quantify the degradation of device parameters

[100]. This is caused by the fact that measurements are commonly

performed by gate voltage sweeps and subsequent current measurements to

estimate the threshold voltage. This requires an interruption of the stress

cycle and relaxation immediately takes place. Since the time constants for

relaxation are very small, measurement results can change significantly with

the measurement delay.

interface. During the production of the devices, hydrogen is used to passivate

these bonds and to make them electrically inactive. During stress, this

hydrogen is released causing the device degradation. In the RD model, the

de-passivated hydrogen is assumed to diffuse away from the interface through

the oxide leaving back dangling bonds at the interface. The degradation is

therefore diffusion dominated. In the relaxation phase hydrogen near the

interface can passivate the interface again. Hence, the diffusion process of

hydrogen plays an important role in the RD model. Various NBTI stress

measurements have been fitted successfully with this method. However, modeling

of the relaxation phase shows considerable deviations between measurements and

simulations. The model predicts a retarded relaxation which is not found in

measurement data. Subsequently the tendency changes insofar that the prediction

relaxes too fast. During NBTI stress the forward and the backward reactions

contribute to the degradation. Considering that the relaxation alone is

evidently not described correctly, the correctness of the RD model is

questionable. Hence, extensions to the RD approach have been suggested, that

assumed a dispersive hydrogen transport in the oxide

[98,99]. But this and other variations do not seem to fit

satisfyingly. Additionally, many published approaches seem to be based on

tainted measurement data and it shows that it is very important to consider the

measurement techniques used to quantify the degradation of device parameters

[100]. This is caused by the fact that measurements are commonly

performed by gate voltage sweeps and subsequent current measurements to

estimate the threshold voltage. This requires an interruption of the stress

cycle and relaxation immediately takes place. Since the time constants for

relaxation are very small, measurement results can change significantly with

the measurement delay.

Recently an advanced physically based NBTI modeling approach has been proposed

by Grasser et al. [101]. In this work, the degradation is described

using two stages. The key ingredient in this model is the near-interfacial

oxygen vacancy in the amorphous

![]() gate dielectric. Holes from the silicon

are captured by this defect, breaking up the Si-Si bond (state 1) which creates

a positively charged

gate dielectric. Holes from the silicon

are captured by this defect, breaking up the Si-Si bond (state 1) which creates

a positively charged ![]() center (see the transition from state 1 to 2 in

Fig. 3.8).

center (see the transition from state 1 to 2 in

Fig. 3.8).

![\includegraphics[width=0.8\textwidth]{figures/Lelis3Couple}](img135.png)

|

On hole emission, i.e. on electron capture, the defect is neutralized (state 3)

but does not relax immediately to its initial configuration. Now, the neutral

![]() center can recapture a hole returning to the charged state 2 or the

structure relaxes back to its precursor configuration. The hole capture and

emission between state 2 and 3 can be very efficient. Therefore, such a kind of

defect is called switching trap. The states 1, 2, and 3 represent the first

stage in this two-stage model. The second stage of the degradation process is

initiated by the dangling bond of the positively charged Si atom of the

center can recapture a hole returning to the charged state 2 or the

structure relaxes back to its precursor configuration. The hole capture and

emission between state 2 and 3 can be very efficient. Therefore, such a kind of

defect is called switching trap. The states 1, 2, and 3 represent the first

stage in this two-stage model. The second stage of the degradation process is

initiated by the dangling bond of the positively charged Si atom of the ![]() center. It attracts a hydrogen atom, which comes originally from the passivated

interface, where it leaves back a positive interface charge. Repassivation of

those dangling bonds requires free hydrogen atoms. For a full recovery, the

defect has to pass through state 2 and 3. Hence, the full relaxation is slow,

especially from stage 2. At least a part of those traps seems to remain

permanent. The possible transitions between the four states of this model are

illustrated in Fig. 3.8. The simulation results using this model in

comparison with measurement data of devices with different technologies and

geometries deliver very promising results

[101,102]. Also the fast and the slow/permanent

degradation observed in measurements are described very well using this

two-stage model [101,102].

center. It attracts a hydrogen atom, which comes originally from the passivated

interface, where it leaves back a positive interface charge. Repassivation of

those dangling bonds requires free hydrogen atoms. For a full recovery, the

defect has to pass through state 2 and 3. Hence, the full relaxation is slow,

especially from stage 2. At least a part of those traps seems to remain

permanent. The possible transitions between the four states of this model are

illustrated in Fig. 3.8. The simulation results using this model in

comparison with measurement data of devices with different technologies and

geometries deliver very promising results

[101,102]. Also the fast and the slow/permanent

degradation observed in measurements are described very well using this

two-stage model [101,102].

Another reliability concern comes from hot-carriers in the channel. Due to the high electric fields along the channel in MOS transistors, carriers gain a considerable amount of energy. This is especially true at the drain end of the channel. These carriers can break silicon-hydrogen bonds at the interface which generates interface traps. Hence, charges can get trapped and consequently change the device parameters. This degradation mechanism is essential for the operation of high-voltage devices and is discussed in detail in Chapter 6.

High energetic carriers are not only responsible for interface reliability. Another hot-carrier process, impact-ionization is also of special interest for reliability engineering. It is especially pronounced at the drain end of the channel region in MOSFET devices. The cascaded impact-ionization carrier generation increases the carrier concentrations, the current densities, and finally leads to avalanche breakdown. Devices have to be designed carefully to avoid breakdown under all operating conditions within the specifications [103,104]. In some applications the breakdown conditions initiated by, for example, electrostatic discharge or power supply peaks, cannot be fully prevented. The breakdown can lead to latch-up, snap-back, or immediate device failure with all consequential reliability issues. The topic of modeling and simulation of impact-ionization is an important part of this thesis, addressed in Chapter 5.

MOSFET transistors and especially CMOS (Complementary MOS) integrated circuits inherently suffer under the high susceptibility of the gate oxides to electrostatic discharge (ESD). In integrated circuits ESD stress leads to gate oxide or thermal junction breakdown [105,106,107]. The risk of ESD shocks is not only present before and during assembly, but also prior to the packaging and bonding of the die. On the semiconductor wafer, for example, etching, testing, and dicing can also introduce ESD [106,108]. The risk of damage obviously increases with the ongoing shrinking of the gate oxide. Since ESD events cannot be fully avoided during the product life-cycle, the most practical approach is the integration of protection circuits against ESD threats directly in the microelectronic structures [8].

Most work in reliability research concerning ESD is related to the optimization

of existing protection structures and to the development of new structures

[109,110]. The procedure of transferring ESD protection devices

from one technology node to the next one is not straightforward. Thereby

changes in the dimensions, the introduction of buried oxides, and different EPI

(epitaxy layer) thicknesses introduce new uncertainties. Various structures are

used as protection circuits. The first protection structures in the beginning

of CMOS technology, required serial resistors. Hence, the overall performance

of the integrated circuit was reduced. However, optimal designed ESD devices

are electrically invisible during functional operation, but become active

quickly, if needed, to keep the voltage low and to dissipate high currents. To

accomplish this, new devices were introduced, one of them is the silicon

controlled rectifier (SCR) based on ![]() -structures [111]. This

type of device is hard to calibrate and small process variations can lead to

significant changes in the turn-on voltage. Nowadays, a very common structure

is the gate-grounded NMOS transistor (ggNMOS), which makes use of the parasitic

bipolar transistor [111]. To minimize the fabrication costs, the

same technology as for the integrated circuit itself is used. The ggNMOS is

actually built like a common MOSFET, only the dimensions have to be adapted

(see Fig. 3.9).

-structures [111]. This

type of device is hard to calibrate and small process variations can lead to

significant changes in the turn-on voltage. Nowadays, a very common structure

is the gate-grounded NMOS transistor (ggNMOS), which makes use of the parasitic

bipolar transistor [111]. To minimize the fabrication costs, the

same technology as for the integrated circuit itself is used. The ggNMOS is

actually built like a common MOSFET, only the dimensions have to be adapted

(see Fig. 3.9).

Source and gate are grounded and the drain is connected to the external input

pin that needs to be clamped down to a low voltage. On ESD events, the rising

voltage generates an increased reverse current leading to impact-ionization near the drain

region. Eventually, the drain junction breaks down yielding a high carrier

generation rate. Electrons are driven towards the drain and holes are driven to

the ![]() area (actually the bulk contact). This hole current flow under the

area (actually the bulk contact). This hole current flow under the

![]() source area increases the electrostatic potential in the bulk so that the

source-bulk junction gets forward biased and electrons are injected into the

bulk. The increased electron current leads to a positive feedback and to a

further increased impact-ionization generation. Hence, the resistance between source and

drain drops. In the I/V characteristics this gives a negative differential

resistance (see Fig. 3.10). The lower the voltage drops, the

lower is the dissipated heat during ESD.

source area increases the electrostatic potential in the bulk so that the

source-bulk junction gets forward biased and electrons are injected into the

bulk. The increased electron current leads to a positive feedback and to a

further increased impact-ionization generation. Hence, the resistance between source and

drain drops. In the I/V characteristics this gives a negative differential

resistance (see Fig. 3.10). The lower the voltage drops, the

lower is the dissipated heat during ESD.

![\includegraphics[width=0.6\textwidth]{figures/snapback_dummy}](img140.png)

|

Structures like the ggNMOS are used to protect integrated circuits efficiently against ESD events. Especially measures to prevent damage due to electrostatic discharge events caused by people touching the device are carefully implemented. This stress event is also well modeled by the human body model (HBM).

One of the most often considered environmental influences is the temperature [112,113,114]. High temperatures in silicon devices lead to changes of the device parameters and to accelerated device degradation [115,116,117]. It has to be ensured that cooling is properly designed for all environmental temperatures that can be expected [118]. Since most degradation mechanisms are thermally activated, elevated temperatures during usage decrease the lifetime of the device. A proper buffer in the design is needed to ensure design goals.

Other environmental impacts include radiation-induced degradation which can lead to displacement or ionization effects [63]. Also mechanical, physical, as well as chemical influences may penetrate the protection layers of integrated circuits and eventually degrade the device or open up paths to the semiconductor surface [63]. By such a path, foreign atoms, or simply moisture, can react with the metalization [71]. Therefore, a proper coating and packaging is very important for protection against environmental impacts [119].