|

|

||||

BiographyAlexander Makarov was born in Volgograd, Russia, in 1985. He studied information technology at the Volgograd State Technical University, where he received the BSc degree in 2006 and MSc degree in 2008. He joined the Institute for Microelectronics in October 2009 and has obtained the doctoral degree in March 2014. He is currently employed as a post-doc researcher. His scientific interests include Monte-Carlo simulations and nonvolatile memory device modeling. |

|||||

Correlated Time-0 and Hot-Carrier Stress Induced FinFET Parameter Variabilities: A Modeling Approach

One of the main problems plaguing the performance of modern ultra-scaled field-effect transistors (FETs) is variability, which has multiple sources: random dopants (RDs), perturbation in material properties, oxide thickness fluctuations, etc. This variability exists even in pristine devices and therefore is named "time-0 variability". In a very similar manner, build-up of defects during stress is a stochastic process and therefore degradation in ultra-scaled devices should be described statistically as a time-dependent variability.

As for hot-carrier degradation (HCD), it has repeatedly been declared to be the most detrimental reliability concern in ultra-scaled FETs. Although HC-induced variability has been the subject of experimental and modeling studies, to the best of our knowledge there is a limited number of publications devoted to the study of the correlation between time-0 and HC stress induced transistor parameter distributions, and no simulation studies of this correlation have been performed so far.

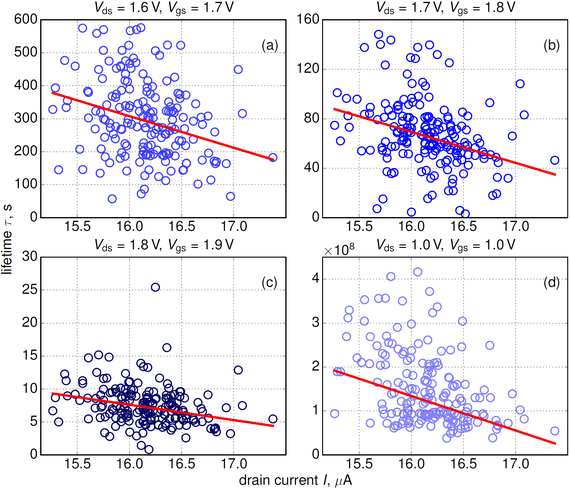

We performed the first theoretical study of the correlation between time-0 values of the linear and saturation drain currents in n-channel FinFETs and relative drain current changes induced by HC stress. To achieve this goal, we employed our statistical simulation model for HCD by first generating an ensemble of 200 instantiations of the n-channel FinFET with unique random dopant configurations, and then, we calculated time-0 drain currents and their normalized changes with stress time. Finally, device lifetimes were extracted. Then, current changes were plotted versus time-0 currents, and the robust linear fit employing the Kendall rank correlation coefficient allowed us to identify correlation between these two variates.

Our correlation analysis has shown that FinFETs with higher time-0 currents degrade faster and therefore have larger current changes and shorter device lifetimes (Fig. 1). This qualitative behavior holds true for both linear and saturation drain currents (and corresponding lifetimes) and is consistent with similar trends previously reported for bias temperature instability. Furthermore, we have shown that the impact of random traps does not changes all the aforementioned tendencies.

Fig. 1: Extracted dependencies of device lifetime on drain current for all stress conditions. To evaluate device lifetime values, we used a ∆Id,lin = 0.1 criterion.