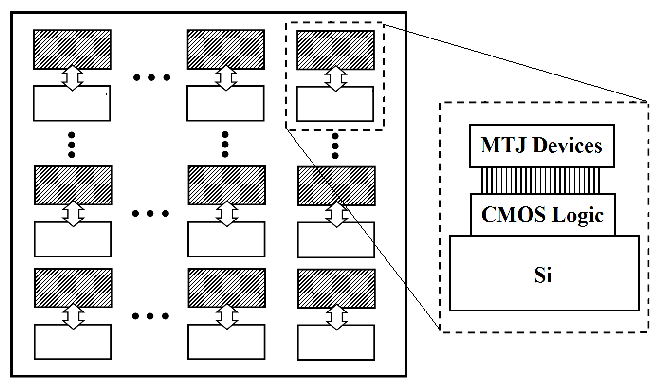

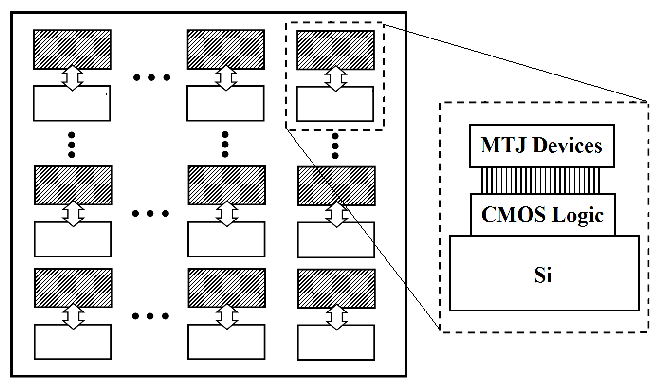

| Figure 4.1.: | Logic-in-memory architecture and the three-dimensional structure of the magnetic logic circuits. |

Spintronics emerged with the discovery of the giant magnetoresistance (GMR) of magnetic multilayers in 1980s [30, 31] which brought the Nobel prize to Fert and Grünberg in 2007 [24]. Spintronic devices exploit the electrons’ spin degree of freedom to provide novel functional properties. Spin dependent tunneling in magnetoresistive devices with a tunnel barrier junction structure shows a higher resistance as well as a higher resistance modulation compared to other magnetoresistive devices [32]. Therefore, magnetic tunnel junctions (MTJs) are very favorable for magnetoresistive random-access memory (MRAM) technology [22, 23]. Despite the advantages of CMOS compatibility, high speed, and unlimited endurance, the first generation of MTJs [41, 42, 43], which utilized Oersted fields for the magnetization switching, was unfavorable in terms of scalability and energy consumption. By using the spin-transfer torque [44, 45] switching technique [46, 47], the second generation of the MTJ (STT-MTJ) [48, ?, 49] eliminates the need for current lines adjacent to memory cells, which were required previously for generating a switching field. Thus, by using the same lines for reading and writing operations, the STT-MTJ is more scalable and allows for smaller switching energies [22, 23].

As one of the most promising non-volatile storage technologies, STT-MTJ is also attractive for non-volatile logic applications to overcome scaling obstacles of CMOS logic circuits like the leakage power issue [37, 51, 52, 53, 54, 55, 56, 57, 58, 59]. By using the STT-MTJ technology the effective area and interconnection delay can be reduced due to an easy three-dimensional integration of the MTJs on top of the CMOS layers (Fig. 4.1). However, in hybrid CMOS/MTJ logic circuits the MTJs are used only as ancillary devices, which store solely the computation results. Therefore, sensing amplifiers [168] are required to read the data at each logic stage and to provide the next stage with an appropriate voltage or current signal as input. This increases the device count, delay, and power consumption. In addition, the generalization to large-scale logic systems is problematic. The use of spintronic devices as the main computing elements (logic gates) in novel computational architectures is a promising solution to address the above-described issues. The focus of this chapter is stateful logic gates which employ spintronic devices as logic gates.

| Figure 4.1.: | Logic-in-memory architecture and the three-dimensional structure of the magnetic logic circuits. |